Mengurangi Panjang Siklus Desain dalam SoC yang Didesain Bersama dengan Renode

Dalam artikel ini, kami menjelaskan bagaimana penggunaan simulator fungsional open-source seperti Antmicro's Renode dapat menjadi bagian integral dari upaya desain bersama perangkat keras-perangkat lunak .

Dalam artikel ini, kami menjelaskan bagaimana penggunaan simulator fungsional open-source seperti Antmicro's Renode dapat menjadi bagian integral dari upaya desain bersama perangkat keras-perangkat lunak.

Karena pasar menuntut lebih banyak dari sistem tertanam mereka, SoC generasi berikutnya menjadi lebih kompleks, yang mengarah ke siklus desain yang lebih panjang dan kenaikan biaya, menurut Semico Research.

Kenyataan yang membuat frustrasi para pembuat perangkat adalah bahwa satu-satunya cara untuk menghadirkan fitur-fitur baru dan inovatif, keamanan yang lebih besar, dan kinerja yang lebih baik yang diminta oleh pelanggan mereka, adalah dengan terlibat dalam desain bersama "seluruh tumpukan", perangkat keras yang berkembang, firmware, runtime (OS), dan toolchain pengembangan secara bersamaan. Dengan melakukan hal itu, tim perangkat keras dan perangkat lunak dapat mengatasi kompromi kompleks di sekitar tumpukan untuk menerapkan fungsionalitas dan pengoptimalan.

Sayangnya, desain bersama sering kali menjadi pendorong utama perpanjangan siklus desain—dan oleh karena itu, biaya—ketika alat simulasi yang tepat tidak tersedia.

Dalam artikel ini, kami menjelaskan bagaimana penggunaan simulator fungsional open-source seperti Antmicro's Renode dapat menjadi bagian integral dari upaya desain bersama perangkat keras-perangkat lunak. Selanjutnya, kami akan menunjukkan kepada Anda contoh bagaimana pengguna Renode dapat memanfaatkan alat ini untuk secara drastis mengurangi panjang siklus desain mereka, menyediakan cara yang sederhana dan efektif bagi pelanggan untuk mengevaluasi solusi mereka, dan untuk mulai mengadaptasi jaminan perangkat lunak secara paralel dengan upaya integrasi perangkat keras.

Di mana Simulator Perangkat Lunak Bisa Gagal

Pentingnya memilih alat simulasi yang tepat paling baik diilustrasikan dalam kasus Dover Microsystems.

Teknologi CoreGuard® Dover adalah satu-satunya solusi yang mencegah eksploitasi kerentanan perangkat lunak dan memungkinkan prosesor untuk mempertahankan diri dari serangan berbasis jaringan. Dover mampu mencapai ini melalui delapan tahun penelitian dan pengembangan—pertama sebagai pemain terbesar di DARPA Crash Program, dan kemudian di Draper Labs—yang menghasilkan solusi hibrid perangkat keras/lunak yang unik untuk sistem tertanam.

Solusi hybrid ini membutuhkan integrasi yang erat antara komponen perangkat keras dan perangkat lunak. CoreGuard silicon IP adalah prosesor penjaga yang bertindak sebagai pengawal, melindungi sistem tertanam dari serangan dunia maya. Ini memantau setiap instruksi yang dijalankan oleh prosesor host untuk memastikan bahwa itu mematuhi seperangkat aturan keamanan, keselamatan, dan privasi yang ditentukan yang disebut kebijakan mikro—komponen perangkat lunak CoreGuard. Jika sebuah instruksi melanggar aturan yang ada, CoreGuard menghentikannya dari eksekusi sebelum kerusakan dapat dilakukan.

Untuk mencapai ini, CoreGuard perlu mengikuti eksekusi prosesor host. Artinya, rata-rata, ia harus dapat menghentikan (menyetujui melalui kebijakan mikro) instruksi pada tingkat yang sama dengan prosesor host yang dilindungi. CoreGuard juga diharapkan meminimalkan jumlah memori yang diperlukan untuk manajemen metadata.

Oleh karena itu, memenuhi tuntutan kinerja, daya, dan area memerlukan interaksi pengoptimalan yang kompleks baik dari lapisan perangkat keras maupun perangkat lunak.

Tim perangkat keras di Dover menggunakan proses dan rantai alat berbasis SystemVerilog standar. Prototipe awal sistem CoreGuard dibangun di atas SoC berbasis RISC-V. Karena CoreGuard memiliki komponen perangkat lunak yang substansial selain IP perangkat keras, penting bagi tim perangkat lunak untuk dapat memulai dengan baik sebelum prototipe perangkat keras tersedia.

Tim perangkat lunak di Dover awalnya menggunakan simulator perangkat lunak ISA Spike RISC-V yang tersedia dari repo GitHub RISC-V. Mereka mengalami dua masalah mendasarkan pengembangan komersial CoreGuard mereka di sekitar Spike:

- Spike tidak menyediakan periferal yang realistis; yaitu, Spike adalah simulator ISA, bukan simulator SoC. Tim Dover mulai menambahkan periferal seperti UART dan penyimpanan persisten ke Spike, dan ini membutuhkan banyak pekerjaan.

- Spike, menurut definisi, spesifik untuk RISC-V, tetapi pelanggan awal Dover Microsystems adalah berbasis RISC-V dan Arm.

Kekurangan ini menyoroti kebutuhan Dover akan simulator multi-arsitektur yang fleksibel dengan konsep model periferal yang akan digunakan sebagai pengganti Spike.

Bagaimana Renode Mengatasi Kebutuhan Desain Bersama yang Penting

Menghadapi tantangan rekayasa desain bersama perangkat keras/perangkat lunak heterogen serupa yang berasal dari pekerjaan dengan softcore sumber terbuka, perangkat lunak awal untuk platform komputasi terdepan, SoC FPGA, dan arsitektur CPU yang muncul seperti RISC-V, Antmicro—sebuah sumber terbuka yang berfokus penyedia teknologi dan layanan—mengembangkan kerangka kerja simulasi fleksibel yang disebut Renode.

Renode adalah kerangka kerja simulasi modular hierarkis yang ditujukan untuk menjalankan firmware produksi nyata (yaitu, tidak dimodifikasi) dalam berbagai sistem yang kompleks, termasuk multi-node yang saling terhubung, multi-arsitektur, heterogen, tingkat MCU, dan sistem berkemampuan Linux.

Untuk mengatasi berbagai tingkat kerumitan ini, Renode dibangun di sekitar gagasan abstraksi yang kuat dan mengadopsi pendekatan modular berorientasi objek untuk simulasi sistem. Core dan periferal dilihat sebagai blok penyusun yang dapat dihubungkan melalui antarmuka dalam konfigurasi yang berbeda, yang mencerminkan bagaimana SoC yang sebenarnya dibangun.

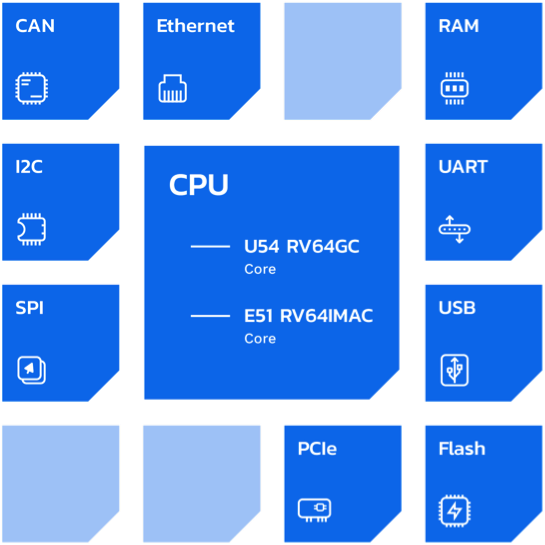

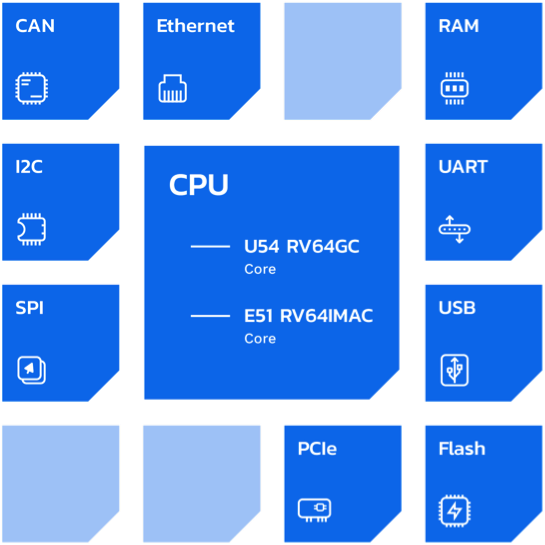

Gambar 1. Contoh simulasi RISC-V SoC.

Gambar 1 menunjukkan contoh simulasi RISC-V SoC. Setiap blok penyusun, termasuk CPU, memiliki seperangkat properti dan API yang dapat digunakan untuk membangun model simulasi seluruh SoC. Demikian pula, node tunggal dapat digabungkan lebih lanjut ke dalam sistem multi-node menggunakan koneksi nirkabel dan kabel tervirtualisasi (6LoWPAN, UART, Ethernet dll). Semua ini tidak memerlukan perubahan pada basis kode Renode tetapi dilakukan melalui konfigurasi dan skrip, mengurangi kurva pembelajaran dan membatasi fragmentasi basis kode.

Sifat kerangka kerja Renode yang fleksibel, ketersediaan sumber terbuka, dan adanya dukungan komersial yang diberikan oleh pembuatnya memudahkan Dover untuk terlebih dahulu membangun implementasi prototipe dari alur kerja yang diinginkan dan kemudian mengontrak Antmicro untuk mengimplementasikannya (dan merilisnya ke domain sumber) fungsionalitas yang membuat Renode lebih cocok untuk kasus penggunaannya, seperti eksekusi per-instruksi.

Khususnya, dengan menggunakan Renode, teknisi Dover kini dapat:

- Beralih antara upaya integrasi berbasis Arm dan RISC-V menggunakan penyiapan yang sama.

- Prototipe SoC (baik referensi/minimal dan yang ditentukan pelanggan) pada tingkat detail/fidelitas yang berbeda.

Buat model spesifikasi arsitektur perangkat keras dari grup perangkat keras Dover, lalu tulis dan uji firmware terhadap model tersebut, semuanya saat perangkat keras sedang dalam pengembangan.

Bagaimana Renode Mengurangi Siklus Desain Dover Secara Signifikan

Teknologi CoreGuard Dover adalah produk keamanan siber hibrida di mana desain perangkat keras dan perangkat lunak berkembang. Oleh karena itu, penting bagi proses pengembangan Dover untuk memungkinkan pengembangan dan pengujian paralel baik perangkat keras maupun perangkat lunak.

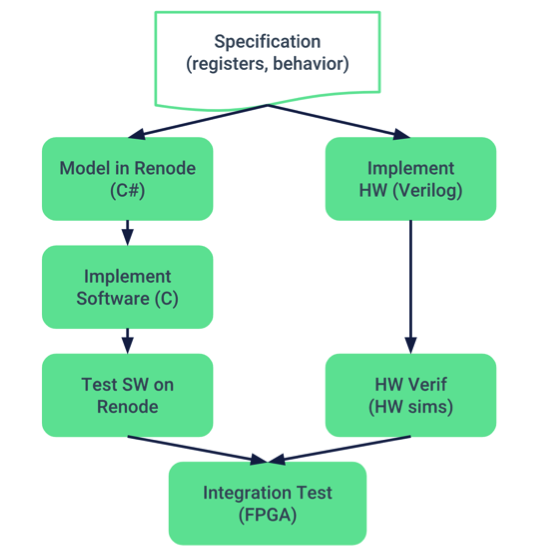

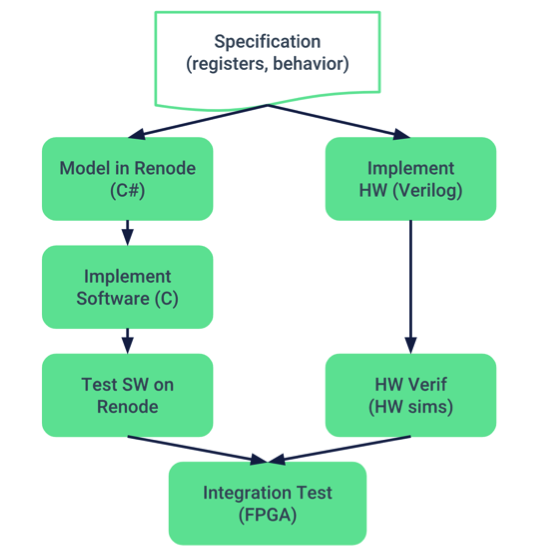

Gambar 2. Proses pengembangan yang digunakan oleh Dover.

Dover menggunakan proses pengembangan yang diuraikan pada Gambar 2. Tim perangkat keras dan perangkat lunak berkolaborasi pada antarmuka perangkat keras (yang tentu saja akan terus berkembang). Saat tim perangkat keras mulai menerapkan blok di SystemVerilog, tim perangkat lunak membuat model blok baru di C#, bahasa asli yang mendasari Renode. Tim perangkat lunak kemudian dapat menulis firmware yang berkomunikasi dengan antarmuka perangkat keras baru, dan menguji perangkat lunak tersebut di bawah simulasi Renode. Akhirnya, perangkat lunak dijalankan pada emulator FPGA.

Proses pengembangan ini, yang dimungkinkan oleh Renode, telah membantu Dover mengoptimalkan simulasi “low fidelity” dan “high fidelity”.

Sementara simulasi “low fidelity” ini mengabstraksi semua logika perangkat keras CoreGuard, Dover masih menganggap penyiapan ini berguna dalam konteks berikut:

- Debug Kebijakan Mikro: Saat kebijakan mikro CoreGuard baru sedang dikembangkan, kami ingin melakukan iterasi dengan cepat terhadap berbagai pengujian perangkat lunak, untuk memeriksa perilaku.

- Demo dan Pratinjau Pelanggan: Untuk demonstrasi CoreGuard, simulasi perangkat lunak murni seringkali cukup untuk mendidik calon pelanggan tentang kemampuan CoreGuard® dan untuk merangsang minat dalam diskusi lebih lanjut. Lebih jauh lagi, Dover akan sering mengirimkan "SDK" kepada pelanggan yang terdiri dari simulator "kesempurnaan rendah" ini dengan beberapa kebijakan mikro yang telah ditentukan, agar pelanggan dapat "bermain" dengan CoreGuard, termasuk kemungkinan menjalankan kebijakan mikro CoreGuard terhadap perangkat lunak pelanggan.

Dalam simulasi “high fidelity”, yang mereplikasi model perangkat keras yang lebih akurat, tim teknik Dover telah mampu mengenali sejumlah manfaat dengan Renode, termasuk:

- Mengintegrasikan dengan berbagai format biner non-ELF (mis., scatter-load) yang digunakan oleh ROM boot perangkat keras.

- Mengembangkan dan menguji proses boot; menyalin dari flash ke RAM, menginisialisasi perangkat.

- Men-debug lalu lintas bus menggunakan instrumentasi Renode.

- Periferal debugging (UART, PIC, antarmuka CoreGuard itu sendiri) dengan instrumentasi.

- Bermain dengan peta memori.

- Menerapkan firmware video HDMI, sebelum perangkat keras berfungsi.

Seperti yang ditunjukkan sebelumnya, ada beberapa kendala kinerja dan area yang menantang yang diterapkan oleh solusi generasi berikutnya seperti CoreGuard pada tim desain SoC selama implementasi.

Untuk meningkatkan kinerja dan mengurangi penggunaan memori, ada berbagai macam pengoptimalan yang perlu dilakukan, yang seringkali melewati batas perangkat keras/perangkat lunak.

Sangat penting bagi tim desain untuk dapat mengeksplorasi berbagai kemungkinan teknik dan pengorbanan bersama perangkat keras/perangkat lunak, tanpa "proses pengembangan perangkat keras-pertama-kemudian-perangkat lunak" serial yang besar. Simulator fungsional perangkat lunak yang fleksibel seperti Renode memungkinkan para insinyur Dover berkolaborasi di seluruh perangkat keras-perangkat lunak untuk menemukan keseimbangan optimal antara kompleksitas perangkat keras dan perangkat lunak, menjadikannya bagian integral dari upaya mereka.

Untuk mempelajari lebih lanjut tentang bagaimana Renode dapat merampingkan proyek desain bersama, kunjungi renode.io. Untuk mempelajari lebih lanjut tentang bagaimana CoreGuard dapat melindungi sistem tertanam dari serangan berbasis jaringan, minta demo untuk melihat CoreGuard beraksi.

Artikel ini ditulis bersama oleh Michael Gielda, VP Business Development dan salah satu pendiri Antmicro.

Artikel Industri adalah bentuk konten yang memungkinkan mitra industri untuk berbagi berita, pesan, dan teknologi yang bermanfaat dengan pembaca All About Circuits dengan cara yang tidak sesuai dengan konten editorial. Semua Artikel Industri tunduk pada pedoman editorial yang ketat dengan tujuan menawarkan kepada pembaca berita, keahlian teknis, atau cerita yang bermanfaat. Sudut pandang dan pendapat yang diungkapkan dalam Artikel Industri adalah dari mitra dan belum tentu dari All About Circuits atau penulisnya.