Teknologi Industri

Penguat operasional nyata memiliki beberapa ketidaksempurnaan dibandingkan dengan model "ideal". Perangkat nyata menyimpang dari penguat perbedaan sempurna. Satu minus satu mungkin bukan nol. Mungkin memiliki offset seperti meter analog yang tidak dinolkan. Input dapat menarik arus. Karakteristiknya dapat berubah seiring bertambahnya usia dan suhu. Penguatan dapat dikurangi pada frekuensi tinggi, dan fase dapat bergeser dari input ke output. Ketidaksempurnaan ini dapat menyebabkan tidak ada kesalahan yang terlihat di beberapa aplikasi, kesalahan yang tidak dapat diterima di aplikasi lain. Dalam beberapa kasus kesalahan ini dapat dikompensasikan. Terkadang diperlukan perangkat dengan kualitas lebih tinggi dan biaya lebih tinggi.

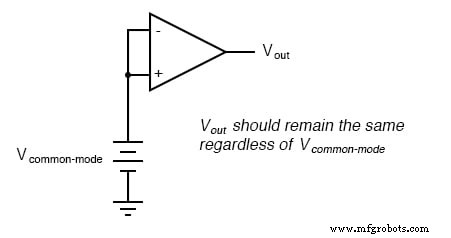

Seperti yang dinyatakan sebelumnya, penguat diferensial yang ideal hanya memperkuat perbedaan tegangan antara dua inputnya. Jika dua input dari penguat diferensial dihubung singkat (sehingga memastikan perbedaan potensial nol di antara keduanya), seharusnya tidak ada perubahan tegangan output untuk sejumlah tegangan yang diterapkan antara dua input korsleting dan ground:

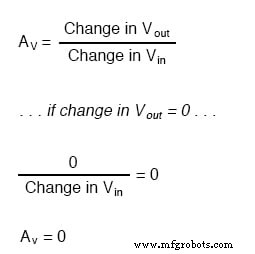

Tegangan yang umum antara salah satu input dan ground, sebagai “Vmode umum ” dalam hal ini, disebut tegangan mode umum . Saat kita memvariasikan tegangan umum ini, tegangan output penguat diferensial sempurna harus benar-benar stabil (tidak ada perubahan output untuk perubahan sembarang pada input mode umum). Ini berarti penguatan tegangan mode umum dari nol.

Penguat operasional, menjadi penguat diferensial dengan gain diferensial tinggi, idealnya memiliki gain mode umum nol juga. Namun, dalam kehidupan nyata, ini tidak mudah dicapai. Dengan demikian, tegangan mode umum akan selalu memiliki beberapa efek pada tegangan keluaran op-amp.

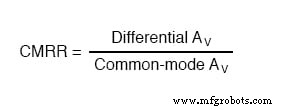

Kinerja op-amp nyata dalam hal ini paling sering diukur dalam hal penguatan tegangan diferensialnya (seberapa besar penguatan perbedaan antara dua tegangan input) versus penguatan tegangan mode umum (seberapa besar penguatan mode umum voltase). Rasio yang pertama dengan yang terakhir disebut rasio penolakan mode umum , disingkat CMRR:

Sebuah op-amp ideal, dengan nol gain mode umum akan memiliki CMRR tak terbatas. Op-amp asli memiliki CMRR yang tinggi, 741 yang ada di mana-mana memiliki sekitar 70 dB, yang menghasilkan rasio sedikit di atas 3.000.

Karena rasio penolakan mode umum dalam op-amp tipikal sangat tinggi, penguatan mode umum biasanya tidak menjadi perhatian besar di sirkuit di mana op-amp digunakan dengan umpan balik negatif. Jika tegangan input mode umum dari rangkaian penguat tiba-tiba berubah, sehingga menghasilkan perubahan yang sesuai pada output karena penguatan mode umum, perubahan output tersebut akan dengan cepat dikoreksi sebagai umpan balik negatif dan penguatan diferensial (menjadi banyak lebih besar dari gain mode umum) bekerja untuk membawa sistem kembali ke keseimbangan. Benar saja, perubahan mungkin terlihat pada output, tetapi akan jauh lebih kecil dari yang Anda harapkan.

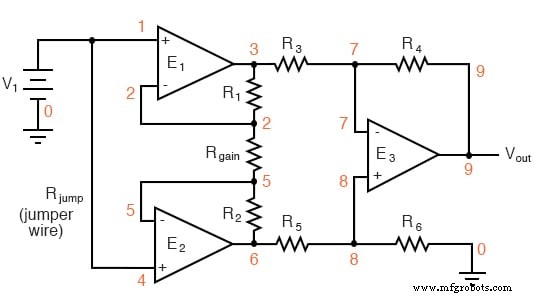

Namun, pertimbangan yang perlu diingat adalah gain mode umum dalam rangkaian op-amp diferensial seperti amplifier instrumentasi. Di luar paket op-amp yang disegel dan penguatan diferensial yang sangat tinggi, kita mungkin menemukan penguatan mode umum yang disebabkan oleh ketidakseimbangan nilai resistor. Untuk mendemonstrasikan ini, kami akan menjalankan analisis SPICE pada penguat instrumentasi dengan input yang dihubung singkat (tanpa tegangan diferensial), memaksakan tegangan mode umum untuk melihat apa yang terjadi. Pertama, kami akan menjalankan analisis yang menunjukkan tegangan output dari rangkaian seimbang sempurna. Kita seharusnya berharap tidak melihat perubahan tegangan output karena tegangan mode umum berubah:

penguat instrumentasi v1 1 0 rin1 1 0 9e12 rjump 1 4 1e-12 rin2 4 0 9e12 e1 3 0 1 2 999k e2 6 0 4 5 999k e3 9 0 8 7 999k rload 9 0 10k r1 2 3 10k perolehan 2 5 10k r2 5 6 10k r3 3 7 10k r4 7 9 10k r5 6 8 10k r6 8 0 10k .dc v1 0 10 1 .print dc v(9) .end

v1 v(9) 0,000E+00 0,000E+00 1.000E+00 1.355E-16 2.000E+00 2.710E-16 3.000E+00 0,000E+00 Seperti yang Anda lihat, tegangan output v( 9) 4.000E+00 5.421E-16 hampir tidak berubah sama sekali untuk tegangan input mode umum 5.000E+00 0.000E+00 (v1) yang menyapu dari 0 6.000E+00 0.000E+00 hingga 10 volt. 7.000E+00 0.000E+00 8.000E+00 1.084E-15 9.000E+00 -1.084E-15 1.000E+01 0.000E+00

Selain penyimpangan yang sangat kecil (sebenarnya karena kebiasaan SPICE daripada perilaku nyata dari rangkaian), output tetap stabil di tempat yang seharusnya:pada 0 volt, dengan perbedaan tegangan input nol. Namun, mari kita perkenalkan ketidakseimbangan resistor di sirkuit, meningkatkan nilai R5 dari 10.000 menjadi 10.500 , dan lihat apa yang terjadi (netlist telah dihilangkan untuk singkatnya—satu-satunya hal yang diubah adalah nilai R5 ):

v1 v(9) 0,000E+00 0,000E+00 1.000E+00 -2.439E-02 2.000E+00 -4.878E-02 3.000E+00 -7.317E-02 Kali ini kita melihat variasi yang signifikan 4.000E+00 -9.756E-02 (dari 0 hingga 0,2439 volt) pada tegangan output 5.000E+00 -1.220E-01 saat tegangan input mode-umum menyapu 6.000E+00 -1.463E-01 dari 0 hingga 10 volt seperti yang terjadi sebelumnya. 7.000E+00 -1.707E-01 8.000E+00 -1.951E-01 9.000E+00 -2.195E-01 1.000E+01 -2.439E-01

Diferensial tegangan input kami masih nol volt, namun tegangan output berubah secara signifikan karena tegangan mode umum berubah. Ini menunjukkan perolehan mode umum, sesuatu yang kami coba hindari. Lebih dari itu, ini adalah keuntungan mode umum yang kami buat sendiri, tidak ada hubungannya dengan ketidaksempurnaan dalam op-amp itu sendiri. Dengan penguatan diferensial yang jauh lebih kuat (sebenarnya sama dengan 3 di sirkuit khusus ini) dan tidak ada umpan balik negatif di luar sirkuit, penguatan mode-umum ini tidak akan dicentang dalam aplikasi sinyal instrumen.

Hanya ada satu cara untuk memperbaiki penguatan mode umum ini, dan itu adalah dengan menyeimbangkan semua nilai resistor. Saat merancang penguat instrumentasi dari komponen diskrit (daripada membeli satu dalam paket terintegrasi), sebaiknya sediakan beberapa cara untuk membuat penyesuaian halus pada setidaknya satu dari empat resistor yang terhubung ke op-amp akhir untuk dapat " memangkas” perolehan mode umum seperti itu. Menyediakan sarana untuk "memotong" jaringan resistor memiliki manfaat tambahan juga. Misalkan semua nilai resistor persis seperti yang seharusnya, tetapi gain mode umum ada karena ketidaksempurnaan pada salah satu op-amp. Dengan ketentuan penyesuaian, resistensi dapat dipangkas untuk mengkompensasi keuntungan yang tidak diinginkan ini.

Salah satu kekhasan dari beberapa model op-amp adalah keluaran latch-up , biasanya disebabkan oleh tegangan input mode umum yang melebihi batas yang diizinkan. Jika tegangan mode umum jatuh di luar batas yang ditentukan pabrikan, output mungkin tiba-tiba "terkunci" dalam mode tinggi (jenuh pada tegangan output penuh). Dalam penguat operasional input JFET, latch-up dapat terjadi jika tegangan input mode umum mendekati terlalu dekat dengan tegangan rel catu daya negatif. Pada op-amp TL082, misalnya, ini terjadi ketika tegangan input mode umum berada dalam kisaran 0,7 volt dari tegangan rel catu daya negatif. Situasi seperti itu dapat dengan mudah terjadi dalam rangkaian catu tunggal, di mana rel catu daya negatif diarde (0 volt), dan sinyal input bebas berayun ke 0 volt.

Latch-up juga dapat dipicu oleh tegangan input mode umum melebihi tegangan rel catu daya, negatif atau positif. Sebagai aturan, Anda tidak boleh membiarkan tegangan input naik di atas tegangan rel catu daya positif, atau tenggelam di bawah tegangan rel catu daya negatif, bahkan jika op-amp yang dimaksud dilindungi dari latch-up (seperti halnya 741 dan 1458 model op-amp). Paling tidak, perilaku op-amp mungkin menjadi tidak terduga. Paling buruk, jenis latch-up yang dipicu oleh tegangan input yang melebihi tegangan catu daya dapat merusak op-amp.

Meskipun masalah ini mungkin tampak mudah untuk dihindari, kemungkinannya lebih besar daripada yang Anda kira. Pertimbangkan kasus rangkaian penguat operasional selama power-up. Jika rangkaian menerima tegangan sinyal input penuh sebelum catu dayanya sendiri memiliki waktu yang cukup untuk mengisi kapasitor filter, tegangan input mode umum dapat dengan mudah melebihi tegangan rel catu daya untuk waktu yang singkat. Jika op-amp menerima tegangan sinyal dari rangkaian yang disuplai oleh sumber daya yang berbeda, dan sumber dayanya sendiri gagal, tegangan sinyal dapat melebihi tegangan rel catu daya untuk waktu yang tidak ditentukan!

Perhatian praktis lainnya untuk kinerja op-amp adalah pengimbangan tegangan . Artinya, efek memiliki tegangan keluaran selain nol volt ketika dua terminal masukan dihubung singkat. Ingatlah bahwa penguat operasional adalah penguat diferensial di atas segalanya:mereka seharusnya memperkuat perbedaan tegangan antara dua koneksi input dan tidak lebih. Ketika perbedaan tegangan input itu tepat nol volt, kita (idealnya) berharap memiliki tepat nol volt pada output. Namun, di dunia nyata hal ini jarang terjadi. Bahkan jika op-amp tersebut memiliki nol gain mode umum (CMRR tak terbatas), tegangan output mungkin tidak nol ketika kedua input dihubung singkat. Penyimpangan dari nol ini disebut offset .

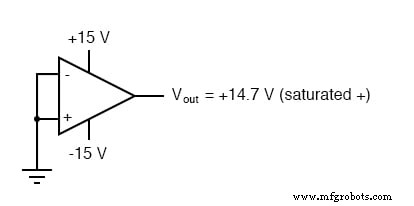

Op-amp yang sempurna akan menghasilkan voltase tepat nol dengan kedua inputnya dihubung singkat dan diarde. Namun, sebagian besar op-amp akan mendorong outputnya ke tingkat jenuh, baik negatif maupun positif. Dalam contoh yang ditunjukkan di atas, tegangan keluaran jenuh pada nilai positif 14,7 volt, hanya sedikit kurang dari +V (+15 volt) karena batas saturasi positif dari op-amp khusus ini. Karena offset dalam op-amp ini mengarahkan output ke titik jenuh sepenuhnya, tidak ada cara untuk mengetahui berapa banyak offset tegangan yang ada pada output. Jika catu daya split +V/-V memiliki tegangan yang cukup tinggi, siapa tahu, mungkin outputnya akan menjadi beberapa ratus volt karena efek offset!

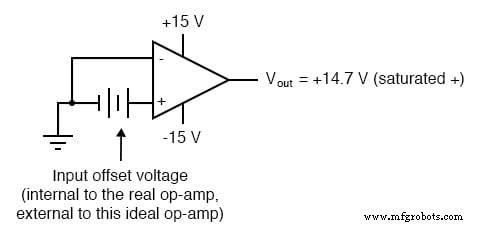

Untuk alasan ini, tegangan offset biasanya dinyatakan dalam jumlah ekivalen input diferensial tegangan menghasilkan efek ini. Dengan kata lain, kita membayangkan bahwa op-amp sempurna (tidak ada offset sama sekali), dan tegangan kecil sedang diterapkan secara seri dengan salah satu input untuk memaksa tegangan output satu arah atau yang lain menjauh dari nol. Karena keuntungan diferensial op-amp sangat tinggi, angka untuk "tegangan offset input" tidak harus banyak menjelaskan apa yang kita lihat dengan input korsleting:

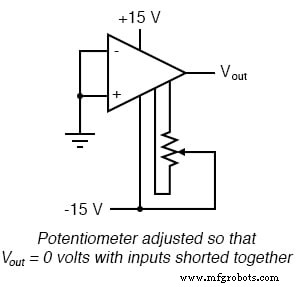

Tegangan offset akan cenderung menimbulkan sedikit kesalahan pada rangkaian op-amp manapun. Jadi bagaimana kita mengimbanginya? Tidak seperti gain mode umum, biasanya ada ketentuan yang dibuat oleh pabrikan untuk memangkas offset op-amp yang dikemas. Biasanya, dua terminal tambahan pada paket op-amp dicadangkan untuk menghubungkan potensiometer "trim" eksternal. Titik koneksi ini diberi label offset null dan digunakan dengan cara umum ini:

Pada op-amp tunggal seperti 741 dan 3130, titik koneksi nol offset adalah pin 1 dan 5 pada paket DIP 8-pin. Model op-amp lain mungkin memiliki koneksi nol offset yang terletak pada pin yang berbeda, dan/atau memerlukan konfigurasi koneksi trim potensiometer yang sedikit berbeda. Beberapa op-amp tidak menyediakan pin nol offset sama sekali! Lihat spesifikasi pabrikan untuk detailnya.

Input pada op-amp memiliki impedansi input yang sangat tinggi. Artinya, arus input yang masuk atau keluar dari dua koneksi sinyal input op-amp sangat kecil. Untuk sebagian besar tujuan analisis rangkaian op-amp, kami memperlakukannya seolah-olah mereka tidak ada sama sekali. Kami menganalisis rangkaian seolah-olah benar-benar ada arus nol yang masuk atau keluar dari koneksi input. Gambaran yang indah ini, bagaimanapun, tidak sepenuhnya benar. Op-amp, terutama op-amp dengan input transistor bipolar, harus memiliki sejumlah arus melalui koneksi inputnya agar rangkaian internalnya dibias dengan benar. Arus ini, secara logis, disebut arus bias . Dalam kondisi tertentu, arus bias op-amp mungkin bermasalah. Rangkaian berikut mengilustrasikan salah satu kondisi masalah tersebut:

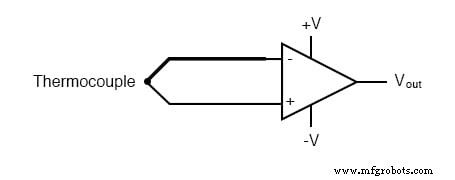

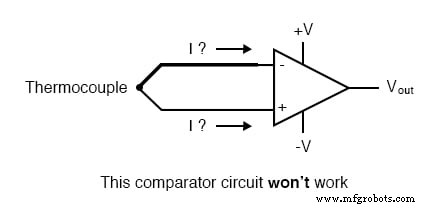

Sepintas, kami tidak melihat masalah yang jelas dengan sirkuit ini. Termokopel, menghasilkan tegangan kecil yang sebanding dengan suhu (sebenarnya, tegangan yang sebanding dengan perbedaan suhu antara sambungan pengukuran dan sambungan "referensi" yang terbentuk ketika kabel termokopel paduan terhubung dengan kabel tembaga yang mengarah ke op-amp) menggerakkan op-amp baik positif maupun negatif. Dengan kata lain, ini adalah semacam rangkaian komparator, membandingkan suhu antara sambungan termokopel ujung dan sambungan referensi (dekat op-amp). Masalahnya adalah ini:loop kawat yang dibentuk oleh termokopel tidak menyediakan jalur untuk kedua arus bias input, karena kedua arus bias mencoba mengalir dengan cara yang sama (baik ke dalam op-amp atau keluar dari op-amp).

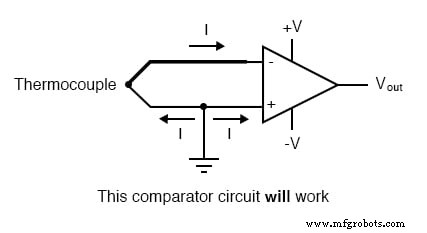

Agar rangkaian ini berfungsi dengan baik, kita harus mengardekan salah satu kabel input, sehingga menyediakan jalur ke (atau dari) pentanahan untuk kedua arus:

Belum tentu masalah yang jelas, tetapi masalah yang sangat nyata!

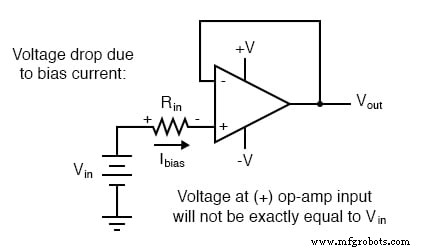

Cara lain arus bias input dapat menyebabkan masalah adalah dengan menjatuhkan tegangan yang tidak diinginkan melintasi resistansi rangkaian. Ambil sirkuit ini misalnya:

Kami mengharapkan rangkaian pengikut tegangan seperti di atas untuk mereproduksi tegangan input tepat pada output. Tetapi bagaimana dengan hambatan yang dirangkai secara seri dengan sumber tegangan input? Jika ada arus bias melalui input non-pembalik (+) sama sekali, itu akan menjatuhkan beberapa tegangan pada Rin , sehingga membuat tegangan pada input non-pembalik tidak sama dengan Vdi yang sebenarnya nilai. Arus bias biasanya dalam kisaran microamp, sehingga tegangan jatuh pada Rdi tidak akan terlalu banyak, kecuali Rdi sangat besar. Salah satu contoh aplikasi dimana resistansi input (Rdi ) akan menjadi sangat besar adalah elektroda probe pH, di mana satu elektroda mengandung penghalang kaca yang dapat ditembus ion (konduktor yang sangat buruk, dengan resistansi jutaan ).

Jika kita benar-benar membangun rangkaian op-amp untuk pengukuran tegangan elektroda pH, kita mungkin ingin menggunakan op-amp input FET atau MOSFET (IGFET) daripada yang dibangun dengan transistor bipolar (untuk arus bias input yang lebih sedikit). Namun meskipun demikian, arus bias kecil yang tersisa dapat menyebabkan kesalahan pengukuran, jadi kita harus menemukan cara untuk menguranginya melalui desain yang baik.

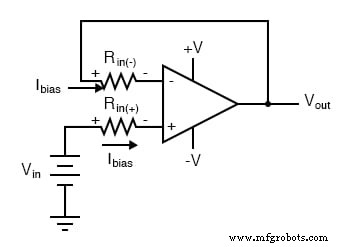

Salah satu cara untuk melakukannya didasarkan pada asumsi bahwa dua arus bias input akan sama. Pada kenyataannya, mereka sering hampir sama, perbedaan di antara mereka disebut sebagai arus offset input . Jika mereka sama, maka kita harus dapat menghilangkan efek penurunan tegangan resistansi input dengan memasukkan jumlah resistansi yang sama secara seri dengan input lainnya, seperti ini:

Dengan tambahan resistansi yang ditambahkan ke rangkaian, tegangan keluaran akan lebih dekat ke Vdi dari sebelumnya, bahkan jika ada beberapa offset antara dua arus input.

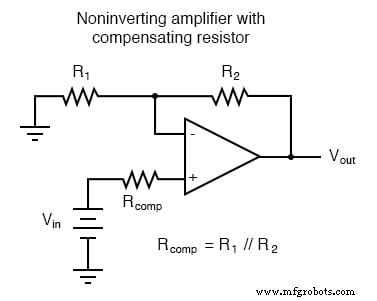

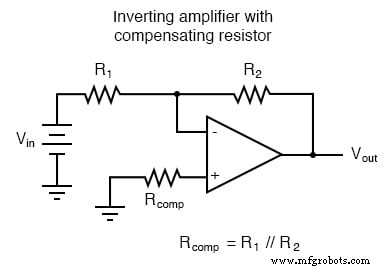

Untuk rangkaian penguat pembalik dan non-pembalik, resistor kompensasi arus bias ditempatkan secara seri dengan input non-pembalik (+) untuk mengkompensasi penurunan tegangan arus bias pada jaringan pembagi:

Dalam kedua kasus, nilai resistor kompensasi ditentukan dengan menghitung nilai resistansi paralel R1 dan R2 . Mengapa nilainya sama dengan paralel setara dengan R1 dan R2 ? Saat menggunakan Teorema Superposisi untuk mengetahui berapa banyak penurunan tegangan yang akan dihasilkan oleh arus bias masukan (-) pembalik, kita memperlakukan arus bias seolah-olah itu berasal dari sumber arus di dalam op-amp dan hubung singkat semua sumber tegangan (Vdi dan Vkeluar ). Ini memberikan dua jalur paralel untuk arus bias (melalui R1 dan melalui R2 , keduanya ke tanah). Kami ingin menduplikasi efek arus bias pada input non-pembalik (+), sehingga nilai resistor yang kami pilih untuk dimasukkan secara seri dengan input itu harus sama dengan R1 secara paralel dengan R2 .

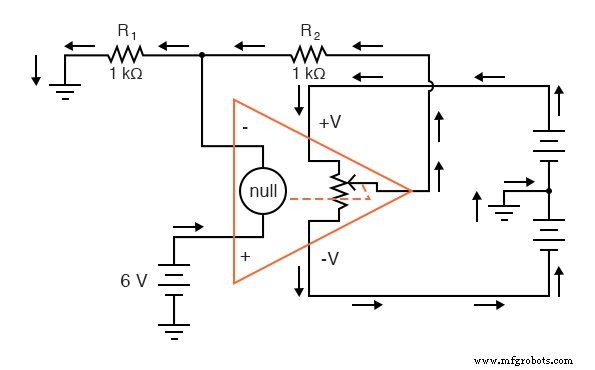

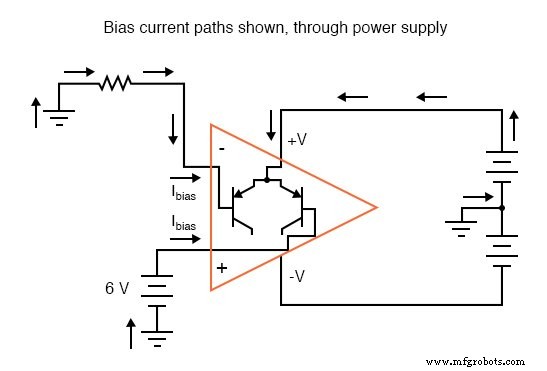

Masalah terkait, yang kadang-kadang dialami oleh siswa yang baru belajar membangun rangkaian penguat operasional, disebabkan oleh kurangnya koneksi ground bersama ke catu daya. Itu wajib untuk fungsi op-amp yang tepat bahwa beberapa terminal catu daya DC sama dengan koneksi "ground" dari sinyal input. Ini menyediakan jalur lengkap untuk arus bias, arus umpan balik, dan untuk arus beban (output). Ambil ilustrasi sirkuit ini, misalnya, menunjukkan catu daya yang diarde dengan benar:

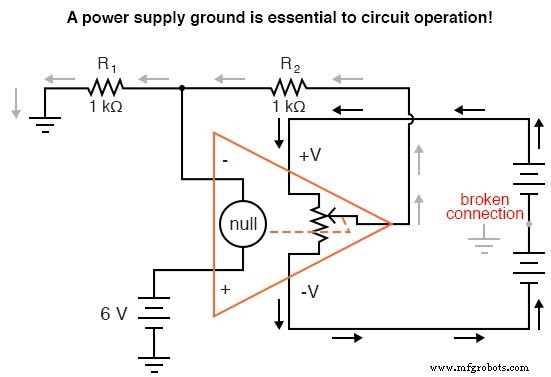

Di sini, panah menunjukkan jalur aliran elektron melalui baterai catu daya, baik untuk memberi daya pada sirkuit internal op-amp ("potensiometer" di dalamnya yang mengontrol tegangan output), dan untuk memberi daya pada loop umpan balik resistor R 1 dan R2 . Namun, anggaplah bahwa koneksi ground untuk catu daya DC "terpisah" ini harus dilepas. Efek dari melakukan ini sangat besar:

Tidak ada elektron yang dapat mengalir masuk atau keluar dari terminal keluaran op-amp, karena jalur ke catu daya adalah "jalan buntu". Jadi, tidak ada elektron yang mengalir melalui sambungan arde di sebelah kiri R1 , tidak melalui loop umpan balik. Ini secara efektif membuat op-amp tidak berguna:Op-amp tidak dapat mempertahankan arus melalui loop umpan balik, atau melalui beban yang diarde, karena tidak ada koneksi dari titik mana pun dari catu daya ke ground.

Arus bias juga dihentikan, karena mereka bergantung pada jalur ke catu daya dan kembali ke sumber input melalui ground. Diagram berikut menunjukkan arus bias (hanya), saat melewati terminal input op-amp, melalui terminal basis transistor input, dan akhirnya melalui terminal catu daya dan kembali ke ground.

Tanpa referensi ground pada catu daya, arus bias tidak akan memiliki jalur lengkap untuk suatu rangkaian, dan mereka akan berhenti. Karena transistor junction bipolar adalah perangkat yang dikendalikan arus, ini membuat tahap input op-amp tidak berguna juga, karena kedua transistor input akan dipaksa terputus oleh kekurangan arus basis.

TINJAUAN:

Menjadi perangkat semikonduktor, op-amp tunduk pada sedikit perubahan perilaku dengan perubahan suhu operasi. Setiap perubahan kinerja op-amp dengan suhu termasuk dalam kategori op-amp drift . Parameter drift dapat ditentukan untuk arus bias, tegangan offset, dan sejenisnya. Lihat lembar data pabrikan untuk mengetahui spesifikasi op-amp tertentu.

Untuk meminimalkan penyimpangan op-amp, kita dapat memilih op-amp yang dibuat untuk memiliki penyimpangan minimum, dan/atau kita dapat melakukan yang terbaik untuk menjaga suhu operasi sestabil mungkin. Tindakan terakhir mungkin melibatkan penyediaan beberapa bentuk kontrol suhu untuk bagian dalam peralatan yang menampung op-amp. Ini tidak aneh seperti yang terlihat pertama kali. Generator referensi tegangan presisi standar laboratorium, misalnya, kadang-kadang diketahui menggunakan "oven" untuk menjaga komponen sensitifnya (seperti dioda zener) pada suhu konstan. Jika akurasi yang sangat tinggi diinginkan di atas faktor biaya dan fleksibilitas yang biasa, ini mungkin merupakan opsi yang layak untuk dilihat.

TINJAUAN:

Dengan penguatan tegangan diferensial yang sangat tinggi, op-amp adalah kandidat utama untuk fenomena yang dikenal sebagai osilasi umpan balik . You’ve probably heard the equivalent audio effect when the volume (gain) on a public-address or other microphone amplifier system is turned too high:that high pitched squeal resulting from the sound waveform “feeding back” through the microphone to be amplified again. An op-amp circuit can manifest this same effect, with the feedback happening electrically rather than audibly.

A case example of this is seen in the 3130 op-amp, if it is connected as a voltage follower with the bare minimum of wiring connections (the two inputs, output, and the power supply connections). The output of this op-amp will self-oscillate due to its high gain, no matter what the input voltage. To combat this, a small compensation capacitor must be connected to two specially-provided terminals on the op-amp. The capacitor provides a high-impedance path for negative feedback to occur within the op-amp’s circuitry, thus decreasing the AC gain and inhibiting unwanted oscillations. If the op-amp is being used to amplify high-frequency signals, this compensation capacitor may not be needed, but it is absolutely essential for DC or low-frequency AC signal operation.

Some op-amps, such as the model 741, have a compensation capacitor built in to minimize the need for external components. This improved simplicity is not without a cost:due to that capacitor’s presence inside the op-amp, the negative feedback tends to get stronger as the operating frequency increases (that capacitor’s reactance decreases with higher frequencies). As a result, the op-amp’s differential voltage gain decreases as frequency goes up:it becomes a less effective amplifier at higher frequencies.

Op-amp manufacturers will publish the frequency response curves for their products. Since a sufficiently high differential gain is absolutely essential to good feedback operation in op-amp circuits, the gain/frequency response of an op-amp effectively limits its “bandwidth” of operation. The circuit designer must take this into account if good performance is to be maintained over the required range of signal frequencies.

TINJAUAN:

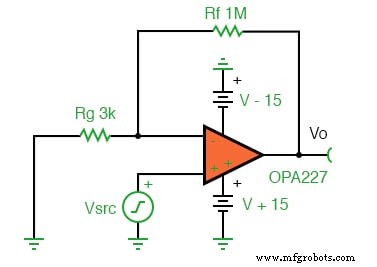

In order to illustrate the phase shift from input to output of an operational amplifier (op-amp), the OPA227 was tested in our lab. The OPA227 was constructed in a typical non-inverting configuration (Figure below).

OPA227 Non-inverting stage

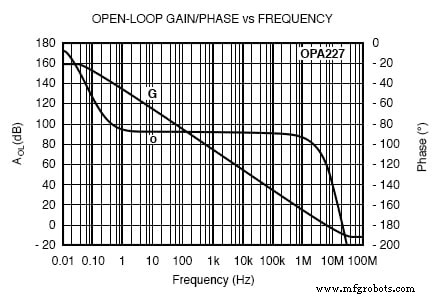

The circuit configuration calls for a signal gain of ≅34 V/V or ≅50 dB. The input excitation at Vsrc was set to 10 mVp, and three frequencies of interest:2.2 kHz, 22 kHz, and 220 MHz. The OPA227’s open loop gain and phase curve vs. frequency is shown in Figure below.

AV and Φ vs. Frequency plot

To help predict the closed loop phase shift from input to output, we can use the open loop gain and phase curve. Since the circuit configuration calls for a closed loop gain, or 1/β, of ≅50 dB, the closed loop gain curve intersects the open loop gain curve at approximately 22 kHz. After this intersection, the closed loop gain curve rolls off at the typical 20 dB/decade for voltage feedback amplifiers, and follows the open loop gain curve.

What is actually at work here is the negative feedback from the closed loop modifies the open loop response. Closing the loop with negative feedback establishes a closed loop pole at 22 kHz. Much like the dominant pole in the open loop phase curve, we will expect phase shift in the closed loop response. How much phase shift will we see?

Since the new pole is now at 22 kHz, this is also the -3 dB point as the pole starts to roll off the closed loop again at 20 dB per decade as stated earlier. As with any pole in basic control theory, phase shift starts to occur one decade in frequency before the pole, and ends at 90 o of phase shift one decade in frequency after the pole. So what does this predict for the closed loop response in our circuit?

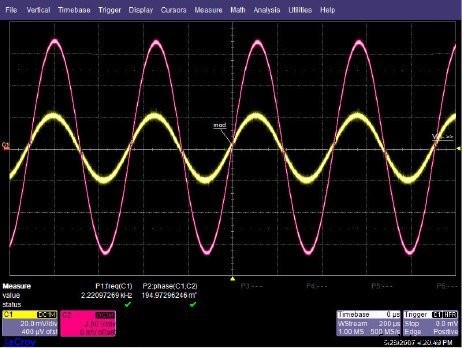

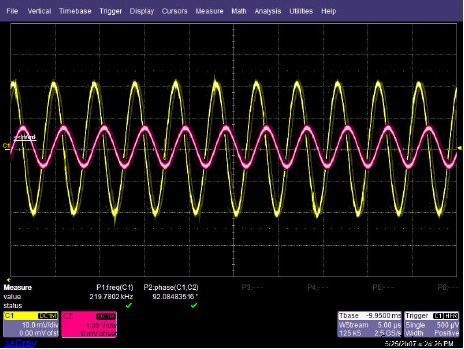

This will predict phase shift starting at 2.2 kHz, with 45 o of phase shift at the -3 dB point of 22 kHz, and finally ending with 90 o of phase shift at 220 kHz. The three Figures shown below are oscilloscope captures at the frequencies of interest for our OPA227 circuit. Figure below is set for 2.2 kHz, and no noticeable phase shift is present. Figure below is set for 220 kHz, and ≅45 o of phase shift is recorded. Finally, Figure below is set for 220 MHz, and the expected ≅90 o of phase shift is recorded. The scope plots were captured using a LeCroy 44x Wavesurfer. The final scope plot used a x1 probe with the trigger set to HF reject.

OPA227 Av=50dB @ 2.2 kHz

OPA227 Av=50dB @ 22 kHz

OPA227 Av=50dB @ 220 kHz

LEMBAR KERJA TERKAIT:

Inverting and Noninverting OpAmp Voltage Amplifier Circuits Worksheet

Teknologi Industri

Kapasitor, seperti semua komponen listrik, memiliki batasan yang harus diperhatikan demi keandalan dan pengoperasian rangkaian yang benar. Tegangan Kerja Kapasitor Tegangan kerja :Karena kapasitor tidak lebih dari dua konduktor yang dipisahkan oleh isolator (dielektrik), Anda harus memperhatikan te

Ketika alternator menghasilkan tegangan AC, tegangan mengubah polaritas dari waktu ke waktu, tetapi melakukannya dengan cara yang sangat khusus. Ketika digambarkan dari waktu ke waktu, gelombang yang dilacak oleh tegangan polaritas bolak-balik ini dari alternator mengambil bentuk yang berbeda, yang

Kapasitas Daya Seperti yang telah diamati, transformator harus dirancang dengan baik untuk mencapai sambungan daya yang dapat diterima, pengaturan tegangan yang ketat, dan distorsi arus eksitasi yang rendah. Juga, transformator harus dirancang untuk membawa nilai yang diharapkan dari arus belitan p

Fungsi utama dari Desain penguat derau rendah adalah memperkuat sinyal daya kecil. Dalam mikrofon elektronik, pesan dapat berupa tegangan atau arus, variabel w.r.t. Waktu. Seperti semua amplifier, amplifier dengan derau rendah juga merupakan sirkuit dua port. Ini mengkonsumsi daya listrik untuk meni