Verilog

Penghitung 4-bit mulai bertambah dari 4'b0000 ke 4'h1111 dan kemudian bergulir kembali ke 4'b0000. Ini akan terus menghitung selama dilengkapi dengan jam berjalan dan reset disetel tinggi.

Rollover terjadi ketika bit paling signifikan dari penambahan terakhir dibuang. Ketika penghitung berada pada nilai maksimum 4'b1111 dan mendapat satu permintaan penghitungan lagi, penghitung mencoba mencapai 5'b10000 tetapi karena hanya dapat mendukung 4-bit, MSB akan dibuang sehingga menghasilkan 0.

0000 0001 0010 ... 1110 1111 rolls over 0000 0001 ...

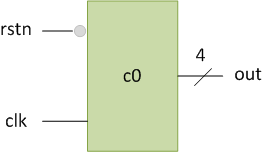

Desain berisi dua input satu untuk jam dan satu lagi untuk reset aktif-rendah. Reset aktif-rendah adalah di mana desain direset ketika nilai pin reset adalah 0. Ada output 4-bit yang dipanggil yang pada dasarnya menyediakan nilai penghitung.

module counter ( input clk, // Declare input port for clock to allow counter to count up

input rstn, // Declare input port for reset to allow the counter to be reset to 0 when required

output reg[3:0] out); // Declare 4-bit output port to get the counter values

// This always block will be triggered at the rising edge of clk (0->1)

// Once inside this block, it checks if the reset is 0, if yes then change out to zero

// If reset is 1, then design should be allowed to count up, so increment counter

always @ (posedge clk) begin

if (! rstn)

out <= 0;

else

out <= out + 1;

end

endmodule

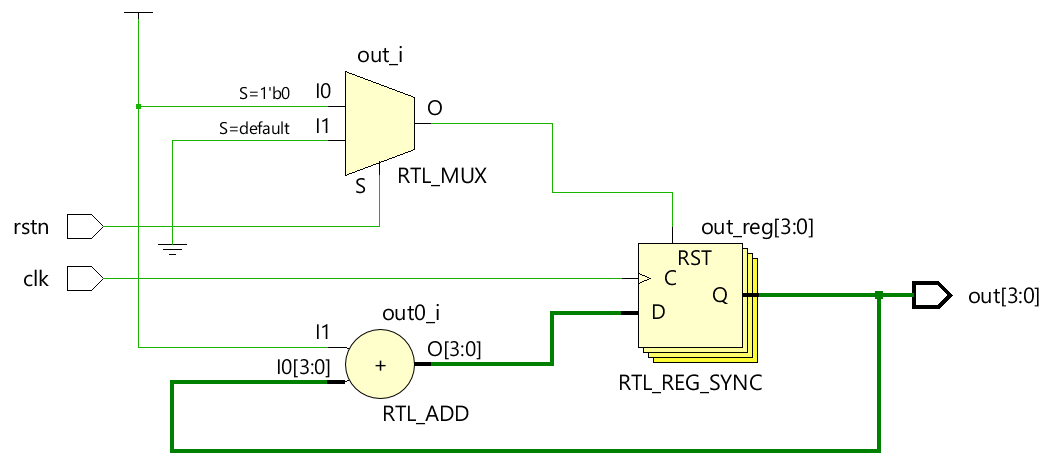

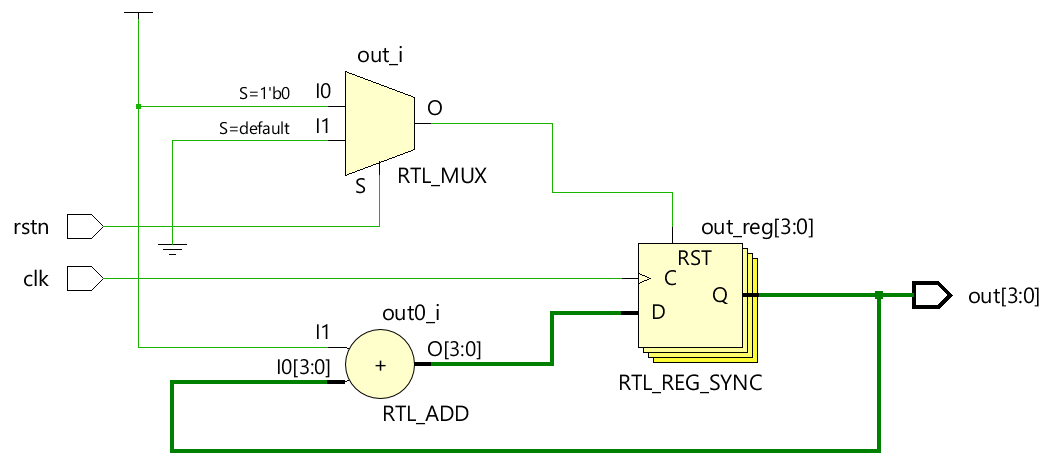

module penghitung memiliki jam dan reset aktif-rendah (dilambangkan dengan n ) sebagai input dan nilai counter sebagai output 4-bit. always blok selalu dieksekusi setiap kali jam bertransisi dari 0 ke 1 yang menandakan sisi naik atau sisi positif. Output bertambah hanya jika reset ditahan tinggi atau 1, dicapai dengan if-else memblokir. Jika reset ditemukan rendah di tepi positif jam, maka output diatur ulang ke nilai default 4'b0000.

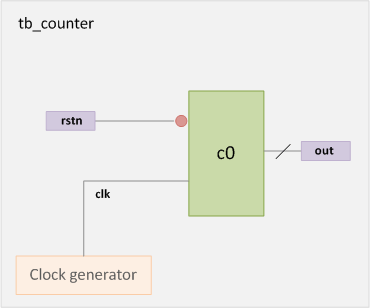

Kami dapat membuat instance desain ke modul testbench kami untuk memverifikasi bahwa penghitung menghitung seperti yang diharapkan.

Modul testbench bernama tb_counter dan port tidak diperlukan karena ini adalah modul teratas dalam simulasi. Namun kita perlu memiliki variabel internal untuk menghasilkan, menyimpan dan menggerakkan jam dan mengatur ulang. Untuk itu, kami telah mendeklarasikan dua variabel bertipe reg untuk jam dan reset. Kami juga membutuhkan wire ketik net untuk membuat koneksi dengan output desain, jika tidak maka akan default ke jaring skalar 1-bit.

Jam dihasilkan melalui always balok yang akan memberikan periode 10 satuan waktu. initial blok digunakan untuk mengatur nilai awal ke variabel internal kami dan mengarahkan nilai reset ke desain. Desainnya dicontohkan di testbench dan terhubung ke variabel internal kami, sehingga akan mendapatkan nilai saat kami mengusirnya dari testbench. Kami tidak memiliki $display pernyataan di testbench kami dan karenanya kami tidak akan melihat pesan apa pun di konsol.

module tb_counter;

reg clk; // Declare an internal TB variable called clk to drive clock to the design

reg rstn; // Declare an internal TB variable called rstn to drive active low reset to design

wire [3:0] out; // Declare a wire to connect to design output

// Instantiate counter design and connect with Testbench variables

counter c0 ( .clk (clk),

.rstn (rstn),

.out (out));

// Generate a clock that should be driven to design

// This clock will flip its value every 5ns -> time period = 10ns -> freq = 100 MHz

always #5 clk = ~clk;

// This initial block forms the stimulus of the testbench

initial begin

// 1. Initialize testbench variables to 0 at start of simulation

clk <= 0;

rstn <= 0;

// 2. Drive rest of the stimulus, reset is asserted in between

#20 rstn <= 1;

#80 rstn <= 0;

#50 rstn <= 1;

// 3. Finish the stimulus after 200ns

#20 $finish;

end

endmodule

Log Simulasi ncsim> run [0ns] clk=0 rstn=0 out=0xx [5ns] clk=1 rstn=0 out=0x0 [10ns] clk=0 rstn=0 out=0x0 [15ns] clk=1 rstn=0 out=0x0 [20ns] clk=0 rstn=1 out=0x0 [25ns] clk=1 rstn=1 out=0x1 [30ns] clk=0 rstn=1 out=0x1 [35ns] clk=1 rstn=1 out=0x2 [40ns] clk=0 rstn=1 out=0x2 [45ns] clk=1 rstn=1 out=0x3 [50ns] clk=0 rstn=1 out=0x3 [55ns] clk=1 rstn=1 out=0x4 [60ns] clk=0 rstn=1 out=0x4 [65ns] clk=1 rstn=1 out=0x5 [70ns] clk=0 rstn=1 out=0x5 [75ns] clk=1 rstn=1 out=0x6 [80ns] clk=0 rstn=1 out=0x6 [85ns] clk=1 rstn=1 out=0x7 [90ns] clk=0 rstn=1 out=0x7 [95ns] clk=1 rstn=1 out=0x8 [100ns] clk=0 rstn=0 out=0x8 [105ns] clk=1 rstn=0 out=0x0 [110ns] clk=0 rstn=0 out=0x0 [115ns] clk=1 rstn=0 out=0x0 [120ns] clk=0 rstn=0 out=0x0 [125ns] clk=1 rstn=0 out=0x0 [130ns] clk=0 rstn=0 out=0x0 [135ns] clk=1 rstn=0 out=0x0 [140ns] clk=0 rstn=0 out=0x0 [145ns] clk=1 rstn=0 out=0x0 [150ns] clk=0 rstn=1 out=0x0 [155ns] clk=1 rstn=1 out=0x1 [160ns] clk=0 rstn=1 out=0x1 [165ns] clk=1 rstn=1 out=0x2 Simulation complete via $finish(1) at time 170 NS + 0

Perhatikan bahwa penghitung direset ke 0 saat reset aktif-rendah menjadi 0, dan saat reset dibatalkan di sekitar 150ns, penghitung mulai menghitung dari kemunculan berikutnya dari tepi positif jam.

Verilog

Komponen dan persediaan Arduino Nano R3 × 1 Buzzer × 1 LED 5 mm:Merah × 1 LED 5 mm:Hijau × 1 Texas Instruments Shift Register- Serial to Parallel × 1 Tampilan LED 7 Segmen, Merah × 1 Resistor 221 ohm × 10 Baterai 9V (ge

Mari kita hadapi itu. Crosstalk PCB adalah masalah besar yang dihadapi rata-rata insinyur dengan PCB berkecepatan tinggi. Saat ini, kami memiliki lebih banyak papan kompak, sehingga lebih penting untuk menganalisis crosstalk sebelum merakit PCB. Namun, jika Anda tidak terbiasa dengan konsep crossta

RESET setelah Edit Program di Fanuc TC Teknisi CNC harus selalu ingat untuk menekan tombol RESET sebelum menekan CYCLE START pada mesin cnc dengan kontrol cnc FANUC TC (mis. Gildemeister NEF 560), jika mereka membuat perubahan pada program bagian cnc mereka.

Kode M Heidenhain ( Fungsi lain-lain) untuk Heidenhain TNC 640/530/410/426/430/320 Heidenhain TNC 320 Kode Heidenhain M Kode M Deskripsi M0 Hentikan program berjalan (Spindle STOP, Coolant OFF) M1 Program opsional STOP (Spindle STOP, Coolant OFF) M2 Hentikan program berjalan (Spindle STOP,Coola