Sirkuit Gerbang CMOS

Sampai saat ini, analisis rangkaian logika transistor kami terbatas pada TTL paradigma desain, di mana transistor bipolar digunakan, dan strategi umum input mengambang setara dengan "tinggi" (terhubung ke Vcc ) masukan—dan dengan demikian, kelonggaran tahap keluaran “kolektor terbuka”—dipertahankan. Namun, ini bukan satu-satunya cara kita dapat membangun gerbang logika.

Transistor Efek Medan

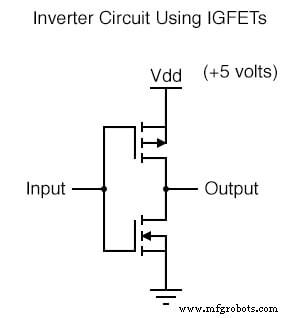

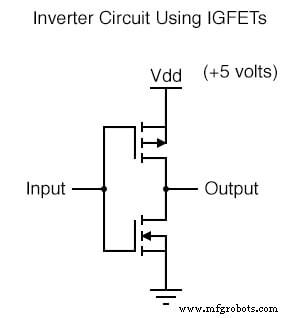

Transistor efek medan, khususnya jenis gerbang berinsulasi, dapat digunakan dalam desain rangkaian gerbang. Menjadi perangkat yang dikendalikan tegangan daripada perangkat yang dikendalikan arus, IGFET cenderung memungkinkan desain sirkuit yang sangat sederhana. Ambil contoh, rangkaian inverter berikut yang dibuat menggunakan IGFET saluran-P dan N:

Perhatikan “Vdd ” pada terminal catu daya positif. Label ini mengikuti konvensi yang sama dengan “Vcc ” di sirkuit TTL:singkatan dari tegangan konstan yang diterapkan ke saluran pembuangan transistor efek medan, mengacu pada ground.

Transistor Efek Medan di Sirkuit Gerbang

Masukan Rendah

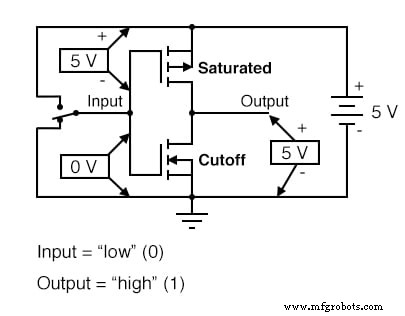

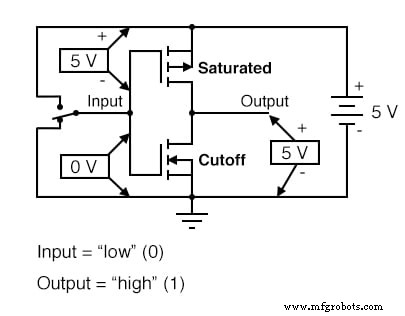

Mari kita sambungkan rangkaian gerbang ini ke sumber daya dan sakelar input, dan periksa operasinya. Harap dicatat bahwa transistor IGFET ini adalah tipe-E (mode Peningkatan), dan begitu juga biasanya mati perangkat.

Dibutuhkan tegangan yang diterapkan antara gerbang dan saluran (sebenarnya, antara gerbang dan substrat) dari polaritas yang benar untuk bias on .

Transistor atas adalah IGFET saluran-P. Ketika saluran (substrat) dibuat lebih positif daripada gerbang (gerbang negatif mengacu pada substrat), saluran ditingkatkan dan arus diperbolehkan antara sumber dan saluran.

Jadi, pada ilustrasi di atas, transistor atas dihidupkan. Transistor bawah, memiliki tegangan nol antara gerbang dan substrat (sumber), berada dalam mode normalnya:mati .

Dengan demikian, aksi kedua transistor ini sedemikian rupa sehingga terminal keluaran dari rangkaian gerbang memiliki koneksi yang solid ke Vdd dan koneksi resistansi yang sangat tinggi ke ground. Ini membuat output “tinggi” (1) untuk status input “rendah” (0).

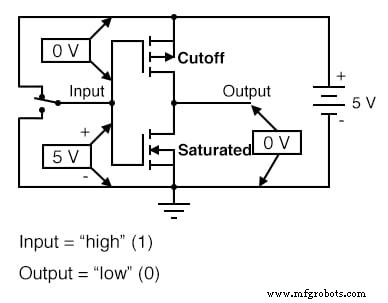

Masukan Tinggi

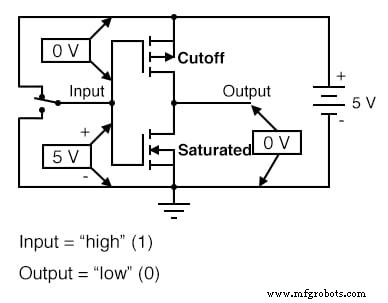

Selanjutnya, kita akan memindahkan sakelar input ke posisi lainnya dan melihat apa yang terjadi:

Sekarang transistor bawah (N-channel) jenuh karena memiliki tegangan yang cukup dari polaritas yang benar diterapkan antara gerbang dan substrat (saluran) untuk menyalakannya (positif pada gerbang, negatif pada saluran). Transistor atas, yang memiliki tegangan nol diterapkan antara gerbang dan substratnya, berada dalam mode normalnya:mati .

Dengan demikian, output dari rangkaian gerbang ini sekarang "rendah" (0). Jelas, sirkuit ini menunjukkan perilaku inverter, atau gerbang NOT.

Semikonduktor Oksida Logam Pelengkap (CMOS)

Menggunakan transistor efek medan sebagai pengganti transistor bipolar telah sangat menyederhanakan desain gerbang inverter. Perhatikan bahwa output dari gerbang ini tidak pernah mengapung seperti halnya dengan rangkaian TTL yang paling sederhana:ia memiliki konfigurasi “kutub totem” alami, yang mampu mengalirkan dan menenggelamkan arus beban.

Kunci dari desain elegan sirkuit gerbang ini adalah pelengkap penggunaan kedua P- dan N-channel IGFET. Karena IGFET lebih dikenal sebagai MOSFET (M etal-O xide-S semikonduktor F bidang E efek T ransistor), dan rangkaian ini menggunakan transistor saluran-P dan N bersama-sama, klasifikasi umum yang diberikan untuk rangkaian gerbang seperti ini adalah CMOS :C pelengkap M dkk O xide S semikonduktor.

Gerbang CMOS:Tantangan dan Solusi

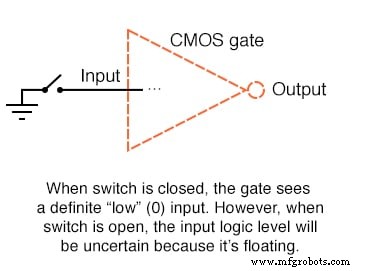

Sirkuit CMOS tidak terganggu oleh ketidaklinieran yang melekat pada transistor efek medan, karena sebagai sirkuit digital transistor mereka selalu beroperasi dalam kondisi jenuh atau batas mode dan tidak pernah dalam aktif mode. Namun, inputnya sensitif terhadap tegangan tinggi yang dihasilkan oleh sumber elektrostatik (listrik statis), dan bahkan dapat diaktifkan ke status "tinggi" (1) atau "rendah" (0) oleh sumber tegangan palsu jika dibiarkan mengambang.

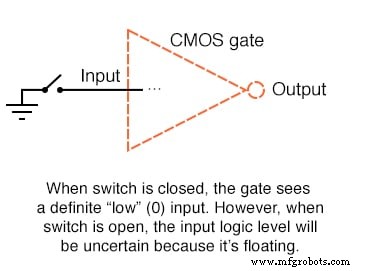

Untuk alasan ini, tidak disarankan untuk membiarkan input gerbang logika CMOS mengapung dalam keadaan apa pun. Harap perhatikan bahwa ini sangat berbeda dari perilaku gerbang TTL di mana input mengambang ditafsirkan dengan aman sebagai level logika “tinggi” (1).

Masalah CMOS dengan Input Mengambang

Hal ini dapat menyebabkan masalah jika input ke gerbang logika CMOS digerakkan oleh sakelar sekali pakai, di mana satu keadaan memiliki input yang terhubung secara solid ke salah satu Vdd atau ground dan status lainnya memiliki input mengambang (tidak terhubung ke apa pun):

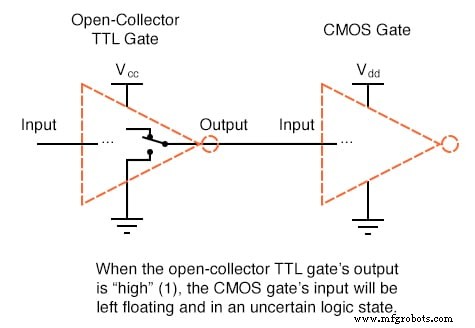

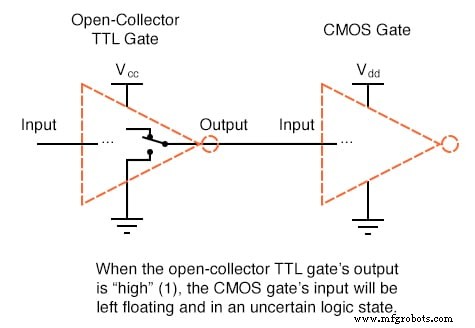

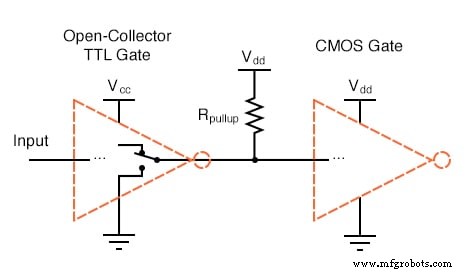

Juga, masalah ini muncul jika input gerbang CMOS digerakkan oleh kolektor terbuka gerbang TTL. Karena output gerbang TTL seperti itu mengapung ketika menjadi "tinggi" (1), input gerbang CMOS akan dibiarkan dalam keadaan tidak pasti:

Solusi untuk Input Mengambang

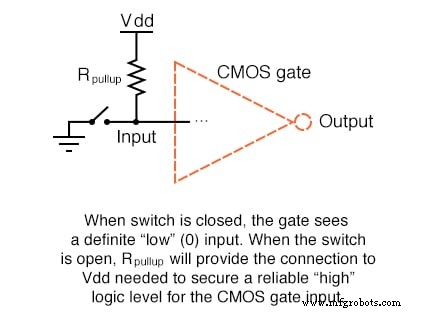

Resistor Tarik

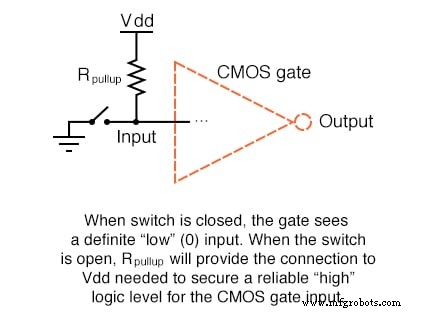

Untungnya, ada solusi mudah untuk dilema ini, yang sering digunakan dalam sirkuit logika CMOS. Setiap kali sakelar sekali pakai (atau keluaran gerbang jenis apa pun lainnya tidak mampu keduanya sumber dan arus tenggelam) digunakan untuk menggerakkan input CMOS, resistor yang terhubung ke Vdd atau ground dapat digunakan untuk menyediakan level logika yang stabil untuk status di mana output perangkat penggerak mengambang.

Nilai resistor ini tidak kritis:10 kΩ biasanya cukup. Ketika digunakan untuk memberikan tingkat logika "tinggi" (1) jika sumber sinyal mengambang, resistor ini dikenal sebagai resistor pullup :

Resistor Pulldown

Ketika resistor tersebut digunakan untuk memberikan tingkat logika "rendah" (0) dalam hal sumber sinyal mengambang, ini dikenal sebagai resistor pull-down . Sekali lagi, nilai resistor pull-down tidak kritis:

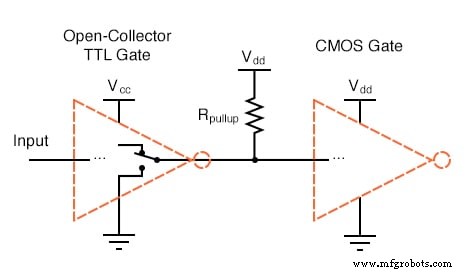

Karena keluaran TTL kolektor terbuka selalu tenggelam, tidak pernah sumber, arus, tariknaik resistor diperlukan saat menghubungkan output seperti itu ke input gerbang CMOS:

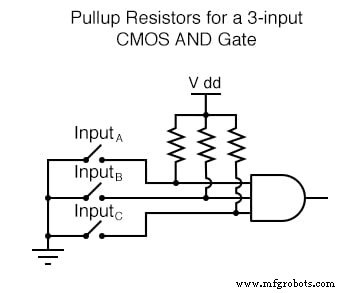

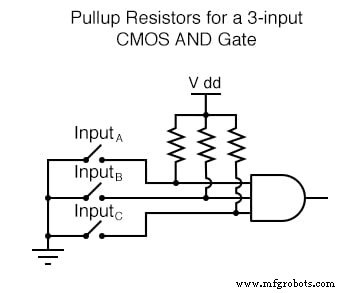

Beberapa Resistor Pullup dan Pulldown

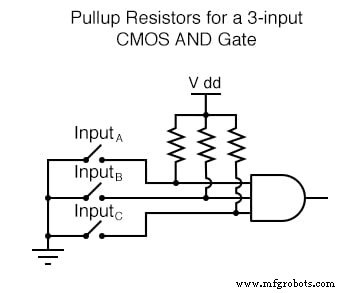

Meskipun gerbang CMOS yang digunakan dalam contoh sebelumnya adalah semua inverter (input tunggal), prinsip resistor pullup dan pulldown yang sama berlaku untuk gerbang CMOS input ganda. Tentu saja, resistor pullup atau pulldown terpisah akan diperlukan untuk setiap input gerbang:

Ini membawa kita ke pertanyaan berikutnya:bagaimana kita mendesain gerbang CMOS multi-input seperti AND, NAND, OR, dan NOR? Tidak mengherankan, jawaban atas pertanyaan ini mengungkapkan kesederhanaan desain seperti halnya inverter CMOS di atas ekuivalen TTL-nya.

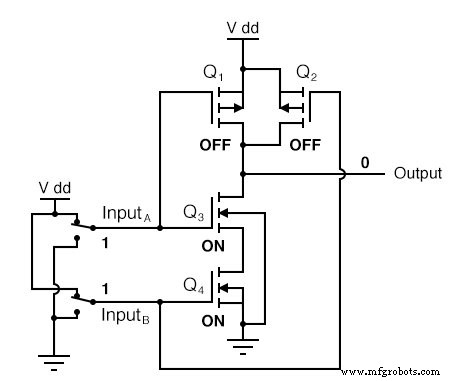

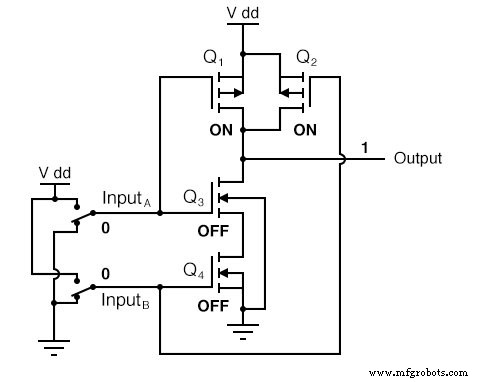

Gerbang CMOS NAND

Sebagai contoh, berikut adalah diagram skema untuk gerbang NAND CMOS:

Perhatikan bagaimana transistor Q1 dan T3 menyerupai pasangan komplementer yang terhubung seri dari rangkaian inverter. Keduanya dikendalikan oleh sinyal input yang sama (input A), transistor atas mati dan transistor bawah menyala saat input "tinggi" (1), dan sebaliknya.

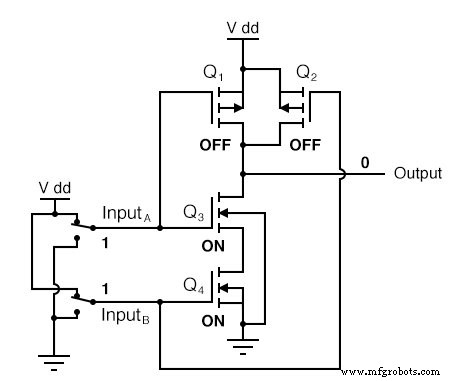

Perhatikan juga bagaimana transistor Q2 dan T4 sama-sama dikendalikan oleh sinyal input yang sama (input B), dan bagaimana sinyal tersebut juga akan menunjukkan perilaku hidup/mati yang sama untuk level logika input yang sama. Transistor atas dari kedua pasangan (Q1 dan T2 ) memiliki terminal sumber dan saluran pembuangan paralel, sedangkan transistor bawah (Q3 dan T4 ) terhubung secara seri.

Artinya, output akan menjadi "tinggi" (1) jika salah satu transistor atas jenuh, dan akan menjadi "rendah" (0) hanya jika keduanya saturasi transistor lebih rendah.

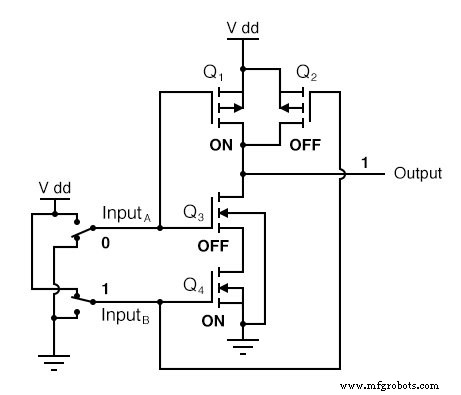

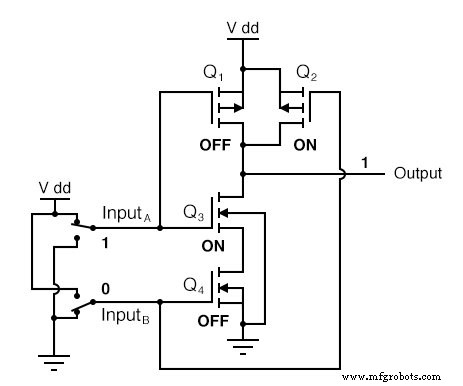

Perilaku Sirkuit CMOS untuk Semua Input Logika

Urutan ilustrasi berikut menunjukkan perilaku gerbang NAND ini untuk keempat kemungkinan level logika input (00, 01, 10, dan 11):

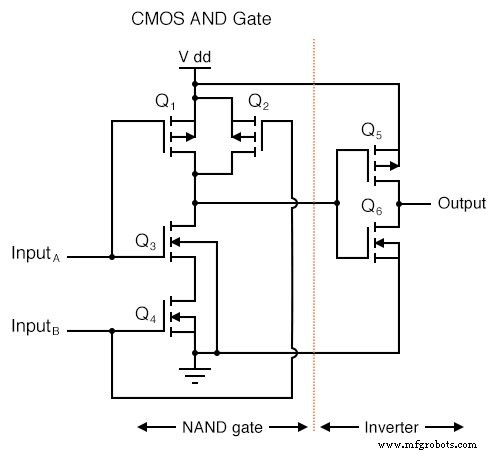

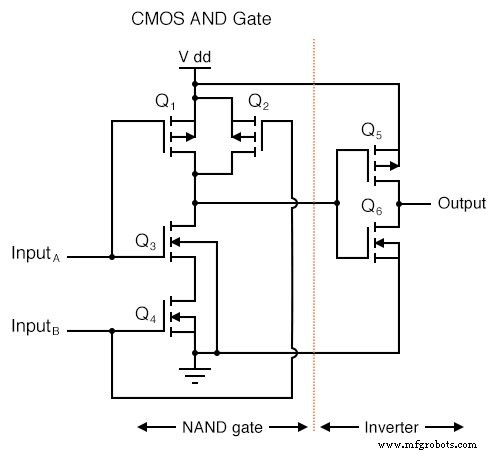

CMOS DAN gerbang

Seperti halnya gerbang NAND TTL, rangkaian gerbang NAND CMOS dapat digunakan sebagai titik awal untuk pembuatan gerbang AND. Yang perlu ditambahkan hanyalah transistor tahap lain untuk membalikkan sinyal output:

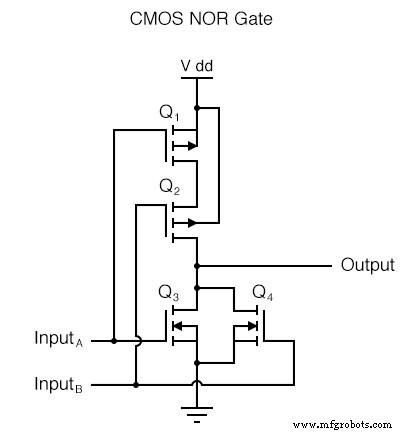

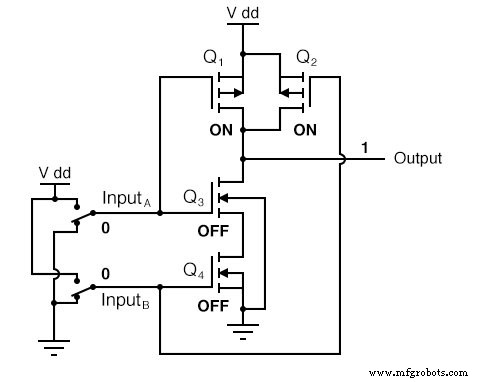

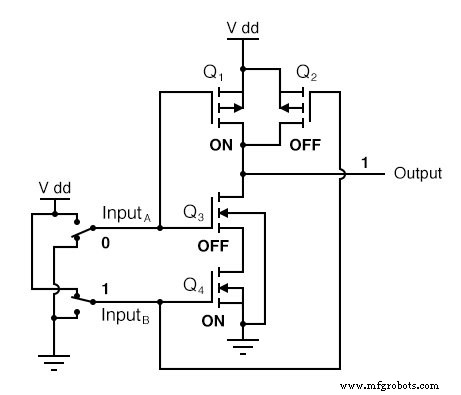

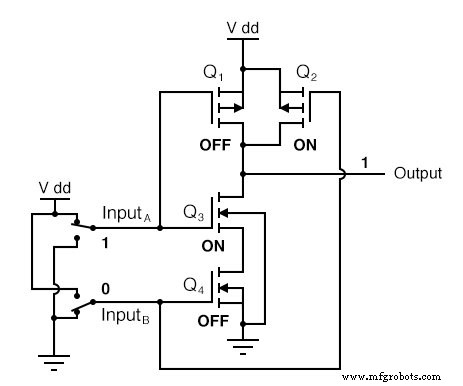

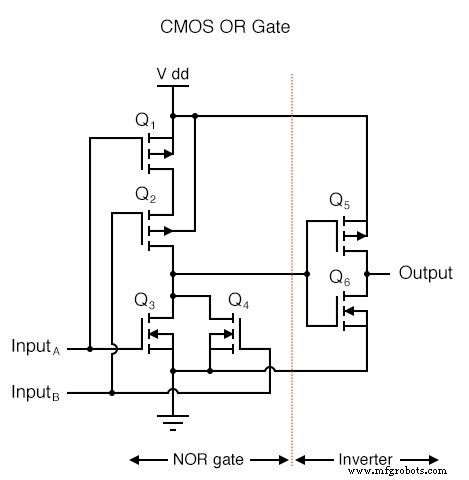

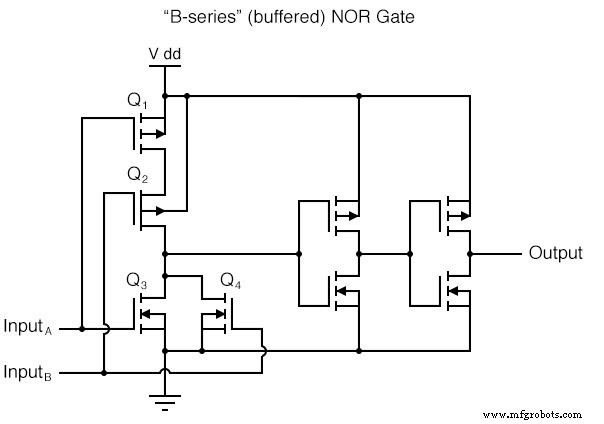

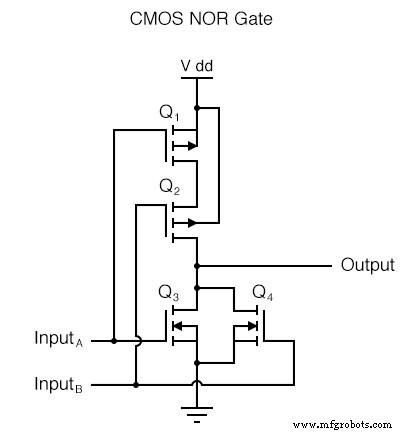

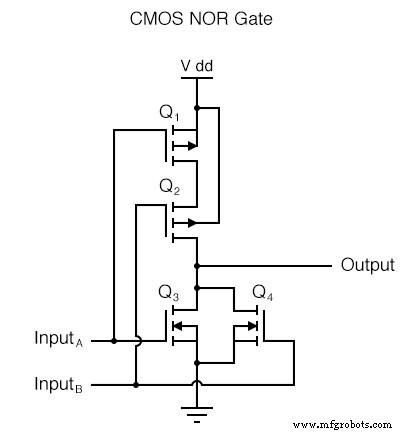

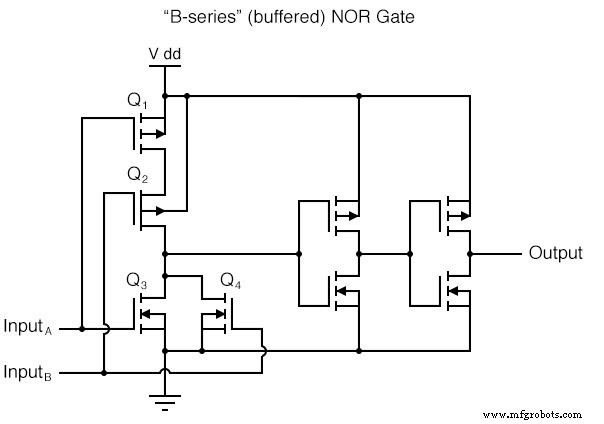

Gerbang CMOS NOR

Rangkaian gerbang NOR CMOS menggunakan empat MOSFET seperti gerbang NAND, kecuali transistornya diatur secara berbeda. Alih-alih dua sumber parallel yang paralel transistor (atas) terhubung ke Vdd dan dua tenggelam . yang terhubung seri (bawah) transistor terhubung ke ground, gerbang NOR menggunakan dua transistor sumber terhubung seri dan dua transistor tenggelam terhubung paralel seperti ini:

Seperti gerbang NAND, transistor Q1 dan T3 bekerja sebagai pasangan pelengkap, seperti halnya transistor Q2 dan T4 . Setiap pasangan dikendalikan oleh sinyal input tunggal. Jika salah satu masukan A atau input B adalah "tinggi" (1), setidaknya salah satu transistor yang lebih rendah (Q3 atau T4 ) akan jenuh, sehingga membuat output “rendah” (0).

Hanya jika keduanya input menjadi "rendah" (0) akan kedua transistor bawah berada dalam mode cutoff dan kedua transistor atas menjadi jenuh, kondisi yang diperlukan untuk output menjadi "tinggi" (1). Perilaku ini, tentu saja, mendefinisikan fungsi logika NOR.

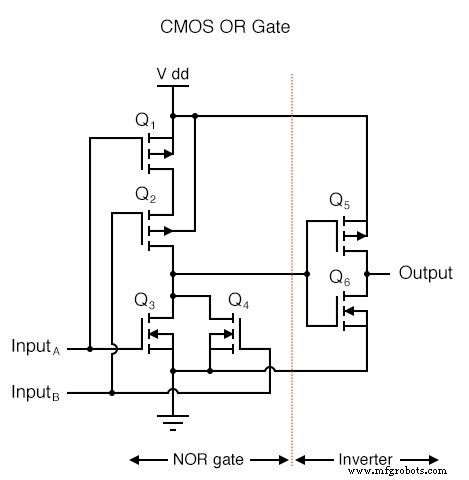

CMOS ATAU Gerbang

Fungsi OR dapat dibangun dari gerbang NOR dasar dengan penambahan tahap inverter pada output:

TTL vs. CMOS:Keuntungan dan Kerugian

Karena tampaknya gerbang apa pun yang mungkin dibuat menggunakan teknologi TTL dapat diduplikasi dalam CMOS, mengapa kedua "keluarga" desain logika ini masih hidup berdampingan? Jawabannya adalah TTL dan CMOS memiliki keunggulan uniknya masing-masing.

Pertama dan terpenting dalam daftar perbandingan antara TTL dan CMOS adalah masalah konsumsi daya. Dalam ukuran kinerja ini, CMOS adalah pemenang yang tak tertandingi. Karena pasangan MOSFET kanal-P dan N komplementer dari rangkaian gerbang CMOS (idealnya) tidak pernah konduksi pada waktu yang sama, ada sedikit atau tidak ada arus yang ditarik oleh rangkaian dari Vdd catu daya kecuali untuk arus apa yang diperlukan untuk sumber arus ke beban. TTL, di sisi lain, tidak dapat berfungsi tanpa arus yang ditarik setiap saat, karena persyaratan bias transistor bipolar dari mana ia dibuat.

Ada peringatan untuk keuntungan ini, meskipun. Sementara disipasi daya gerbang TTL tetap agak konstan terlepas dari status operasinya, gerbang CMOS menghilangkan lebih banyak daya saat frekuensi sinyal inputnya meningkat. Jika gerbang CMOS dioperasikan dalam kondisi statis (tidak berubah), ia menghilangkan daya nol (idealnya).

Namun, sirkuit gerbang CMOS menarik arus transien selama setiap status keluaran beralih dari "rendah" ke "tinggi" dan sebaliknya. Jadi, semakin sering gerbang CMOS beralih mode, semakin sering ia akan menarik arus dari Vdd pasokan, sehingga disipasi daya yang lebih besar pada frekuensi yang lebih besar.

Keuntungan CMOS

Gerbang CMOS juga menarik arus yang jauh lebih sedikit dari output gerbang penggerak daripada gerbang TTL karena MOSFET adalah perangkat yang dikendalikan tegangan, bukan dikendalikan arus. Ini berarti bahwa satu gerbang dapat menggerakkan lebih banyak input CMOS daripada input TTL. Ukuran berapa banyak input gerbang yang dapat dikendarai oleh satu output gerbang disebut fanout .

Keuntungan lain yang dinikmati desain gerbang CMOS dibandingkan TTL adalah rentang tegangan catu daya yang jauh lebih lebar yang diizinkan. Sedangkan gerbang TTL dibatasi untuk catu daya (Vcc ) tegangan antara 4,75 dan 5,25 volt, gerbang CMOS biasanya dapat beroperasi pada tegangan apa pun antara 3 dan 15 volt!

Alasan di balik perbedaan tegangan catu daya ini adalah persyaratan bias masing-masing MOSFET versus transistor sambungan bipolar. MOSFET dikendalikan secara eksklusif oleh tegangan gerbang (berkenaan dengan substrat), sedangkan BJT dikontrol arus perangkat.

Resistansi rangkaian gerbang TTL dihitung dengan tepat untuk arus bias yang tepat dengan asumsi catu daya yang diatur 5 volt. Setiap variasi yang signifikan dalam tegangan catu daya tersebut akan mengakibatkan arus bias transistor menjadi salah, yang kemudian menghasilkan operasi yang tidak dapat diandalkan (tidak dapat diprediksi).

Satu-satunya efek yang dimiliki variasi tegangan catu daya pada gerbang CMOS adalah definisi tegangan dari status "tinggi" (1). Untuk gerbang CMOS yang beroperasi pada tegangan catu daya 15 volt (Vdd ), sinyal input harus mendekati 15 volt agar dianggap "tinggi" (1). Ambang tegangan untuk sinyal “rendah” (0) tetap sama:mendekati 0 volt.

Kekurangan CMOS

Salah satu kelemahan CMOS adalah kecepatan lambat, dibandingkan dengan TTL. Kapasitansi input gerbang CMOS jauh, jauh lebih besar daripada gerbang TTL yang sebanding — karena penggunaan MOSFET daripada BJT — dan gerbang CMOS akan lebih lambat untuk merespons transisi sinyal (rendah ke tinggi atau sebaliknya) daripada gerbang TTL, semua faktor lainnya dianggap sama.

Konstanta waktu RC yang dibentuk oleh resistansi rangkaian dan kapasitansi input gerbang cenderung menghambat waktu naik dan turun yang cepat dari tingkat logika digital, sehingga menurunkan kinerja frekuensi tinggi.

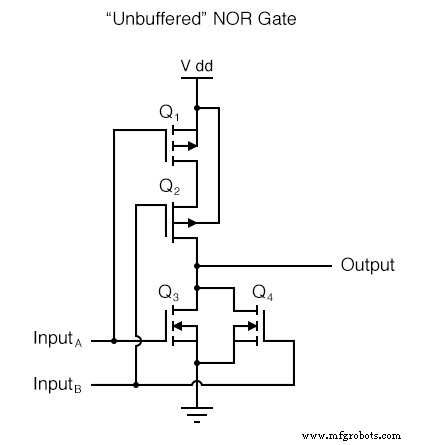

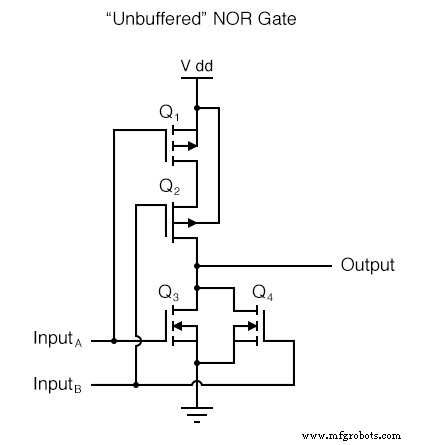

Strategi untuk Memerangi Kerugian

Strategi untuk meminimalkan kerugian yang melekat pada sirkuit gerbang CMOS ini adalah dengan "menyangga" sinyal keluaran dengan tahapan transistor tambahan, untuk meningkatkan penguatan tegangan keseluruhan perangkat. Ini memberikan tegangan keluaran transisi yang lebih cepat (tinggi ke rendah atau rendah ke tinggi) untuk tegangan masukan yang perlahan berubah dari satu keadaan logika ke keadaan logika lainnya.

Pertimbangkan contoh ini, dari gerbang NOR “tanpa buffer” versus “buffered”, atau B-series , gerbang NOR:

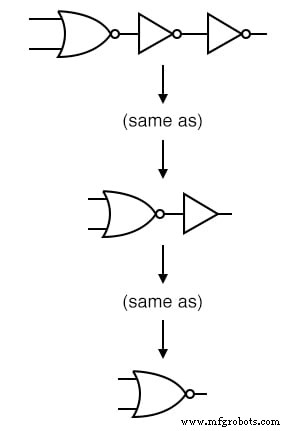

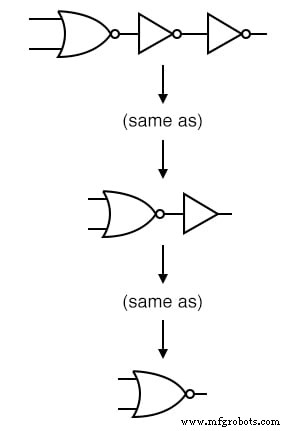

Intinya, peningkatan desain seri-B menambahkan dua inverter ke output rangkaian NOR sederhana. Ini tidak berguna sejauh menyangkut logika digital, karena dua inverter bertingkat hanya membatalkan:

Namun, menambahkan tahapan inverter ini ke sirkuit memang bertujuan untuk meningkatkan penguatan tegangan secara keseluruhan, membuat output lebih sensitif terhadap perubahan status input, bekerja untuk mengatasi kelambatan bawaan yang disebabkan oleh kapasitansi input gerbang CMOS.

TINJAUAN:

- Gerbang logika CMOS terbuat dari transistor IGFET (MOSFET) daripada transistor sambungan bipolar.

- Masukan gerbang CMOS sensitif terhadap listrik statis. Mereka mungkin rusak oleh tegangan tinggi, dan mereka dapat mengasumsikan level logika apa pun jika dibiarkan mengambang.

- Tarik dan tarik turun resistor digunakan untuk mencegah input gerbang CMOS mengambang jika digerakkan oleh sumber sinyal yang hanya mampu mengalirkan atau menenggelamkan arus.

- Gerbang CMOS mengeluarkan daya yang jauh lebih sedikit daripada gerbang TTL yang setara, tetapi disipasi dayanya meningkat seiring dengan frekuensi sinyal, sedangkan disipasi daya gerbang TTL kira-kira konstan pada berbagai kondisi pengoperasian.

- Masukan gerbang CMOS menarik arus yang jauh lebih sedikit daripada masukan TTL, karena MOSFET adalah perangkat yang dikendalikan tegangan, bukan arus.

- Gerbang CMOS dapat beroperasi pada rentang tegangan catu daya yang jauh lebih luas daripada TTL:biasanya 3 hingga 15 volt versus 4,75 hingga 5,25 volt untuk TTL.

- Gerbang CMOS cenderung memiliki frekuensi operasi maksimum yang jauh lebih rendah daripada gerbang TTL karena kapasitansi input yang disebabkan oleh gerbang MOSFET.

- Seri-B Gerbang CMOS memiliki output "buffered" untuk meningkatkan penguatan tegangan dari input ke output, menghasilkan respons output yang lebih cepat terhadap perubahan sinyal input. Ini membantu mengatasi kelambatan bawaan gerbang CMOS karena kapasitansi input MOSFET dan konstanta waktu RC yang dihasilkan.

LEMBAR KERJA TERKAIT: