Teknologi Industri

Register geser, seperti penghitung, adalah bentuk logika sekuensial .

Logika sekuensial, tidak seperti logika kombinasional, tidak hanya dipengaruhi oleh input saat ini, tetapi juga oleh riwayat sebelumnya.

Dengan kata lain, logika sekuensial mengingat peristiwa masa lalu.

Shift register menghasilkan penundaan diskrit dari sinyal digital atau bentuk gelombang.

Bentuk gelombang yang disinkronkan ke jam , gelombang persegi berulang, ditunda oleh “n” waktu jam diskrit, di mana “n” adalah jumlah tahapan register geser.

Dengan demikian, register geser empat tahap menunda "data masuk" sebanyak empat jam menjadi "data keluar".

Tahapan dalam register geser adalah tahap penundaan , biasanya ketik “D” Flip-Flop atau ketik “JK” Sandal jepit.

Sebelumnya, register geser yang sangat panjang (beberapa ratus tahap) berfungsi sebagai memori digital.

Aplikasi usang ini mengingatkan pada jalur tunda merkuri akustik yang digunakan sebagai memori komputer awal.

Transmisi data serial, melalui jarak meter hingga kilometer, menggunakan register geser untuk mengubah data paralel menjadi bentuk serial.

Komunikasi data serial menggantikan banyak kabel data paralel lambat dengan satu rangkaian kecepatan tinggi serial.

Data serial pada jarak pendek puluhan sentimeter, menggunakan register geser untuk memasukkan dan mengeluarkan data dari mikroprosesor.

Banyak periferal, termasuk konverter analog ke digital, konverter digital ke analog, driver tampilan, dan memori, menggunakan register geser untuk mengurangi jumlah kabel di papan sirkuit.

Beberapa sirkuit pencacah khusus sebenarnya menggunakan register geser untuk menghasilkan bentuk gelombang berulang.

Register geser yang lebih panjang, dengan bantuan umpan balik menghasilkan pola yang sangat panjang sehingga terlihat seperti noise acak, pseudo-noise .

Register geser dasar diklasifikasikan berdasarkan struktur menurut tipe berikut:

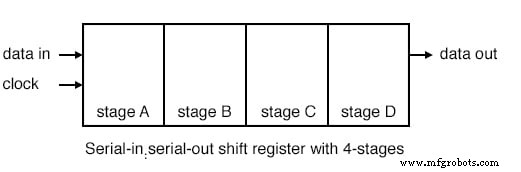

Di atas kami menunjukkan diagram blok register geser serial-in/serial-out, yang panjangnya 4 tahap.

Data pada input akan ditunda empat periode clock dari input ke output register geser.

Data di “data in”, di atas, akan ada di Tahap A output setelah pulsa clock pertama. Setelah tahap denyut nadi kedua A data ditransfer ke tahap B output, dan "data masuk" ditransfer ke tahap A keluaran. Setelah jam ketiga, panggung C digantikan oleh tahap B; tahap B digantikan oleh tahap A; dan tahap A diganti dengan “data masuk”.

Setelah jam keempat, data yang semula ada pada “data masuk” berada pada tahap D , “keluaran”.

Data "masuk pertama" adalah "keluar pertama" karena digeser dari "data masuk" menjadi "data keluar".

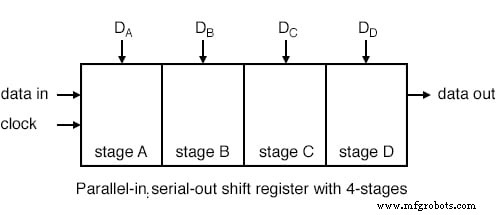

Data dimuat ke semua tahapan sekaligus dari register geser paralel-in/serial-out.

Data kemudian digeser keluar melalui "data out" oleh pulsa clock. Karena register geser 4 tahap ditunjukkan di atas, empat pulsa clock diperlukan untuk memindahkan semua data.

Pada diagram di atas, tahap D data akan hadir pada "data keluar" hingga pulsa clock pertama; tahap C data akan hadir pada "data keluar" antara jam pertama dan pulsa jam kedua; tahap B data akan hadir antara jam kedua dan jam ketiga; dan panggung A data akan ditampilkan antara jam ketiga dan keempat.

Setelah pulsa clock keempat dan setelahnya, bit berturut-turut dari "data masuk" akan muncul di "data keluar" dari register geser setelah penundaan empat pulsa clock.

Jika empat sakelar terhubung ke DA melalui DD , statusnya dapat dibaca ke dalam mikroprosesor hanya dengan menggunakan satu pin data dan satu pin jam.

Karena menambahkan lebih banyak sakelar tidak memerlukan pin tambahan, pendekatan ini terlihat menarik untuk banyak masukan.

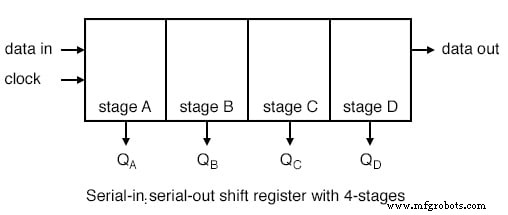

Di atas, empat bit data akan digeser dari "data masuk" oleh empat pulsa clock dan tersedia di QA melalui QD untuk menggerakkan sirkuit eksternal seperti LED, lampu, driver relai, dan klakson. Setelah jam pertama, data di “data masuk” muncul di QA .

Setelah jam kedua, QA old yang lama data muncul di QB; TJ menerima data berikutnya dari "data masuk". Setelah jam ketiga, QB data ada di QC .

Setelah jam keempat, QC data ada di QD . Tahap ini berisi data yang pertama kali hadir pada “data in”. Register geser sekarang harus berisi empat bit data.

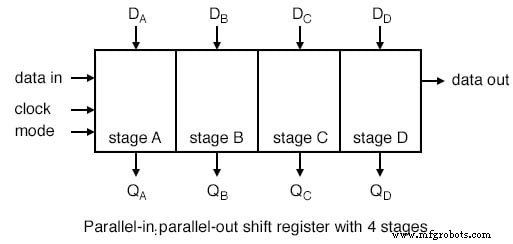

Register geser paralel-in/parallel-out menggabungkan fungsi register geser paralel-in, serial-out dengan fungsi register geser serial-in, paralel-out untuk menghasilkan register geser universal.

Pergeseran "lakukan apa saja" ada harganya– peningkatan jumlah pin I/O (Input/Output) dapat mengurangi jumlah tahapan yang dapat dikemas.

Data disajikan di DA melalui DD paralel dimuat ke dalam register.

Data ini di QA melalui QD dapat digeser oleh jumlah pulsa yang ditampilkan pada input jam.

Data yang digeser tersedia di QA melalui QD .

Input “mode”, yang mungkin lebih dari satu input, mengontrol pemuatan data paralel dari DA melalui DD , perpindahan data, dan arah perpindahan.

Ada register geser yang akan menggeser data ke kiri atau ke kanan.

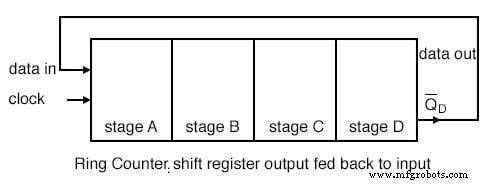

Jika output serial dari register geser terhubung ke input serial, data dapat terus-menerus digeser di sekitar ring selama pulsa clock ada.

Jika output dibalik sebelum diumpankan kembali seperti yang ditunjukkan di atas, kita tidak perlu khawatir memuat data awal ke dalam “ring counter”.

LEMBAR KERJA TERKAIT:

Teknologi Industri

Komponen dan persediaan Arduino Nano R3 × 1 Texas Instruments Shift Register- Serial to Parallel 74HC595 × 4 Ukuran Penuh Papan Tempat Memotong Roti Tanpa Solder × 1 LED (generik) Tergantung pada preferensi Anda. × 1 Resistor 100 ohm Tergantung pada LED

Apa itu Ilmu Data? Ilmu Data adalah bidang interdisipliner yang melibatkan penggunaan metode, proses, dan sistem ilmiah untuk mengumpulkan, menyiapkan, dan menganalisis data dalam bentuk terstruktur dan tidak terstruktur. Ilmu data memanfaatkan berbagai bidang termasuk matematika, statistik, databa

Apa itu Li-Fi? Li-Fi (juga dikenal sebagai light fidelity) adalah teknologi untuk transmisi data nirkabel antar perangkat Li-Fi menggunakan cahaya sebagai media untuk transmisi data. Lampu LED adalah sumber yang digunakan untuk pengkodean data dengan menyalakan dan mematikan lampu secara berkala u

Pengantar Halo semuanya, saya akan berbicara tentang runtime straton dan lingkungan pemrogramannya di sekitar standar IEC61850. Waktu proses ini mengikuti standar Edisi 2, sebuah protokol yang sedang berevolusi penuh di bidang energi. Di masa lalu, Phoenix Contact telah mengembangkan tump