gerbang TTL NAND dan AND

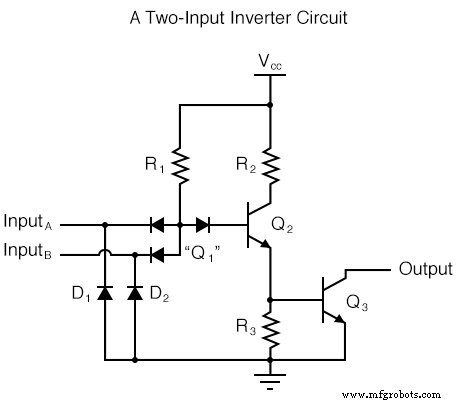

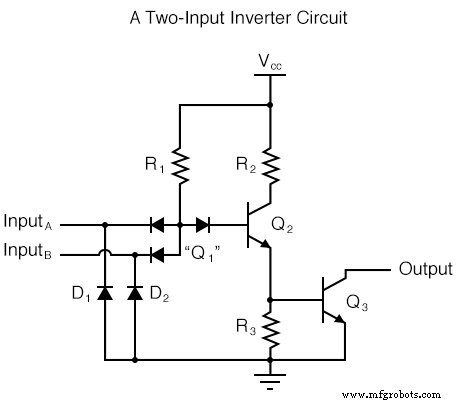

Misalkan kita mengubah rangkaian inverter kolektor terbuka dasar kita, menambahkan terminal input kedua seperti yang pertama:

Skema ini menggambarkan rangkaian nyata, tetapi tidak disebut "inverter dua input." Melalui analisis, kita akan menemukan apa fungsi logika Sirkuit ini dan dengan demikian harus ditunjuk sebagai apa.

Sama seperti dalam kasus inverter dan buffer, cluster dioda "kemudi" bertanda "Q1" sebenarnya dibentuk seperti transistor, meskipun tidak digunakan dalam kapasitas penguatan apa pun. Sayangnya, struktur transistor NPN sederhana tidak cukup untuk mensimulasikan tiga Sambungan PN diperlukan dalam jaringan dioda ini, sehingga diperlukan transistor (dan simbol) yang berbeda.

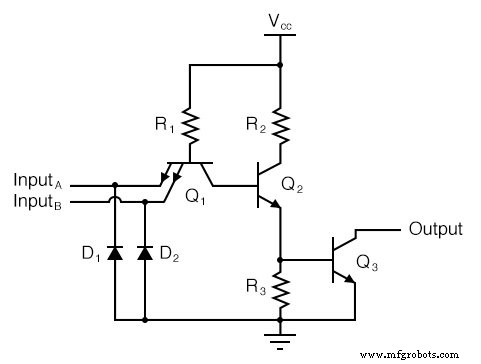

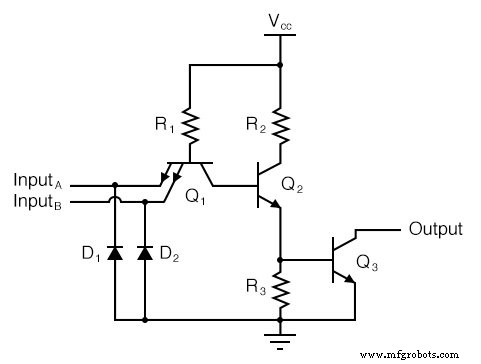

Transistor ini memiliki satu kolektor, satu basis, dan dua emitor, dan di sirkuit, terlihat seperti ini:

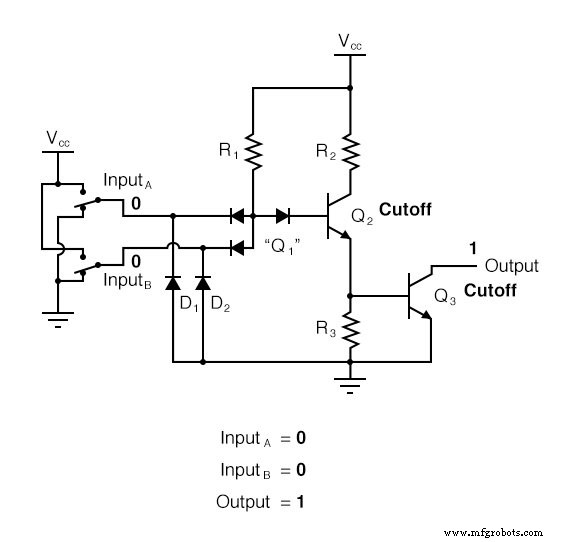

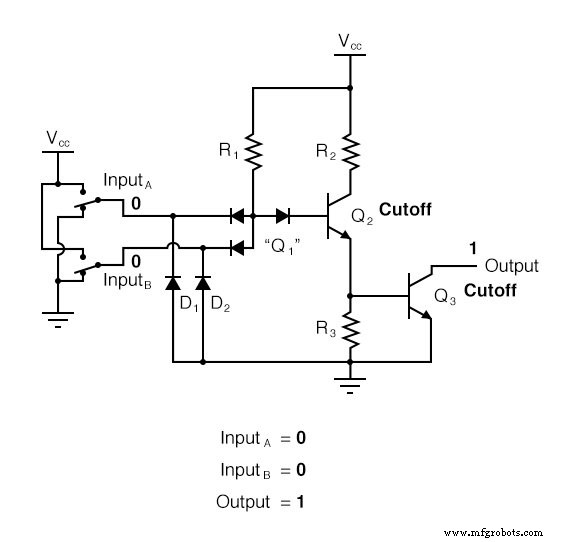

Dalam rangkaian input tunggal (inverter), pengardean input menghasilkan output yang mengasumsikan status "tinggi" (1). Dalam kasus konfigurasi keluaran kolektor terbuka, status "tinggi" ini hanya "mengambang".

Membiarkan input mengapung (atau dihubungkan ke Vcc) mengakibatkan output menjadi ground, yang merupakan status "rendah" atau 0. Jadi, 1 masuk menghasilkan 0 keluar, dan sebaliknya.

Ilustrasi Sirkuit untuk Status Input

Karena rangkaian ini sangat mirip dengan rangkaian inverter sederhana, satu-satunya perbedaan adalah terminal input kedua yang terhubung dengan cara yang sama ke basis transistor Q2, kita dapat mengatakan bahwa masing-masing input akan memiliki efek yang sama pada output.

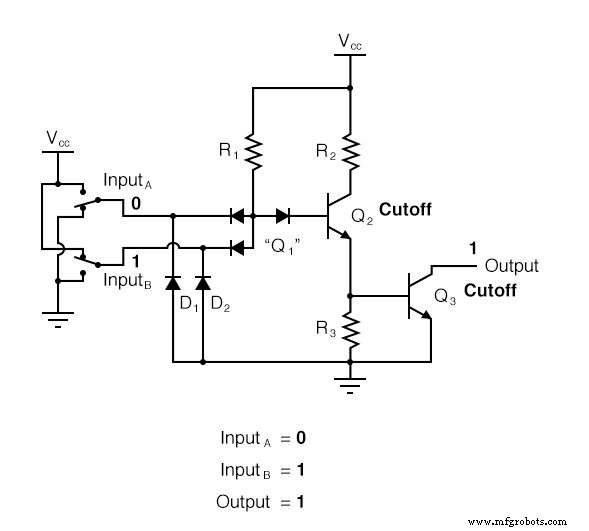

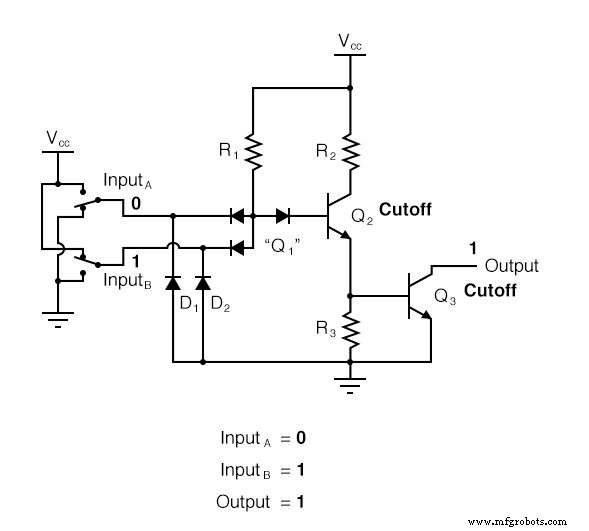

Yaitu, jika salah satu input di-ground, transistor Q2 akan dipaksa ke dalam kondisi cutoff, sehingga mematikan Q3 dan output mengambang (output menjadi "tinggi"). Rangkaian ilustrasi berikut menunjukkan ini untuk tiga status input (00, 01, dan 10):

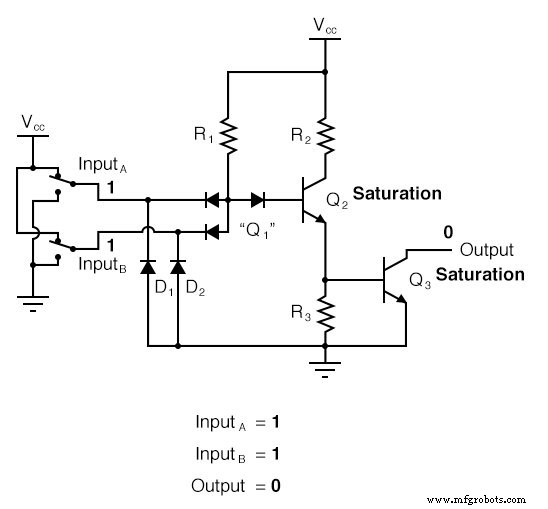

Bagaimanapun, di mana ada input yang di-ground ("rendah"), output dijamin mengambang ("tinggi"). Sebaliknya, satu-satunya waktu output akan menjadi "rendah" adalah jika transistor Q3 menyala, yang berarti transistor Q2 harus dihidupkan (jenuh), yang berarti tidak ada input yang dapat mengalihkan arus R1 menjauh dari basis Q2.

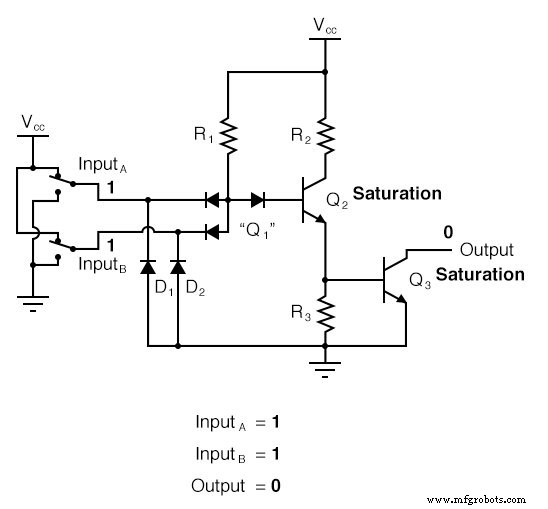

Satu-satunya kondisi yang akan memenuhi persyaratan ini adalah ketika kedua input "tinggi" (1):

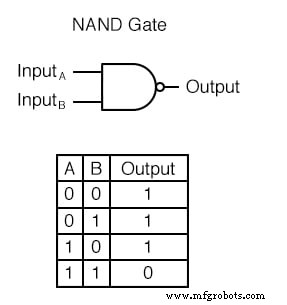

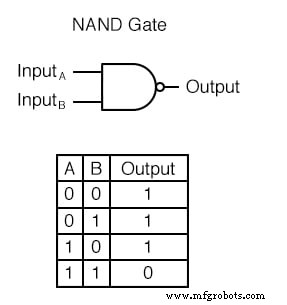

Gerbang NAND

Mengumpulkan dan mentabulasi hasil ini ke dalam tabel kebenaran, kita melihat bahwa polanya cocok dengan pola gerbang NAND:

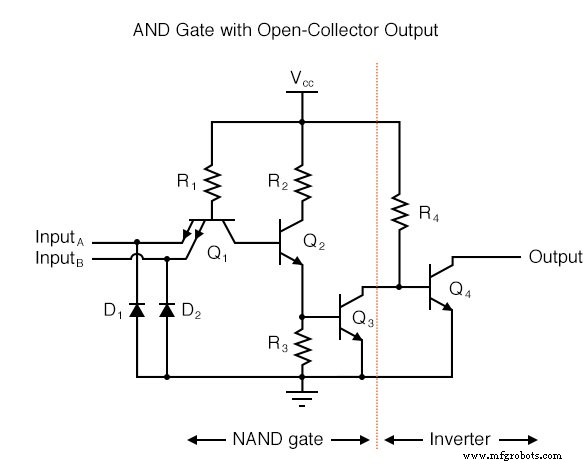

Pada bagian sebelumnya tentang gerbang NAND, jenis gerbang ini dibuat dengan mengambil gerbang AND dan meningkatkan kompleksitasnya dengan menambahkan inverter (gerbang NOT) ke output. Namun, ketika kami memeriksa sirkuit ini, kami melihat bahwa fungsi NAND sebenarnya adalah mode operasi paling sederhana dan paling alami untuk desain TTL ini.

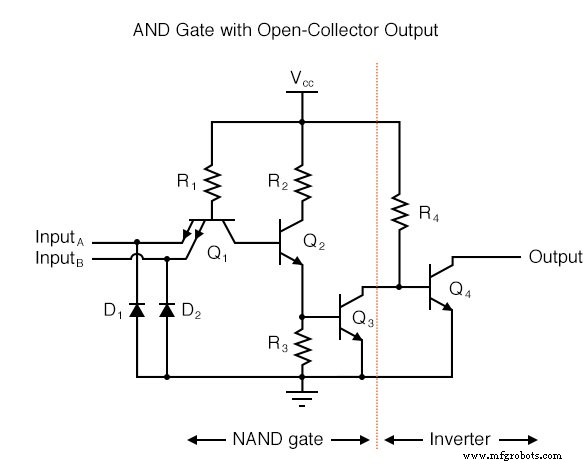

Untuk membuat fungsi AND menggunakan sirkuit TTL, kita perlu meningkatkan rumitnya rangkaian ini dengan menambahkan stage inverter pada outputnya, sama seperti kita harus menambahkan stage transistor tambahan pada rangkaian inverter TTL untuk mengubahnya menjadi buffer:

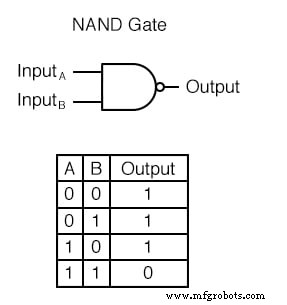

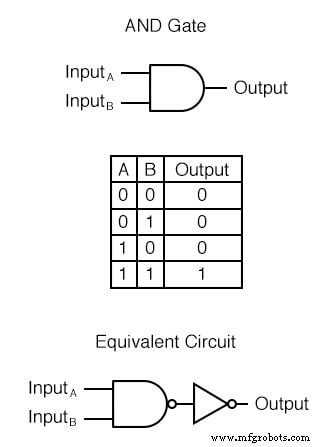

Gerbang DAN

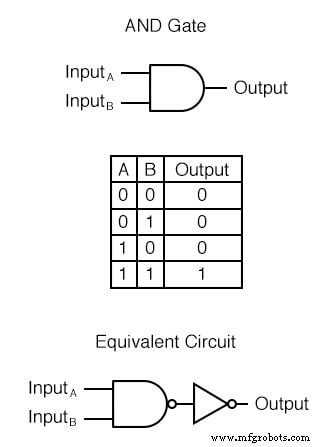

Tabel kebenaran dan rangkaian gerbang ekivalen (gerbang NAND keluaran terbalik) ditunjukkan di sini:

Tentu saja, baik sirkuit gerbang NAND maupun AND dapat dirancang dengan tahap keluaran tiang totem daripada kolektor terbuka. Saya memilih untuk menampilkan versi kolektor terbuka demi kesederhanaan.

TINJAUAN:

- Gerbang NAND TTL dapat dibuat dengan mengambil rangkaian inverter TTL dan menambahkan input lain.

- Gerbang AND dapat dibuat dengan menambahkan tahap inverter ke output rangkaian gerbang NAND.

LEMBAR KERJA TERKAIT: