Variabel - Contoh VHDL

Variabel dalam VHDL bertindak mirip dengan variabel dalam C. Nilainya valid di lokasi yang tepat dalam kode di mana variabel dimodifikasi. Oleh karena itu, jika sinyal menggunakan nilai variabel sebelum tugas, itu akan memiliki nilai variabel lama. Jika sinyal menggunakan nilai variabel setelah tugas itu akan memiliki nilai variabel baru.

Aturan Variabel:

- Variabel hanya dapat digunakan di dalam proses

- Variabel apa pun yang dibuat dalam satu proses tidak dapat digunakan di proses lain

- Variabel perlu didefinisikan setelah kata kunci proses tapi sebelum kata kunci dimulai

- Variabel ditetapkan menggunakan := simbol tugas

- Variabel yang ditugaskan langsung mengambil nilai dari tugas tersebut

Hal yang paling penting untuk dipahami adalah bahwa variabel segera mengambil nilai dari tugasnya. Berikut adalah contoh yang menunjukkan satu cara yang berguna untuk menggunakan variabel:menyimpan data untuk penggunaan sementara . Ini menggunakan pernyataan kasus dan operator rangkaian ampersand (&).

VAR_CASE : process (i_clk)

variable v_Choices : std_logic_vector(1 downto 0);

begin

v_Choices := i_select_1 & i_select_2; -- concatenation

case v_Choices is

when "00" =>

o_data <= "0001";

when "01" =>

o_data <= "0010";

-- ETC

Dalam contoh sebelumnya, kami menggabungkan dua sinyal sehingga mereka dapat digunakan dalam pernyataan kasus. Variabel v_Choices segera tersedia untuk digunakan segera setelah ditetapkan. Mari kita lihat contoh lain. Contoh di bawah ini lebih komprehensif dan menunjukkan bagaimana variabel segera mengambil nilai tugasnya. Sinyal r_Var_Copy1 dan r_Var_Copy2 tampaknya sama, tetapi r_Var_Copy2 tidak pernah bisa mencapai 5 sebelum disetel ulang.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity variable_ex is

port (

i_clk : in std_logic;

o_done : out std_logic

);

end variable_ex;

architecture rtl of variable_ex is

signal r_Done : std_logic := '0';

signal r_Var_Copy1 : natural range 0 to 5 := 0;

signal r_Var_Copy2 : natural range 0 to 5 := 0;

begin

EX_VAR : process (i_clk)

variable v_Count : natural range 0 to 5 := 0;

begin

if rising_edge(i_clk) then

v_Count := v_Count + 1;

r_Var_Copy1 <= v_Count;

if v_Count = 5 then

r_Done <= '1';

v_Count := 0;

else

r_Done <= '0';

end if;

r_Var_Copy2 <= v_Count;

end if;

end process EX_VAR;

o_done <= r_Done;

end rtl;

Untuk mensimulasikan desain kita, kita perlu membuat testbench. Juga, variabel bisa sedikit rumit untuk ditampilkan dalam simulasi. Jika Anda menggunakan Modelsim, baca selengkapnya tentang cara melihat variabel Anda di jendela bentuk gelombang Modelsim.

Testbench:

library ieee;

use ieee.std_logic_1164.all;

entity variable_ex_tb is

end variable_ex_tb;

architecture behave of variable_ex_tb is

component variable_ex

port (

i_clk : in std_logic;

o_done : out std_logic

);

end component variable_ex;

constant c_CLK_PERIOD : time := 10 ns;

signal r_CLK : std_logic := '0';

signal w_DONE : std_logic;

begin

UUT : variable_ex

port map (

i_clk => r_CLK,

o_done => w_DONE

);

r_CLK <= not r_CLK after c_CLK_PERIOD/2;

end behave;

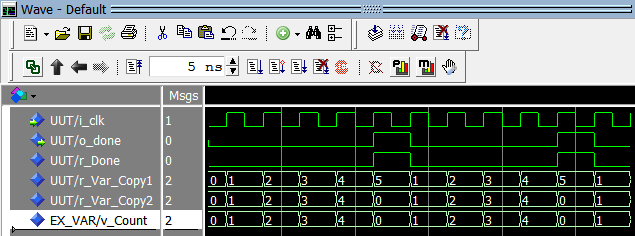

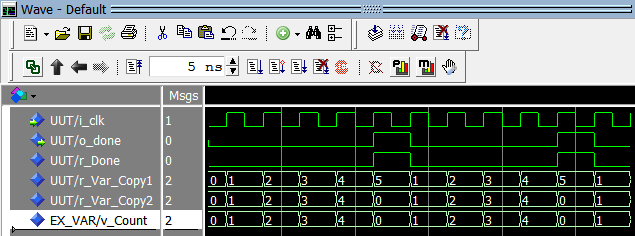

Contoh Variabel Bentuk Gelombang Testbench

Contoh di atas menunjukkan bagaimana variabel bertindak berbeda dari sinyal. Sinyal r_Var_Copy1 dan r_Var_Copy2 tampaknya sama, tetapi r_Var_Copy2 tidak pernah bisa mencapai 5 sebelum disetel ulang.

Contoh Variabel Bentuk Gelombang Testbench

Contoh Variabel Bentuk Gelombang Testbench