Alur Desain ASIC

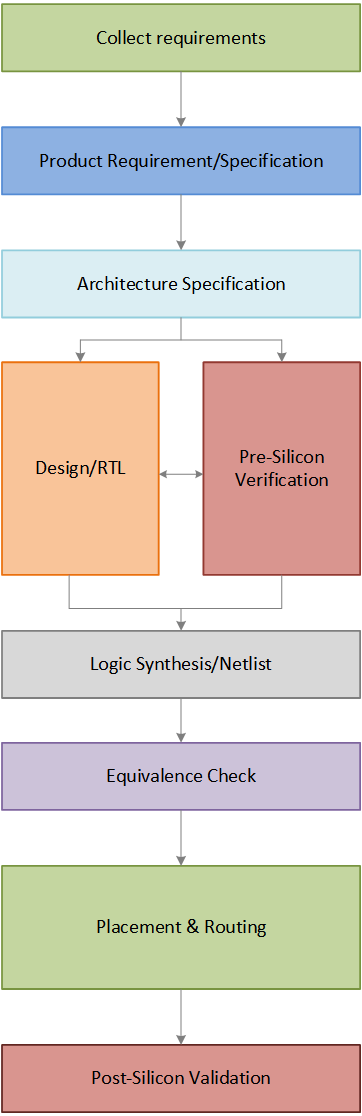

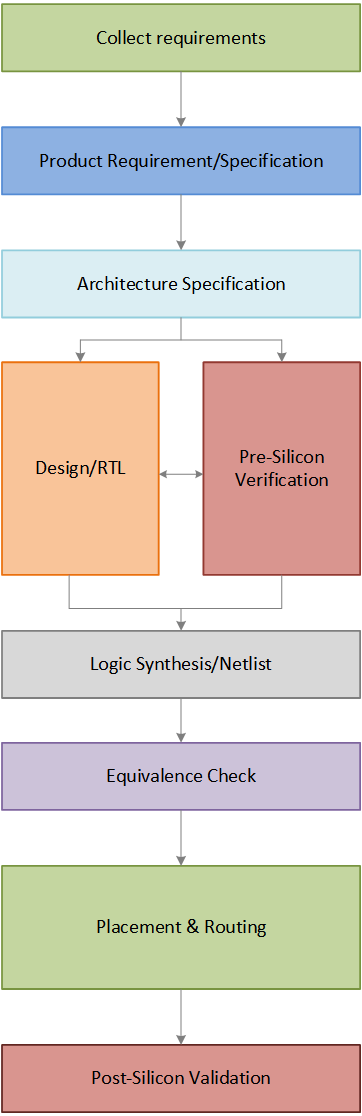

Aliran desain tipikal mengikuti struktur yang ditunjukkan di bawah ini dan dapat dipecah menjadi beberapa langkah. Beberapa fase ini terjadi secara paralel dan beberapa berurutan. Kita akan melihat bagaimana siklus desain proyek pada industri saat ini.

Persyaratan

Pelanggan perusahaan semikonduktor biasanya adalah perusahaan lain yang berencana menggunakan chip dalam sistem atau produk akhir mereka. Jadi, persyaratan pelanggan juga memainkan peran penting dalam memutuskan bagaimana chip harus dirancang. Secara alami, langkah pertama adalah mengumpulkan persyaratan, memperkirakan nilai pasar produk akhir, dan mengevaluasi jumlah sumber daya yang diperlukan untuk melakukan proyek.

Spesifikasi

Langkah selanjutnya adalah mengumpulkan "spesifikasi" yang menggambarkan secara abstrak fungsionalitas, antarmuka, dan arsitektur keseluruhan dari chip yang akan dirancang. Ini bisa berupa sesuatu seperti:

- Memerlukan daya komputasi untuk menjalankan algoritme pencitraan untuk mendukung realitas virtual

- Memerlukan dua prosesor ARM A53 dengan interkoneksi yang koheren dan harus berjalan pada 600 MHz

- Memerlukan antarmuka USB 3.0, Bluetooth, dan PCIe generasi ke-2

- Harus mendukung tampilan 1920x1080 piksel dengan pengontrol yang sesuai

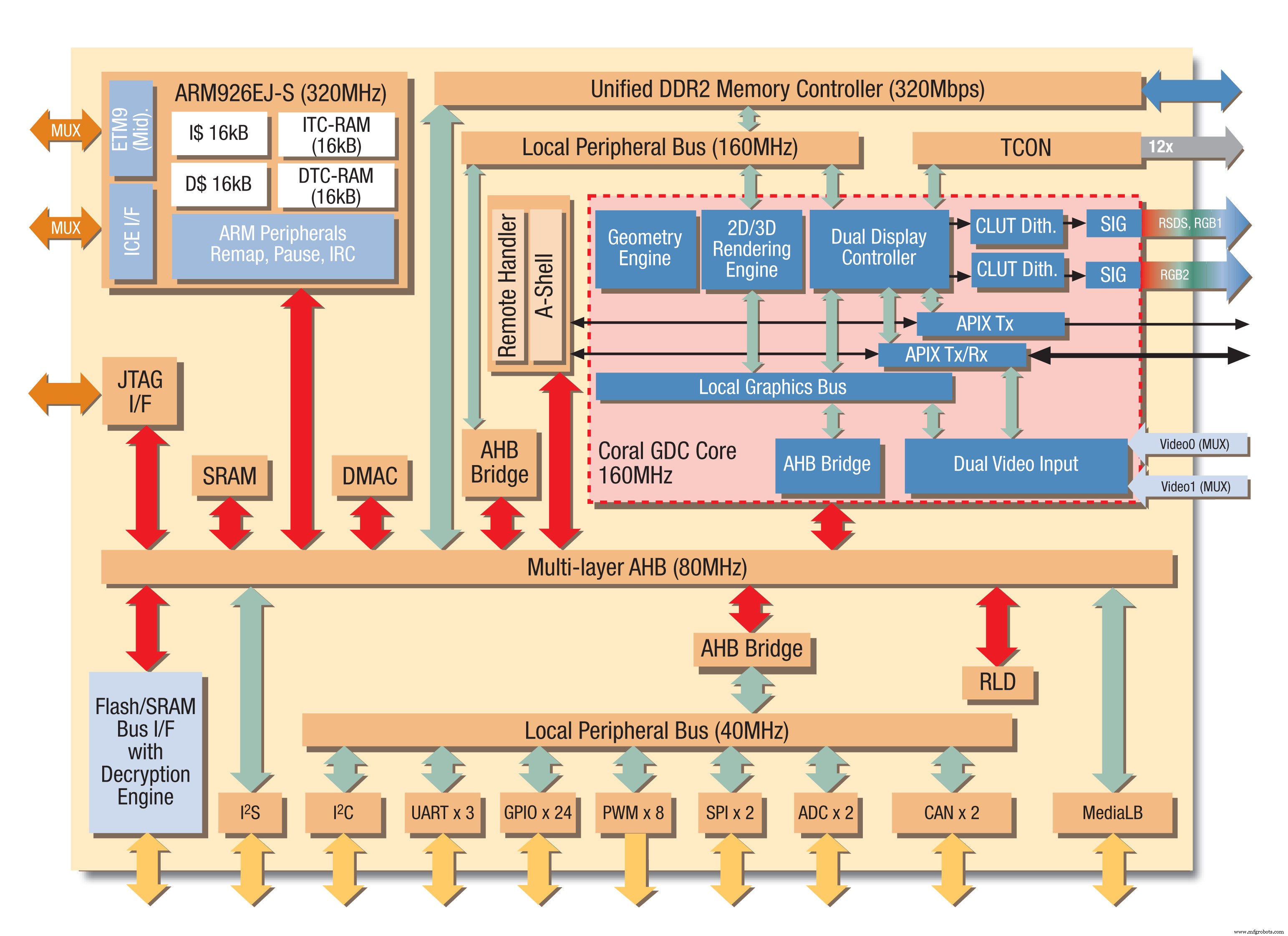

Arsitektur

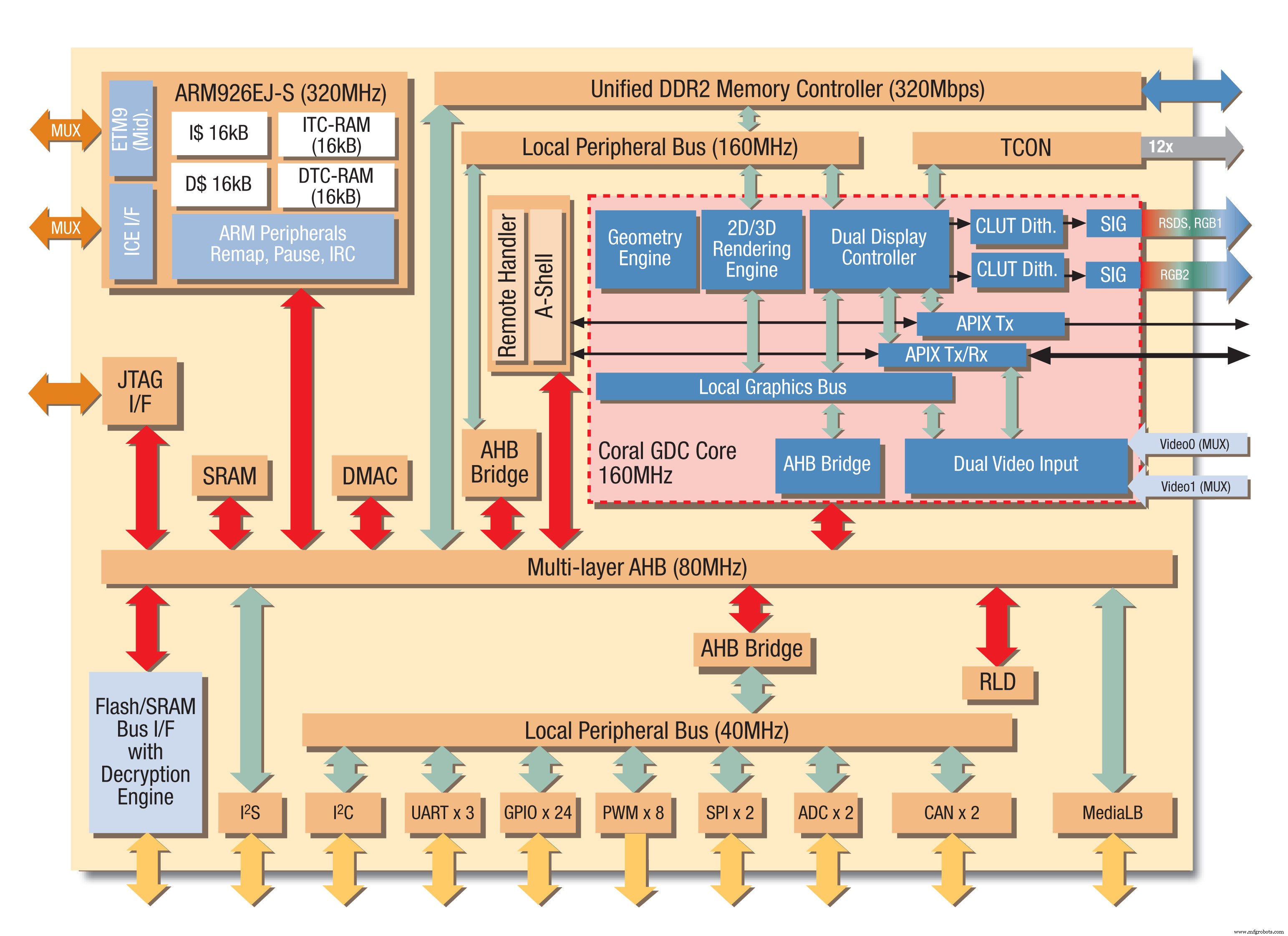

Sekarang, para arsitek datang dengan tampilan tingkat sistem tentang bagaimana chip harus beroperasi. Mereka akan memutuskan semua komponen lain yang diperlukan, frekuensi clock apa yang harus dijalankan, dan bagaimana menargetkan persyaratan daya dan kinerja. Mereka juga memutuskan bagaimana data harus mengalir di dalam chip. Contohnya adalah aliran data ketika prosesor mengambil data pencitraan dari ram sistem dan menjalankannya. Sementara itu, mesin grafis akan mengeksekusi data pasca-proses dari kumpulan sebelumnya yang dibuang ke bagian lain dari memori dan seterusnya.

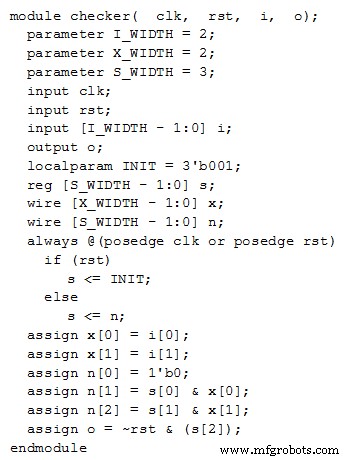

Desain Digital

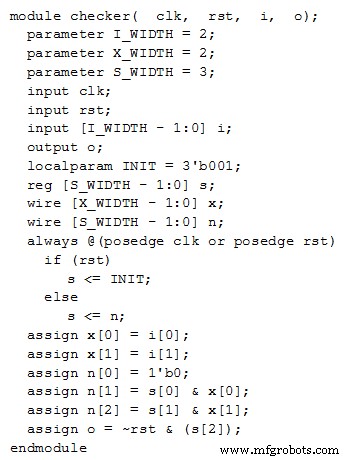

Karena sifat kompleks dari chip modern, tidak mungkin untuk membangun sesuatu dari awal, dan dalam banyak kasus, banyak komponen akan digunakan kembali. Katakanlah perusahaan X memerlukan modul FlexCAN untuk berinteraksi dengan modul lain di dalam mobil. Mereka dapat membeli desain FlexCAN dari perusahaan lain untuk menghemat waktu dan tenaga atau menghabiskan sumber daya untuk membangunnya sendiri. Juga, tidak praktis untuk merancang sistem seperti itu dari blok bangunan dasar seperti sandal jepit dan transistor CMOS. Sebagai gantinya, deskripsi perilaku dikembangkan untuk menganalisis desain dalam hal fungsionalitas, kinerja, dan masalah tingkat tinggi lainnya menggunakan Bahasa Deskripsi Perangkat Keras seperti Verilog atau VHDL. Ini biasanya dilakukan oleh perancang digital dan mirip dengan pemrogram komputer tingkat tinggi yang dilengkapi dengan keterampilan dalam elektronik digital.

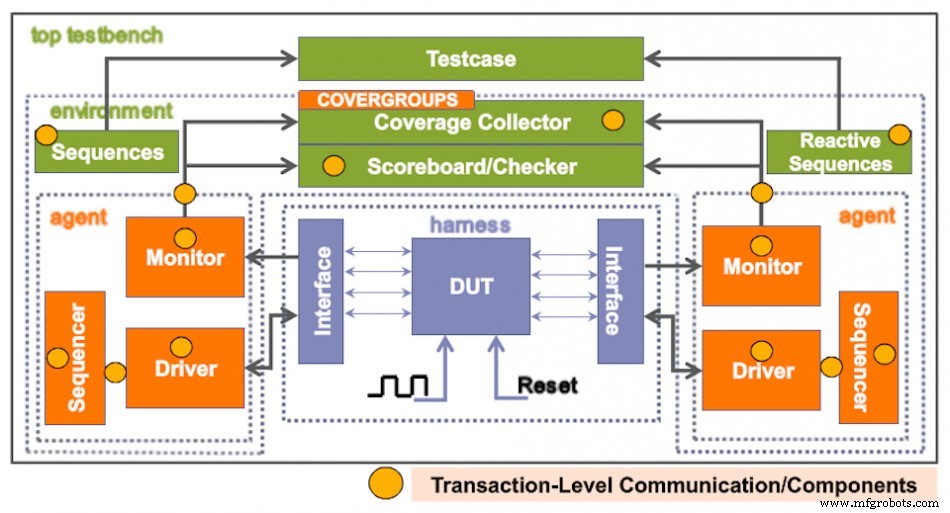

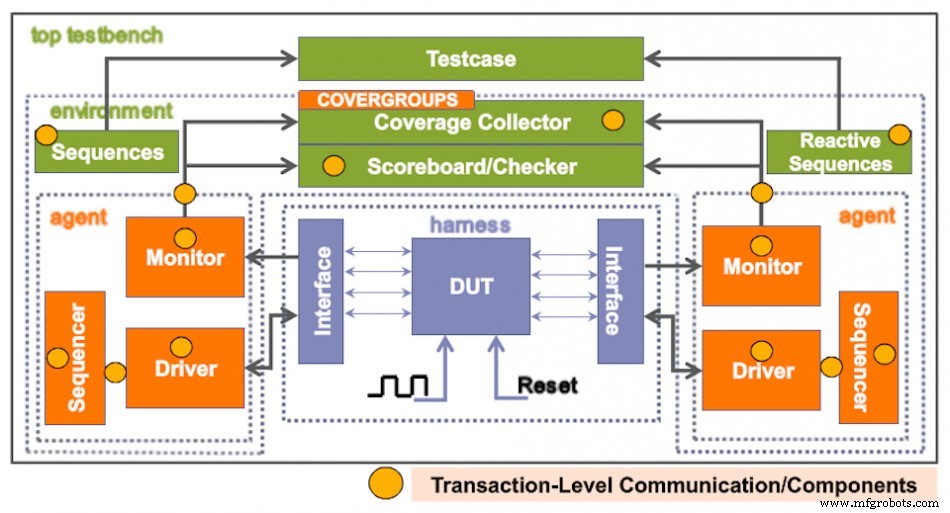

Verifikasi

Setelah desain RTL siap, perlu diverifikasi kebenaran fungsinya. Misalnya, prosesor DSP diharapkan mengeluarkan transaksi bus untuk mengambil instruksi dari memori, tetapi bagaimana kita tahu bahwa ini akan terjadi seperti yang diharapkan? Jadi, verifikasi fungsional diperlukan pada titik ini, yang dilakukan dengan bantuan simulator EDA yang memiliki kemampuan untuk memodelkan desain dan menerapkan stimulus yang berbeda padanya. Ini adalah pekerjaan seorang insinyur verifikasi pra-silikon.

Untuk menghemat waktu dan mencapai penutupan fungsional, baik tim desain dan verifikasi beroperasi secara paralel di mana desainer "melepaskan" versi RTL, dan tim verifikasi mengembangkan lingkungan testbench dan kasus uji untuk menguji fungsionalitas versi RTL tersebut. Jika salah satu dari tes ini gagal, maka itu mungkin menunjukkan masalah dengan desain dan "bug" akan muncul pada elemen desain itu. Bug ini harus diperbaiki pada rilis RTL versi berikutnya dari tim desain. Proses ini berlangsung sampai ada tingkat kepercayaan yang baik dalam kebenaran fungsional desain.

Sintesis Logika

Sekarang setelah kita puas dengan desainnya, saatnya mengubahnya menjadi skema perangkat keras dengan elemen nyata seperti gerbang kombinasional dan sandal jepit. Langkah ini disebut sebagai sintesis. Alat sintesis logika memungkinkan konversi deskripsi RTL dalam HDL ke netlist tingkat gerbang. Netlist ini tidak lain adalah deskripsi sirkuit dalam hal gerbang dan koneksi di antara mereka. Itu bisa terlihat seperti:

and_2_0 u_and2_0 ( .in_a (_net_112),

.in_b (_net_56),

.out (_net_222));

ff_lt u_ff_lt_122 (.d (_net_222),

.clk (_net_11),

.q (_net_76));

Alat sintesis logika memastikan bahwa netlist memenuhi spesifikasi waktu, area, dan daya. Biasanya mereka memiliki akses ke proses node teknologi yang berbeda dan perpustakaan elemen digital dan dapat membuat perhitungan cerdas untuk memenuhi semua kriteria yang berbeda ini. Pustaka ini diperoleh dari fab semikonduktor yang menyediakan karakteristik data untuk komponen yang berbeda seperti waktu naik/turun untuk flip-flop, waktu input-output untuk gerbang kombinasional, dll.

Kesetaraan Logika

Netlist level gerbang kemudian diperiksa untuk kesetaraan logis dengan RTL, dan terkadang "verifikasi level gerbang" dilakukan di mana verifikasi elemen tertentu dilakukan sekali lagi, perbedaannya adalah kali ini di level gerbang dan di level yang lebih rendah dari abstraksi. Waktu simulasi cenderung lebih lambat karena banyaknya elemen yang terlibat dalam desain pada tahap ini bersama dengan informasi penundaan beranotasi belakang.

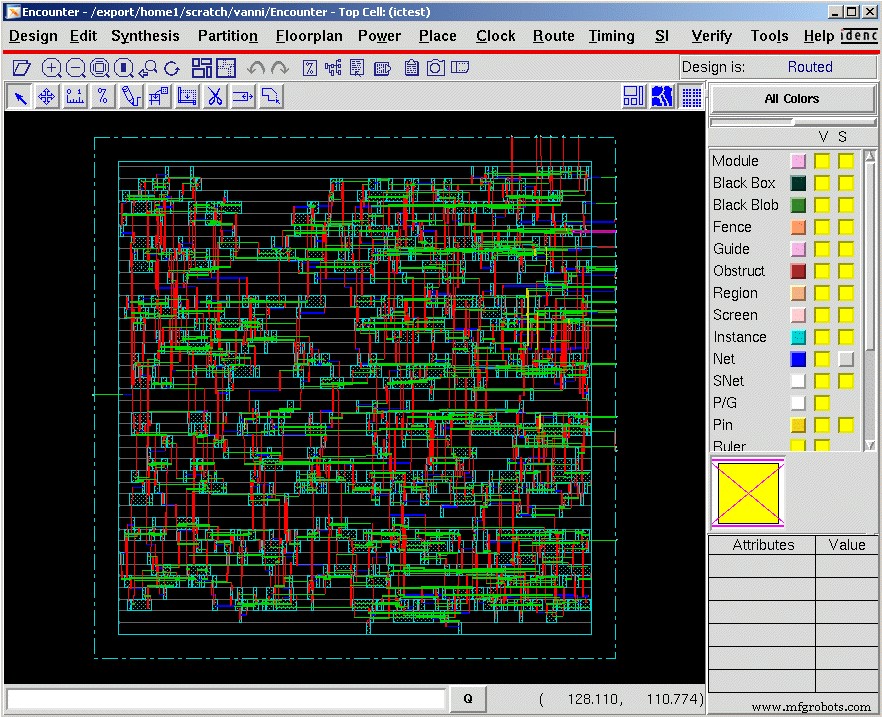

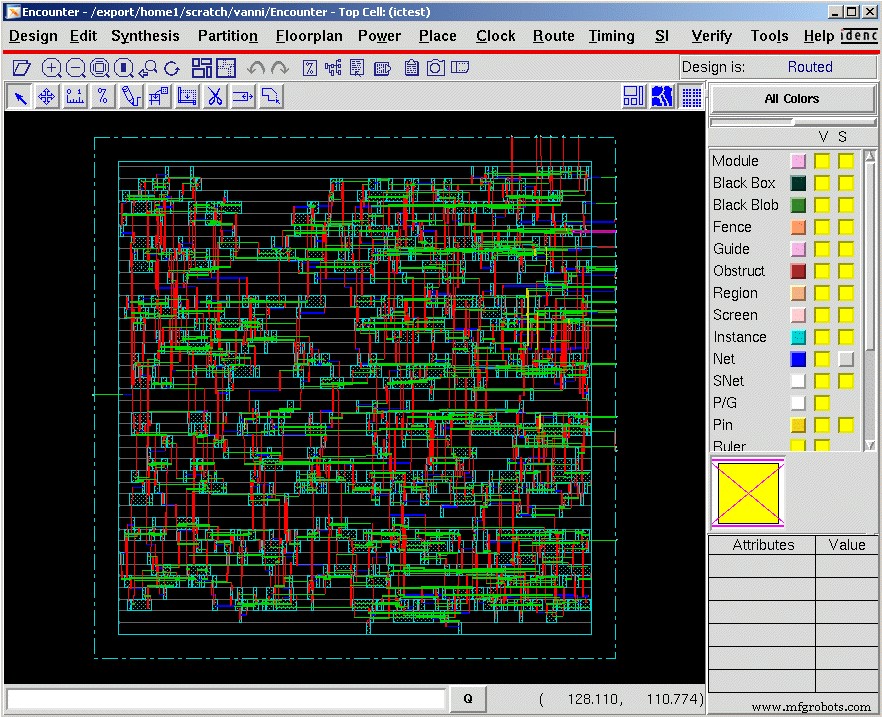

Penempatan dan Perutean

Netlist tersebut kemudian dimasukkan ke dalam alur desain fisik, dimana tempat dan rute otomatis (APR atau PnR) dilakukan dengan bantuan alat EDA. Contoh yang baik dari alat tersebut adalah Cadence Encounter dan Synopsys IC Compiler. Ini akan memilih dan menempatkan sel standar ke dalam baris, menentukan peta bola untuk input-output, membuat lapisan logam yang berbeda, dan menempatkan buffer untuk memenuhi waktu. Setelah proses ini selesai, tata letak dibuat dan biasanya dikirim untuk fabrikasi. Tahap ini biasanya ditangani oleh tim desain fisik yang berpengalaman dengan node teknologi dan detail implementasi fisik.

Validasi

Itu tidak berakhir di sini. Sebuah chip sampel akan dibuat baik oleh perusahaan semikonduktor yang sama atau dikirim ke pengecoran pihak ketiga seperti TSMC atau Global Foundries. Sampel ini sekarang melalui proses validasi pasca-silikon di mana tim insinyur lain menjalankan pola yang berbeda pada penguji. Jauh lebih sulit untuk men-debug dalam validasi pasca-silikon daripada verifikasi pra-silikon hanya karena tingkat visibilitas ke dalam simpul internal sebuah chip berkurang secara drastis. Selain itu, satu juta siklus jam akan selesai dalam satu detik dan menelusuri kembali ke waktu kesalahan yang tepat akan memakan waktu. Jika ada masalah nyata atau bug desain yang ditemukan pada tahap ini, maka ini harus diperbaiki di RTL, diverifikasi ulang dan semua langkah selanjutnya harus dilakukan.

Meskipun ada beberapa langkah dalam aliran desain, banyak aktivitas desain biasanya terkonsentrasi pada optimasi dan verifikasi deskripsi RTL sirkuit. Penting untuk dicatat bahwa meskipun alat EDA tersedia untuk mengotomatisasi proses, penggunaan yang tidak tepat akan menyebabkan desain yang tidak efisien dan karenanya seorang desainer harus membuat pilihan sadar selama proses desain.