Tertanam

Karena konverter analog-ke-digital (ADC) berkecepatan tinggi telah meningkat dalam laju pengambilan sampel, demikian juga masalah kesalahan kode — juga dikenal sebagai kode kilau — dalam data keluaran ADC. Kesalahan kode didefinisikan sebagai kesalahan dalam kode keluaran ADC yang melebihi ambang batas yang ditentukan. Ambang batas paling sering didefinisikan sebagai tingkat di mana kesalahan melebihi amplitudo yang diharapkan dari kebisingan ADC sehingga kesalahan dapat dengan mudah diidentifikasi dengan adanya kebisingan.

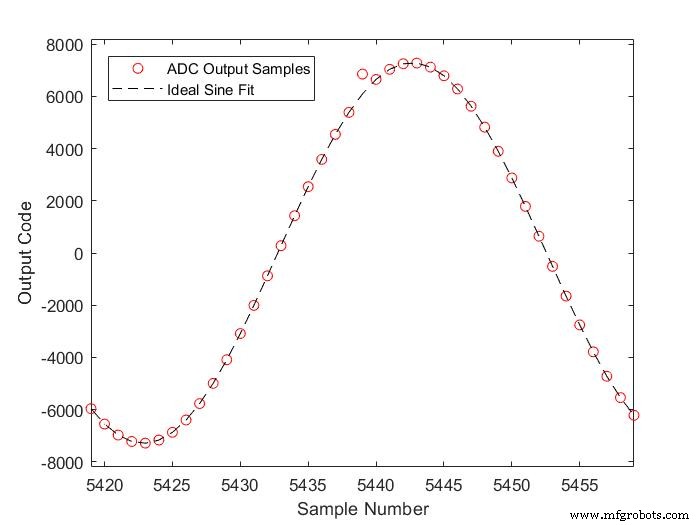

Cara lain untuk menjelaskan definisi ambang kesalahan ini adalah bahwa amplitudo kesalahan terjadi dengan probabilitas melebihi probabilitas yang diharapkan dari amplitudo tersebut dengan asumsi derau terdistribusi Gaussian ADC. Gambar 1 menunjukkan contoh kesalahan kode yang ditemukan dalam sampel keluaran ADC. Sampel yang salah terlihat jelas jika dibandingkan dengan fit gelombang sinus yang ideal dan jauh melebihi noise dari sampel lain dalam plot.

Gambar 1:Contoh keluaran ADC dengan kesalahan kode.

Tingkat kesalahan kode ADC (CER), juga kadang-kadang disebut tingkat kesalahan kata (WER) atau tingkat kesalahan metastabilitas, didefinisikan sebagai jumlah rata-rata kesalahan per sampel dan diukur dengan menghitung jumlah rata-rata sampel antara kesalahan berurutan. Ini paling sering didefinisikan sebagai urutan besarnya, seperti 10 –12 kesalahan/sampel. Waktu rata-rata antara kesalahan, oleh karena itu, tergantung pada laju sampling konverter. CER yang diukur hanya akurat ketika ADC berjalan pada laju pengambilan sampel di mana CER diukur. Secara umum, mengurangi laju pengambilan sampel dapat meningkatkan CER secara bertahap.

Mari kita lihat dari mana kesalahan kode berasal untuk melihat mengapa laju pengambilan sampel menjadi faktor utama.

Apa yang membuat ADC berkilau?

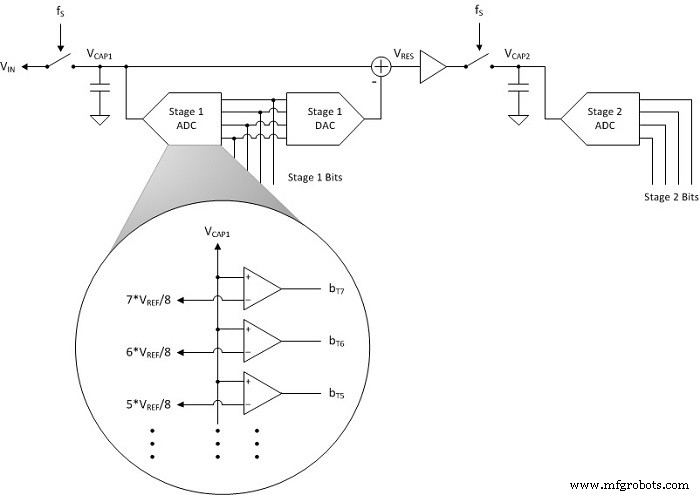

Arsitektur ADC multilangkah, seperti ADC flash pipelined atau ADC ADC, mengubah tegangan sampel menjadi bit digital secara bertahap, dan setiap tahap berurutan bergantung pada hasil tahap sebelumnya. Pertimbangkan ADC kecepatan tinggi flash pipelined dasar, seperti yang ditunjukkan pada Gbr. 2 . ADC yang disederhanakan ini menunjukkan dua tahap konversi di mana setiap tahap yang berurutan menghasilkan kode digital yang memperkirakan sinyal input dengan lebih halus.

Pengoperasian ADC yang ditampilkan adalah sebagai berikut:

Tahap pertama mengambil sampel tegangan input dan secara kasar mengubah sinyal input analog menjadi kode digital menggunakan ADC tahap pertama. Flash ADC pada tahap ini bekerja dengan membandingkan tegangan sampel dengan tegangan referensi statis, yang dihasilkan dari tegangan referensi utama ADC (V REF ), menggunakan komparator berkecepatan tinggi. Output dari komparator flash adalah sampel digital yang dikodekan dengan termometer yang mewakili tegangan input.

Kode termometer yang dikonversi kemudian dikirim langsung ke DAC tahap pertama. DAC ini mengeluarkan tegangan analog, yang sesuai dengan sampel yang dikonversi secara kasar.

Mengurangkan output DAC tahap pertama dari tegangan input asli menghasilkan tegangan kesalahan kuantisasi atau tegangan residu (V RES ). Residu tersebut kemudian diamplifikasi dan diambil sampelnya kembali (dipipihkan) untuk tahap kedua.

ADC tahap kedua mengkuantisasi V RES untuk mendapatkan perkiraan yang lebih akurat (resolusi lebih tinggi) dari tegangan input analog asli.

Gbr. 2:Contoh diagram blok arsitektur ADC flash pipelined.

V RES proses pembuatan memperkenalkan putaran keputusan berkecepatan tinggi. Dalam satu periode jam pengambilan sampel, tegangan sampel harus diubah menjadi kode digital oleh ADC tahap pertama. Kode digital harus dikeluarkan dari DAC tahap pertama, dikurangi dari tegangan input asli dan disampel ulang oleh tahap kedua. Loop keputusan berkecepatan tinggi menimbulkan kesalahan kode karena komparator dalam ADC flash memiliki waktu penyelesaian yang merupakan fungsi dari perbedaan antara tegangan sampel dan V REF .

Lebih sederhana, komparator membutuhkan waktu lebih lama untuk menyelesaikan ketika tegangan input (V CAP1 ) dekat dengan tegangan referensi (seperti 7 * V REF /8) dari pembanding. Secara teoritis, jika V CAP1 sangat dekat dengan tegangan referensi komparator, komparator tidak akan pernah menetap karena akan beroperasi di wilayah liniernya.

Kebisingan akan mencegah hal ini benar-benar terjadi, tetapi jika komparator terlalu lama untuk diselesaikan, maka DAC tahap pertama dapat menggunakan kode digital yang salah untuk mengeluarkan tegangan analog terkuantisasi. Hasilnya adalah V RES yang tidak cocok dengan kode keluaran digital ADC tahap pertama yang sebenarnya. ADC tahap kedua kemudian mengubah V RES yang salah , yang menghasilkan kesalahan kode.

Apa yang memengaruhi CER?

Anda sekarang harus memiliki cukup detail untuk dapat menarik beberapa kesimpulan tentang apa yang mempengaruhi CER. CER jelas tergantung pada laju pengambilan sampel. Tingkat pengambilan sampel yang lebih cepat mengurangi waktu di mana loop keputusan harus membuat keputusan. Lebih sedikit waktu untuk membuat keputusan menghasilkan peningkatan eksponensial dalam kemungkinan bahwa komparator tidak menyelesaikan tepat waktu.

–Matt Guibord adalah seorang insinyur sistem dalam konverter kecepatan tinggi di Texas Instruments.

Tertanam

Dari prototipe desain hingga bagian tubuh palsu, pencetakan 3D menciptakan kemungkinan baru di bidang manufaktur. Mesin cetak 3D saat ini memproduksi segala sesuatu mulai dari pengecoran pasir hingga implan gigi titanium dan bilah turbin. Bebek yang digambarkan di atas, Buttercup, lahir dengan kaki

Komponen dan persediaan Arduino UNO × 2 LED (generik) × 2 Resistor foto × 1 Buzzer × 1 Tentang proyek ini Saya mengajar kelas hari ini tentang Sistem Komunikasi dan ingin siswa saya belajar dengan memvisualisasikan dan mengalami. Kami melakuka

Definisi Kode QR Kode Respon Cepat, atau kode QR, menjadi lebih populer baik di dalam maupun di luar gudang dan fasilitas penyimpanan. Kode QR berasal dari Jepang dan digunakan untuk mengambil informasi tentang suatu barang atau bisnis dan memasukkannya ke dalam ponsel atau pemindai genggam. Kode QR

Alarm CNC dan Daftar kode kesalahan untuk mesin dan kontrol CNC, untuk membantu ahli mesin/pemrogram/penyetel CNC mempermudah pekerjaan mereka. Gambar:Action Machinery Co., Inc. Alarm Fanuc Daftar lengkap kode alarm Fanuc.Alarm Fanuc 11/10/12Alarm Fanuc Seri 15Alarm Fanuc 15iAlarm Fanuc 16i 18iAl