Teknologi Industri

Sirkuit gerbang logika dirancang untuk memasukkan dan mengeluarkan hanya dua jenis sinyal:"tinggi" (1) dan "rendah" (0), sebagaimana diwakili oleh tegangan variabel:tegangan catu daya penuh untuk keadaan "tinggi" dan tegangan nol untuk keadaan “rendah”. Di dunia yang sempurna, semua sinyal rangkaian logika akan ada pada batas tegangan ekstrem ini, dan tidak pernah menyimpang darinya (yaitu, kurang dari tegangan penuh untuk "tinggi", atau lebih dari nol tegangan untuk "rendah").

Namun, pada kenyataannya, level tegangan sinyal logika jarang mencapai batas sempurna ini karena penurunan tegangan yang menyimpang di sirkuit transistor, jadi kita harus memahami batasan level sinyal dari rangkaian gerbang saat mereka mencoba menafsirkan tegangan sinyal yang terletak di suatu tempat antara tegangan suplai penuh dan nol.

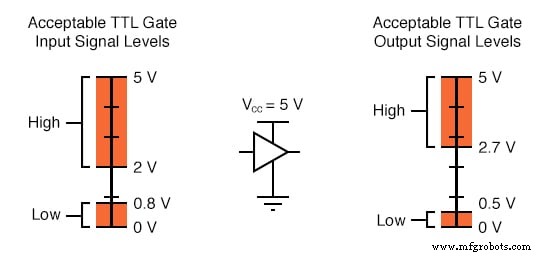

Gerbang TTL beroperasi pada tegangan catu daya nominal 5 volt, +/- 0,25 volt. Idealnya, sinyal "tinggi" TTL akan tepat 5,00 volt, dan sinyal "rendah" TTL tepat 0,00 volt.

Namun, rangkaian gerbang TTL nyata tidak dapat menghasilkan tingkat tegangan yang sempurna seperti itu, dan dirancang untuk menerima sinyal "tinggi" dan "rendah" yang menyimpang secara substansial dari nilai ideal ini.

Tegangan sinyal input yang "dapat diterima" berkisar dari 0 volt hingga 0,8 volt untuk status logika "rendah", dan 2 volt hingga 5 volt untuk status logika "tinggi".

Tegangan sinyal output yang “dapat diterima” (level tegangan yang dijamin oleh pabrikan gerbang pada rentang kondisi beban tertentu) berkisar dari 0 volt hingga 0,5 volt untuk status logika “rendah”, dan 2,7 volt hingga 5 volt untuk status logika “tinggi” :

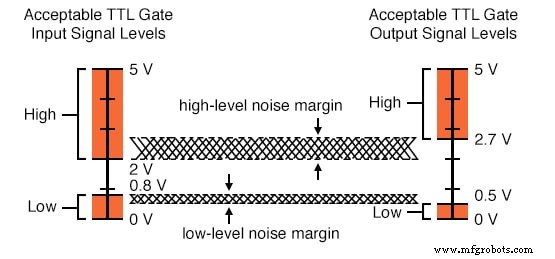

Jika sinyal tegangan berkisar antara 0,8 volt dan 2 volt dikirim ke input gerbang TTL, tidak akan ada respons pasti dari gerbang. Sinyal seperti itu akan dianggap tidak pasti , dan tidak ada produsen gerbang logika yang akan menjamin bagaimana sirkuit gerbang mereka akan menafsirkan sinyal seperti itu.

Seperti yang Anda lihat, rentang yang dapat ditoleransi untuk level sinyal output lebih sempit daripada level sinyal input, untuk memastikan bahwa setiap gerbang TTL yang mengeluarkan sinyal digital ke input gerbang TTL lain akan mengirimkan tegangan yang dapat diterima ke gerbang penerima. Perbedaan antara rentang keluaran dan masukan yang dapat ditoleransi disebut margin kebisingan dari gerbang.

Untuk gerbang TTL, margin kebisingan tingkat rendah adalah selisih antara 0,8 volt dan 0,5 volt (0,3 volt), sedangkan margin kebisingan tingkat tinggi adalah selisih antara 2,7 volt dan 2 volt (0,7 volt). Sederhananya, margin kebisingan adalah jumlah puncak tegangan palsu atau "noise" yang mungkin ditumpangkan pada sinyal tegangan keluaran gerbang yang lemah sebelum gerbang penerima mungkin menafsirkannya secara salah:

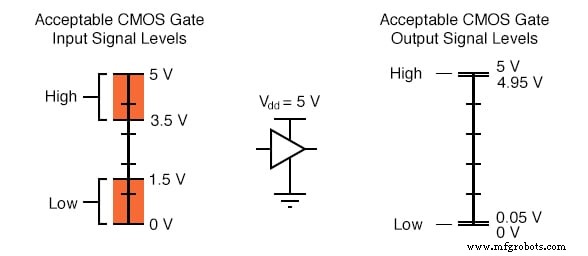

Rangkaian gerbang CMOS memiliki spesifikasi sinyal input dan output yang cukup berbeda dengan TTL. Untuk gerbang CMOS yang beroperasi pada tegangan catu daya 5 volt, tegangan sinyal input yang dapat diterima berkisar dari 0 volt hingga 1,5 volt untuk status logika "rendah", dan 3,5 volt hingga 5 volt untuk status logika "tinggi".

Tegangan sinyal keluaran yang "dapat diterima" (tingkat tegangan yang dijamin oleh pabrikan gerbang pada rentang kondisi beban tertentu) berkisar dari 0 volt hingga 0,05 volt untuk status logika "rendah", dan 4,95 volt hingga 5 volt untuk status logika "tinggi". :

Harus jelas dari angka-angka ini bahwa sirkuit gerbang CMOS memiliki margin kebisingan yang jauh lebih besar daripada TTL:1,45 volt untuk margin tingkat rendah dan tinggi CMOS, versus maksimum 0,7 volt untuk TTL. Dengan kata lain, sirkuit CMOS dapat mentolerir lebih dari dua kali jumlah tegangan “noise” yang ditumpangkan pada saluran inputnya sebelum kesalahan interpretasi sinyal akan terjadi.

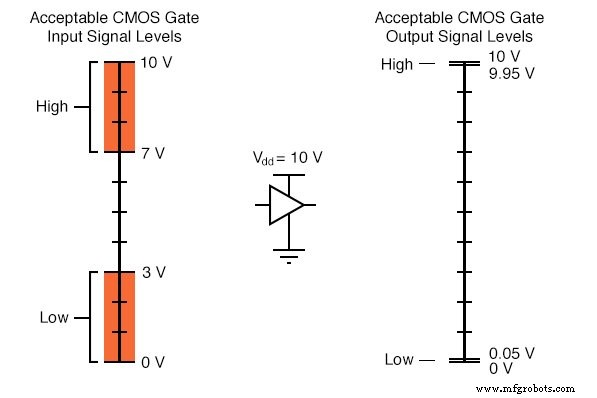

Margin Kebisingan pada Tegangan Operasi Lebih Tinggi

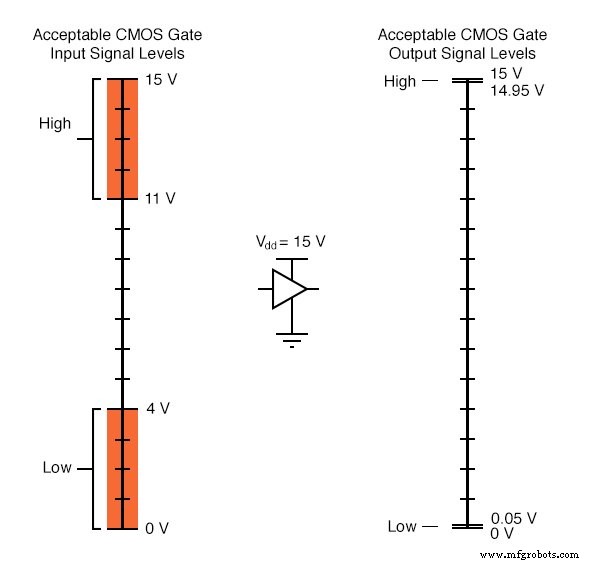

Margin noise CMOS semakin melebar dengan voltase pengoperasian yang lebih tinggi. Tidak seperti TTL, yang dibatasi pada tegangan catu daya 5 volt, CMOS dapat ditenagai oleh tegangan setinggi 15 volt (beberapa sirkuit CMOS setinggi 18 volt).

Ditampilkan di sini adalah status "tinggi" dan "rendah" yang dapat diterima, baik untuk input maupun output, dari sirkuit terpadu CMOS yang masing-masing beroperasi pada 10 volt dan 15 volt:

Margin untuk sinyal “tinggi” dan “rendah” yang dapat diterima mungkin lebih besar dari yang ditunjukkan pada ilustrasi sebelumnya. Apa yang ditampilkan menunjukkan kinerja sinyal input "kasus terburuk", berdasarkan spesifikasi pabrikan. Dalam praktiknya, mungkin ditemukan bahwa rangkaian gerbang akan mentolerir sinyal "tinggi" dengan tegangan yang jauh lebih rendah dan sinyal "rendah" dengan tegangan yang jauh lebih besar daripada yang ditentukan di sini.

Sebaliknya, margin keluaran yang sangat kecil yang ditunjukkan—menjamin status keluaran untuk sinyal “tinggi” dan “rendah” hingga dalam 0,05 volt dari “rel” catu daya—adalah optimis. Level tegangan keluaran "padat" seperti itu hanya berlaku untuk kondisi pembebanan minimum. Jika gerbang mengalirkan atau menenggelamkan arus substansial ke beban, tegangan keluaran tidak akan dapat mempertahankan tingkat optimal ini, karena resistansi saluran internal dari MOSFET keluaran akhir gerbang.

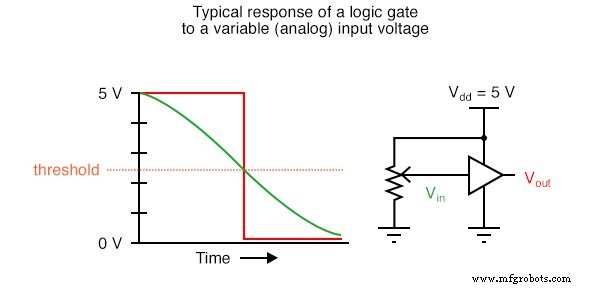

Ambang Tegangan

Dalam rentang "tidak pasti" untuk input gerbang apa pun, akan ada beberapa titik demarkasi yang membagi rentang sinyal input "rendah" aktual gerbang dari rentang sinyal input "tinggi" aktualnya. Artinya, di suatu tempat antara level tegangan sinyal "tinggi" terendah dan level tegangan sinyal "rendah" tertinggi yang dijamin oleh pabrikan gerbang, ada tegangan ambang batas di mana gerbang akan sebenarnya mengalihkan interpretasi sinyal dari "rendah" atau "tinggi" atau sebaliknya. Untuk sebagian besar sirkuit gerbang, tegangan yang tidak ditentukan ini adalah satu titik:

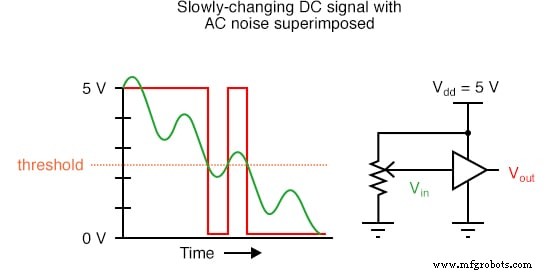

Masukan dengan Kebisingan AC

Dengan adanya tegangan “noise” AC yang ditumpangkan pada sinyal input DC, titik ambang tunggal di mana gerbang mengubah interpretasi level logikanya akan menghasilkan keluaran yang tidak menentu:

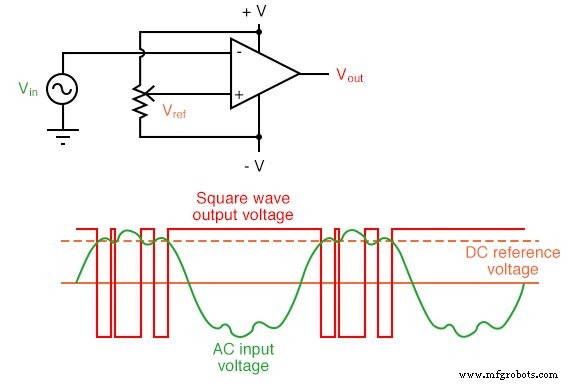

Jika skenario ini terlihat familier bagi Anda, itu karena Anda ingat masalah serupa dengan rangkaian op-amp pembanding tegangan (analog). Dengan titik ambang tunggal di mana input menyebabkan output beralih antara status "tinggi" dan "rendah", adanya noise yang signifikan akan menyebabkan perubahan yang tidak menentu pada output:

Solusi untuk masalah ini sedikit positif umpan balik dimasukkan ke dalam rangkaian penguat. Dengan op-amp, ini dilakukan dengan menghubungkan kembali keluaran ke masukan non-pembalik (+) melalui resistor.

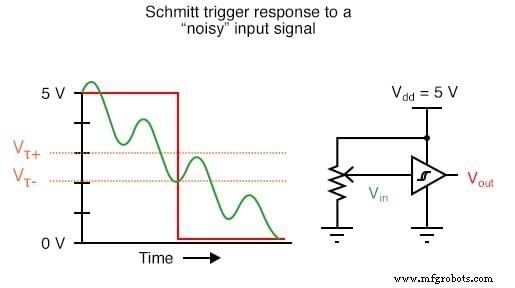

Di sirkuit gerbang, ini memerlukan mendesain ulang sirkuit gerbang internal, membangun umpan balik di dalam paket gerbang daripada melalui koneksi eksternal. Gerbang yang dirancang seperti itu disebut pemicu Schmitt . Pemicu Schmitt menafsirkan tegangan input yang bervariasi menurut dua tegangan ambang:berjalan positif ambang batas (VT+), dan berjalan negatif ambang batas (VT-):

Histeresis di Gerbang Pemicu Schmitt

Gerbang pemicu Schmitt dibedakan dalam diagram skematik dengan simbol "histeresis" kecil yang digambar di dalamnya, mengingatkan pada kurva B-H untuk bahan feromagnetik. Histeresis yang ditimbulkan oleh umpan balik positif dalam sirkuit gerbang menambahkan tingkat kekebalan kebisingan tambahan pada kinerja gerbang.

Gerbang pemicu Schmitt sering digunakan dalam aplikasi di mana kebisingan diharapkan pada jalur sinyal input, dan/atau di mana output yang tidak menentu akan sangat merugikan kinerja sistem.

Persyaratan level tegangan yang berbeda dari teknologi TTL dan CMOS menghadirkan masalah ketika kedua jenis gerbang digunakan dalam sistem yang sama. Meskipun mengoperasikan gerbang CMOS pada tegangan catu daya 5,00 volt yang sama yang dibutuhkan oleh gerbang TTL tidak menjadi masalah, level tegangan keluaran TTL tidak akan kompatibel dengan persyaratan tegangan masukan CMOS.

Contoh Sirkuit Kombinasi TTL dan CMOS

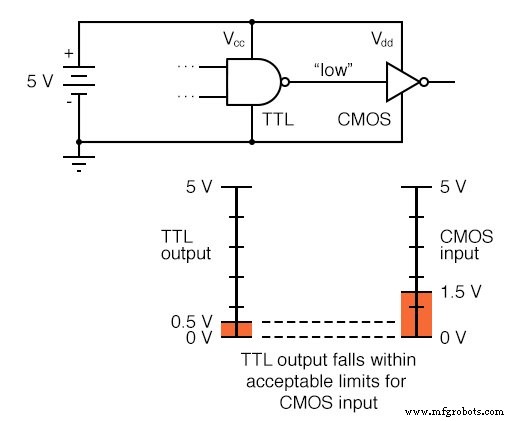

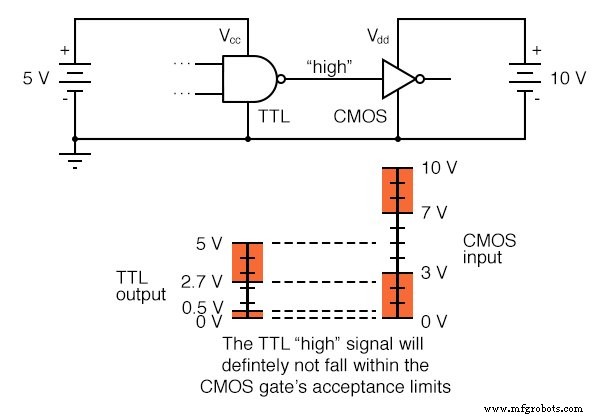

Ambil contoh gerbang NAND TTL yang mengeluarkan sinyal ke input gerbang inverter CMOS. Kedua gerbang ditenagai oleh suplai 5,00 volt yang sama (Vcc ). Jika gerbang TTL mengeluarkan sinyal "rendah" (dijamin antara 0 volt dan 0,5 volt), sinyal tersebut akan ditafsirkan dengan benar oleh input gerbang CMOS sebagai "rendah" (mengharapkan voltase antara 0 volt dan 1,5 volt):

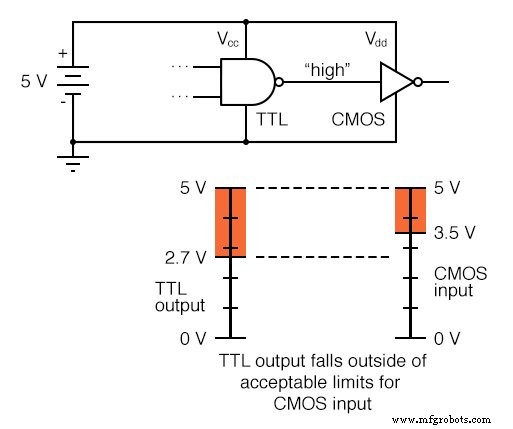

Namun, jika gerbang TTL mengeluarkan sinyal "tinggi" (dijamin antara 5 volt dan 2,7 volt), itu mungkin tidak ditafsirkan dengan benar oleh input gerbang CMOS sebagai "tinggi" (mengharapkan tegangan antara 5 volt dan 3,5 volt):

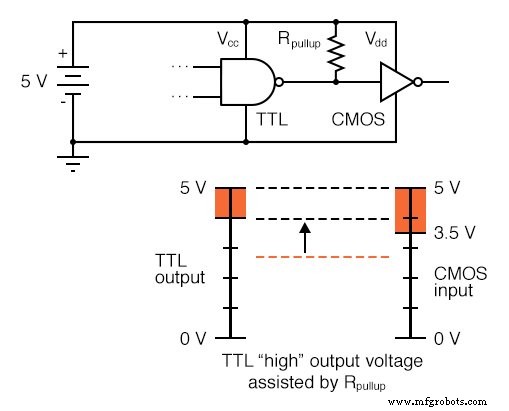

Mengingat ketidakcocokan ini, sangat mungkin bagi gerbang TTL untuk mengeluarkan sinyal "tinggi" yang valid (valid, yaitu, menurut standar untuk TTL) yang berada dalam kisaran "tidak pasti" untuk input CMOS, dan mungkin ( salah) ditafsirkan sebagai "rendah" oleh gerbang penerima. "Perbaikan" yang mudah untuk masalah ini adalah dengan menambah level tegangan sinyal "tinggi" gerbang TTL melalui resistor pullup:

Namun, sesuatu yang lebih dari ini diperlukan untuk menghubungkan keluaran TTL dengan masukan CMOS, jika gerbang CMOS penerima ditenagai oleh tegangan catu daya yang lebih besar:

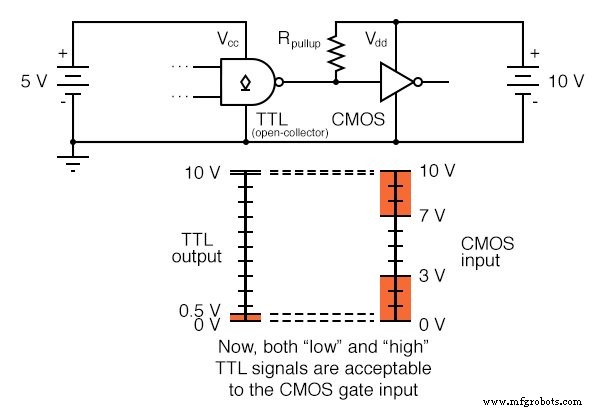

Menggunakan gerbang TTL Kolektor Terbuka dengan gerbang CMOS

Tidak akan ada masalah dengan gerbang CMOS yang menafsirkan output "rendah" gerbang TTL, tentu saja, tetapi sinyal "tinggi" dari gerbang TTL adalah masalah lain sepenuhnya. Rentang tegangan keluaran yang dijamin dari 2,7 volt hingga 5 volt dari keluaran gerbang TTL jauh dari kisaran yang dapat diterima gerbang CMOS dari 7 volt hingga 10 volt untuk sinyal "tinggi".

Jika kami menggunakan pengumpul terbuka Gerbang TTL sebagai ganti gerbang keluaran tiang totem, resistor pullup ke 10 volt Vdd rel suplai akan menaikkan tegangan keluaran "tinggi" gerbang TTL ke tegangan catu daya penuh yang memasok gerbang CMOS. Karena gerbang kolektor terbuka hanya dapat menenggelamkan arus, bukan arus sumber, tingkat tegangan status "tinggi" sepenuhnya ditentukan oleh catu daya tempat resistor pull-up dipasang, sehingga menyelesaikan masalah ketidakcocokan dengan rapi:

Masalah Menggunakan Output CMOS ke Input TTL

Karena karakteristik tegangan keluaran gerbang CMOS yang sangat baik, biasanya tidak ada masalah dalam menghubungkan keluaran CMOS ke masukan TTL. Satu-satunya masalah yang signifikan adalah pembebanan saat ini yang disajikan oleh input TTL, karena output CMOS harus menenggelamkan arus untuk setiap input TTL saat dalam status "rendah".

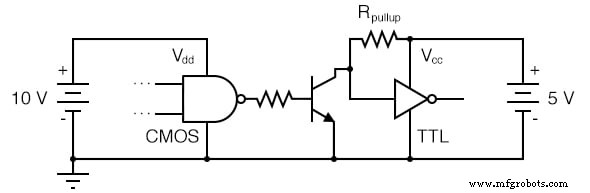

Ketika gerbang CMOS yang dimaksud dialiri oleh sumber tegangan lebih dari 5 volt (Vcc ), meskipun, masalah akan terjadi. Status keluaran "tinggi" dari gerbang CMOS, yang lebih besar dari 5 volt, akan melebihi batas masukan gerbang TTL yang dapat diterima untuk sinyal "tinggi".

Menggunakan Rangkaian Inverter Kolektor Terbuka

Solusi untuk masalah ini adalah membuat rangkaian inverter "kolektor terbuka" menggunakan transistor NPN diskrit, dan menggunakannya untuk menghubungkan kedua gerbang bersama-sama:

“Rpullup resistor ” adalah opsional, karena input TTL secara otomatis mengasumsikan status “tinggi” ketika dibiarkan mengambang, yang akan terjadi ketika output gerbang CMOS “rendah” dan transistor terputus. Tentu saja, salah satu konsekuensi yang sangat penting dari penerapan solusi ini adalah inversi logis yang dibuat oleh transistor:ketika gerbang CMOS mengeluarkan sinyal "rendah", gerbang TTL melihat input "tinggi"; dan ketika gerbang CMOS mengeluarkan sinyal "tinggi", transistor menjadi jenuh dan gerbang TTL melihat input "rendah". Selama inversi ini diperhitungkan dalam skema logis sistem, semuanya akan baik-baik saja.

LEMBAR KERJA TERKAIT:

Lembar Kerja Sinyal Logika Digital

Teknologi Industri

Generator elektromekanis adalah perangkat yang mampu menghasilkan tenaga listrik dari energi mekanik, biasanya putaran poros. Ketika tidak terhubung ke tahanan beban, generator akan menghasilkan tegangan yang kira-kira sebanding dengan kecepatan poros. Dengan konstruksi dan desain yang presisi, gene

Metode analisis tegangan simpul memecahkan tegangan yang tidak diketahui pada simpul rangkaian dalam hal sistem persamaan KCL. Analisis ini terlihat aneh karena melibatkan penggantian sumber tegangan dengan sumber arus yang setara. Juga, nilai resistor dalam ohm diganti dengan konduktansi ekivalen d

Teorema superposisi adalah salah satu pukulan jenius yang mengambil subjek yang kompleks dan menyederhanakannya dengan cara yang masuk akal. Teorema seperti Millman memang bekerja dengan baik, tetapi tidak terlalu jelas mengapa itu bekerja dengan sangat baik. Superposisi, di sisi lain, jelas. Anali

Ketika alternator menghasilkan tegangan AC, tegangan mengubah polaritas dari waktu ke waktu, tetapi melakukannya dengan cara yang sangat khusus. Ketika digambarkan dari waktu ke waktu, gelombang yang dilacak oleh tegangan polaritas bolak-balik ini dari alternator mengambil bentuk yang berbeda, yang