VHDL

Pernyataan generate dalam VHDL dapat secara otomatis menduplikasi blok kode ke penutupan dengan sinyal, proses, dan instance yang identik. Ini adalah loop for untuk region arsitektur yang dapat membuat proses berantai atau instance modul.

Tidak seperti loop for biasa, yang hanya dapat ada dalam proses atau subprogram, pernyataan generate ditempatkan langsung di wilayah arsitektur file VHDL. Ketika digunakan bersama dengan obat generik, ini menjadi alat yang ampuh untuk merancang modul VHDL yang dapat disesuaikan yang memungkinkan untuk digunakan kembali di seluruh desain.

Sintaks dari pernyataan generate adalah sebagai berikut:

[label :] for <constant_name> in <range> generate

[declarations_local_to_each_loop_iteration]

[begin]

<processes_and_instantiations>

end generate [label];

Bagian yang terlampir dalam tanda kurung siku adalah opsional. Dengan demikian, Anda dapat menghilangkan wilayah deklaratif dan begin kata kunci jika Anda tidak ingin mendeklarasikan objek lokal apa pun. to atau downto .

Sebelum kita mulai membuat pernyataan, saya akan menyajikan modul sederhana yang akan kita gunakan sebagai contoh di seluruh artikel ini. Ini adalah debouncer yang mampu mendebounce input sakelar tunggal.

Agar dapat digunakan untuk kecepatan clock apa pun, saya telah menambahkan input umum bernama timeout_cycles . Konstanta ini menentukan berapa banyak siklus jam waktu habis setelah input sakelar berubah. Debouncer akan mengabaikan perubahan tambahan dalam nilai sakelar selama periode waktu habis.

Daftar di bawah ini menunjukkan entitas debouncer modul. Ada sakelar yang melenting masukan, dan kemudian ada switch_debounced clean yang bersih keluaran.

entity debouncer is

generic (

timeout_cycles : positive

);

port (

clk : in std_logic;

rst : in std_logic;

switch : in std_logic;

switch_debounced : out std_logic

);

end debouncer;

Modul debouncer bergantung pada penghitung bilangan bulat untuk mencapai periode waktu habis. Panjang penghitung sinyal mengikuti konstanta generik. Itulah yang dilakukan oleh durasi waktu tunggu yang ditentukan selama instantiasi.

Karena kita perlu membaca nilai switch_debounced output internal, saya telah mendeklarasikan sinyal bayangan bernama debounced , yang akan kita gunakan sebagai gantinya. Itu solusi yang lebih bersih daripada opsi lainnya, yaitu mengatur inout mode di switch_debounce dalam entitas.

Terakhir, kami menerapkan perilaku debouncing dalam satu proses, seperti yang ditunjukkan pada kode di bawah ini.

architecture rtl of debouncer is

signal debounced : std_logic;

signal counter : integer range 0 to timeout_cycles - 1;

begin

-- Copy internal signal to output

switch_debounced <= debounced;

DEBOUNCE_PROC : process(clk)

begin

if rising_edge(clk) then

if rst = '1' then

counter <= 0;

debounced <= switch;

else

if counter < timeout_cycles - 1 then

counter <= counter + 1;

elsif switch /= debounced then

counter <= 0;

debounced <= switch;

end if;

end if;

end if;

end process;

end architecture;

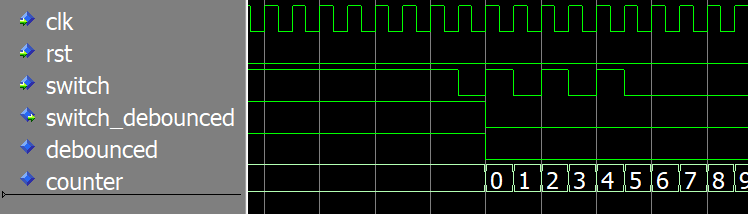

Bentuk gelombang di bawah ini menunjukkan simulasi debounce modul di ModelSim. Kita dapat melihat bahwa switch_debounced output mengikuti switch masukan, tetapi mengabaikan perilaku memantul langsung setelah perubahan pertama — ia mendebounce sinyal.

Gunakan formulir di bawah ini untuk mengunduh kode VHDL dari artikel ini. Saat Anda memasukkan alamat email, Anda akan menerima file Zip yang berisi seluruh proyek ModelSim dengan testbenches dan skrip quick-run. Anda akan menerima pembaruan di masa mendatang dari VHDLwhiz, dan Anda dapat berhenti berlangganan kapan saja.

Untuk membuat debouncer untuk array sakelar, kita akan menggunakan pernyataan generate untuk membuat beberapa instance modul debouncer satu bit kami.

Daftar di bawah ini menunjukkan entitas dari array baru atau modul vektor debouncer kami. Ini mirip dengan debouncer satu bit, tetapi ada input umum tambahan:switch_count . Ini menentukan berapa banyak contoh modul debouncer yang akan dibuat. Harus ada satu untuk setiap sakelar.

Selain itu, saya telah mengganti nama input dan output sakelar menjadi versi jamak dari kata tersebut, dan sekarang menjadi vektor, bukan bit tunggal.

entity debouncer_gen_inst is

generic (

switch_count : positive;

timeout_cycles : positive

);

port (

clk : in std_logic;

rst : in std_logic;

switches : in std_logic_vector(switch_count - 1 downto 0);

switches_debounced : out std_logic_vector(switch_count - 1 downto 0)

);

end debouncer_gen_inst;

Dalam arsitektur, saatnya menggunakan pernyataan generate. Ini bekerja seperti loop for biasa, hanya dengan kata "generate" menggantikan kata "loop". Namun tidak seperti perulangan for biasa, ia dapat berisi instance modul.

Loop for berjalan pada waktu kompilasi dan menghasilkan satu instance modul debouncer untuk setiap iterasi. Tetapi karena konstanta “i” akan berbeda untuk setiap iterasi, kita dapat menggunakannya untuk memetakan input dan output debouncer ke bit individual pada vektor switch, seperti yang ditunjukkan di bawah ini.

architecture rtl of debouncer_gen_inst is

begin

MY_GEN : for i in 0 to switch_count - 1 generate

DEBOUNCER : entity work.debouncer(rtl)

generic map (

timeout_cycles => timeout_cycles

)

port map (

clk => clk,

rst => rst,

switch => switches(i),

switch_debounced => switches_debounced(i)

);

end generate;

end architecture;

Perhatikan bahwa memberi label pada pernyataan generate adalah opsional, tetapi mungkin bijaksana untuk melakukannya. Label muncul di hierarki simulator dan log sintesis, sehingga memudahkan untuk mengidentifikasi instance spesifik saat debugging.

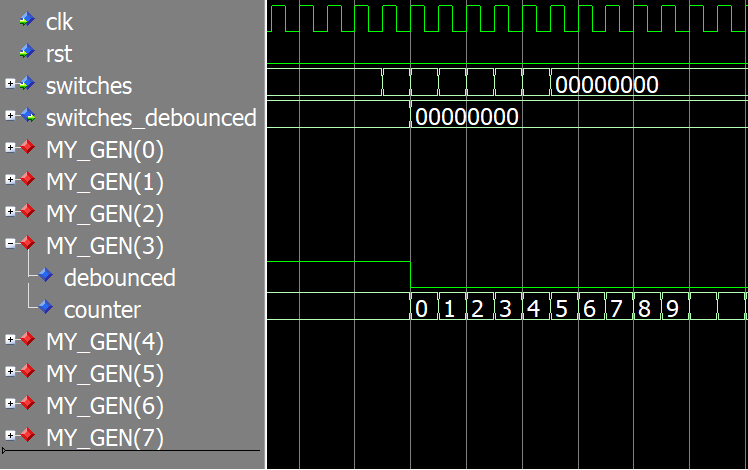

Bentuk gelombang di bawah ini menunjukkan simulasi vektor debouncer. Kita dapat melihat bahwa label “MY_GEN” muncul kembali di sini, dengan indeks ditambahkan untuk masing-masing dari delapan instance debouncer.

Testbench ini hanya mengubah input sakelar nomor 3, itulah yang Anda lihat dalam bentuk gelombang dan mengapa saya hanya memperluas grup MY_GEN(3).

Anda dapat dengan cepat menjalankan contoh ini di komputer Anda jika Anda telah menginstal ModelSim. Gunakan formulir di bawah ini untuk mengunduh kode sumber dan proyek ModelSim!

Pada contoh terakhir artikel ini, kita akan menggunakan pernyataan generate untuk membuat serangkaian proses yang identik. Alih-alih membuat instance modul debouncer satu bit, saya telah mengangkat kode VHDL darinya. Entitasnya sama dengan contoh sebelumnya, begitu juga perilakunya, tetapi implementasinya berbeda.

Kita dapat melihat bahwa saya telah memindahkan proses DEBOUNCE_PROC dalam pernyataan generate dan mengubahnya sedikit pada kode di bawah ini. Kali ini saya mendeklarasikan dua sinyal lokal dalam pernyataan generate:debounced dan penghitung .

Setiap iterasi dari for loop akan membuat salinan tambahan dari sinyal dan proses. Menggunakan nama sinyal ini dalam proses akan mereferensikan sinyal yang dicakup ke enklosur dari iterasi loop spesifik tersebut.

Akhirnya, saya menugaskan debounced std_logic sinyal ke bit yang benar dari switches_debounced keluaran modul menggunakan pernyataan bersamaan di atas proses.

architecture rtl of debouncer_gen_proc is

begin

MY_GEN : for i in 0 to switch_count - 1 generate

signal debounced : std_logic;

signal counter : integer range 0 to timeout_cycles - 1;

begin

switches_debounced(i) <= debounced;

DEBOUNCE_PROC : process(clk)

begin

if rising_edge(clk) then

if rst = '1' then

counter <= 0;

debounced <= switches(i);

else

if counter < timeout_cycles - 1 then

counter <= counter + 1;

elsif switches(i) /= debounced then

counter <= 0;

debounced <= switches(i);

end if;

end if;

end if;

end process;

end generate;

end architecture;

Saya telah menghilangkan bentuk gelombang simulasi karena terlihat persis sama seperti pada contoh sebelumnya menggunakan instantiasi modul. Perilakunya identik.

Anda dapat mengunduh semua kode menggunakan formulir di bawah ini. Ketika Anda memasukkan alamat email Anda, Anda berlangganan pembaruan dari VHDLwhiz. Tapi jangan khawatir, ada link unsubscribe di setiap email yang saya kirim.

Tinggalkan komentar di bawah jika Anda memiliki aplikasi lain yang berguna untuk menghasilkan pernyataan untuk dibagikan! ?

VHDL

Apa itu Pernyataan Switch di C? Ganti pernyataan di C menguji nilai variabel dan membandingkannya dengan beberapa kasus. Setelah kecocokan kasus ditemukan, blok pernyataan yang terkait dengan kasus tertentu akan dieksekusi. Setiap kasing dalam blok sakelar memiliki nama/nomor berbeda yang disebut

Kita semua menggunakan sakelar secara teratur dalam hidup kita. Ya, saya berbicara tentang sakelar listrik yang kami gunakan untuk lampu dan kipas kami. Seperti yang Anda lihat dari gambar di bawah, setiap sakelar ditugaskan untuk beroperasi untuk peralatan listrik tertentu. Misalnya, pada gambar,

Apa itu Pernyataan Bersyarat di Python? Pernyataan Bersyarat dalam Python melakukan perhitungan atau tindakan yang berbeda tergantung pada apakah batasan Boolean tertentu bernilai benar atau salah. Pernyataan bersyarat ditangani oleh pernyataan IF dengan Python. Dalam tutorial ini, kita akan melih

Diagram dan Instalasi Pengkabelan Perangkat Switch dan Outlet Combo Apa itu Perangkat Sakelar/Outlet Kombo dan Bagaimana Cara Menghubungkannya? Perangkat kombo adalah kombinasi sakelar dan stopkontak di kotak enklosur yang sama. Sakelar internal dapat disambungkan untuk mengontrol stopkontak di kot