Implementasi JTAG di Perangkat Arm Core

Artikel ini akan mengajarkan Anda tentang persilangan antara JTAG dan perangkat inti Arm, dengan perhatian khusus diberikan pada Arm Debug Interface atau ADI.

Sejauh ini dalam seri kami di JTAG, kami telah melihat standar IEEE 1149.1, termasuk pengontrol port akses uji (TAP) dan mesin status TAP. Kemudian kami meninjau berbagai antarmuka fisik yang tersedia untuk bekerja dengan JTAG, termasuk pinout umum untuk konektor, dan antarmuka JTAG serta probe debug yang tersedia di pasaran.

Pada artikel ini, kita akan sedikit menyimpang dari standar JTAG dan sebagai gantinya melihat bagaimana JTAG diimplementasikan di perangkat inti ARM yang ada di mana-mana.

Apa Itu Lengan?

Arm mengacu pada arsitektur prosesor, bersama dengan sejumlah besar kekayaan intelektual yang berkaitan dengan antarmuka mikroprosesor dan mikrokontroler. Jika PC konsumen cenderung menggunakan prosesor turunan x86, atau PowerPC, atau MIPS, elektronik tertanam paling sering diimplementasikan dengan prosesor Arm-core.

"Inti" prosesor didistribusikan ke pabrikan seperti ST Microelectronics atau NXP, dan pabrikan ini kemudian menambahkan fitur periferal tambahan, seperti antarmuka I2C dan SPI, ADC dan DAC, antarmuka USB, dan sebagainya.

Arsitektur lengan diversi sebagai ARMv, contohnya adalah ARMv2 (berasal dari 1987), ARMv6 (prosesor yang diproduksi 2002-2005) dan seterusnya, dan inti prosesor yang menggunakan arsitektur tersebut dicap sebagai seri ARMx (ARM1, ARM6, ARM7), dan baru-baru ini sebagai seri ARM Cortex-A/R/M untuk aplikasi berkinerja tinggi (Cortex-A), real-time (Cortex-R), dan mikrokontroler (Cortex-M). Versi arsitektur mengikuti penamaan sufiks Cortex, menjadi versi seperti ARMv6-M, ARMv7-R, ARMv7-A.

Antarmuka debugging Arm berada di bawah nama Arsitektur Arm CoreSight; ini termasuk antarmuka debug (Antarmuka Debug Lengan, ADI), makrosel jejak tertanam (ETM), port pelacakan serial kecepatan tinggi (HSSTP), dan arsitektur jejak aliran program CoreSight. ADI membentuk dasar untuk operasi debugging dengan prosesor Arm-core, dan bagian dari standar ini mencakup antarmuka JTAG serta alternatif Serial Wire Debug (SWD). Topik artikel ini adalah ADI, dan khususnya lapisan antarmuka perangkat keras.

Pengantar Antarmuka Debug Lengan (ADI)

Arm Debug Interface (ADI) adalah spesifikasi antarmuka perangkat keras dan antarmuka logis untuk debugging antara host dan satu atau lebih perangkat. Saat ini, sebagian besar prosesor menerapkan ADIv5 (ditentukan dalam Arm IHI0031E), sedangkan ADIv6 yang lebih baru (lihat Arm IHI0074C) secara bertahap diterapkan. Karena lebih populer, kami akan berfokus di sini pada standar ADIv5.

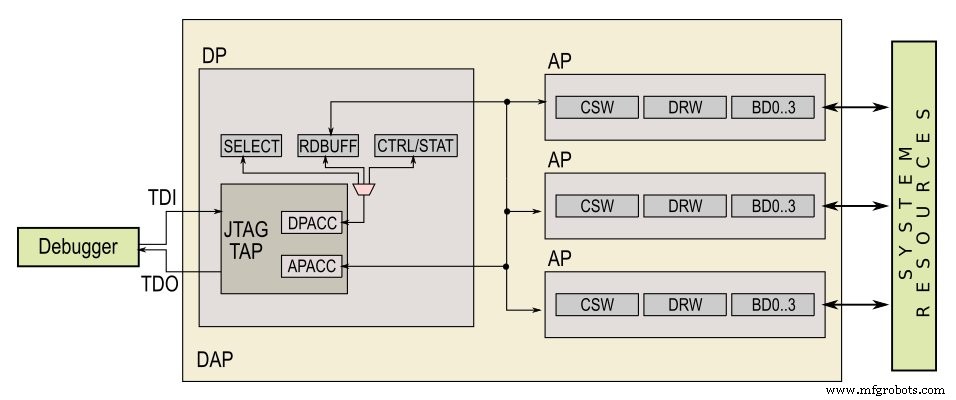

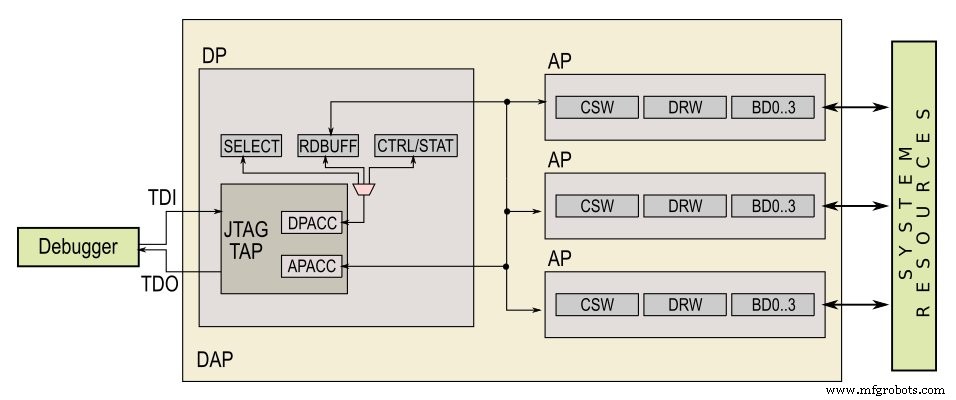

ADI mendefinisikan port akses debug (DAP), terdiri dari port debug (DP) dan port akses (AP). DAP adalah "unit" utama dari antarmuka debug. Perangkat yang diberikan akan memiliki satu port debug, yang menangani koneksi fisik dengan debugger, serta sejumlah port akses yang menyediakan akses ke sumber daya sistem seperti register debug, register port jejak, tabel ROM, atau memori sistem. Dengan demikian DP mencakup koneksi fisik (JTAG, SWD) serta beberapa register bawaan, dan setiap AP memiliki koneksinya sendiri ke sistem, dan sejumlah registernya sendiri.

Di ADIv5, ada dua jenis port debug, dan (secara umum) tiga jenis port akses. DP dapat berupa JTAG-DP, atau SWD-DP, dinamai untuk antarmuka yang digunakan dalam menghubungkan ke DAP dari luar perangkat. AP dapat berupa MEM-AP, menyediakan akses ke sumber daya dengan pengalamatan (analog dengan pemetaan memori, maka namanya), JTAG-AP, memungkinkan rantai pemindaian JTAG untuk dihubungkan ke seluruh unit debug (DAP), dan vendor-spesifik AP, yang tidak ditentukan oleh Arm. MEM-AP sejauh ini adalah yang paling umum dan berguna, jadi kami tidak akan membahas jenis lainnya di sini.

Dalam konteks JTAG, kami mengharapkan Antarmuka Debug untuk menyediakan kode instruksi JTAG, serta fitur JTAG khusus vendor. Sebenarnya, standar ADIv5 memberikan instruksi berikut:

- EXTEST (0b00000000)

- CONTOH (0b00000001)

- PRELOAD (0b00000010)

- INTEST (0b000000100)

- CLAMP (0b00000101)

- TINGGI (0b00000110)

- BATALKAN (0b11111000)

- DPACC (0b11111010)

- APACC (0b11111011)

- IDCODE (0b11111110)

- BYPASS (0b11111111)

Selain itu, register data JTAG meliputi:

- ABORT (35 bit), daftar untuk memaksa Access Port dibatalkan

- DPACC (35 bit), Daftar akses baca/tulis Port Debug

- APACC (35 bit), register akses baca/tulis Port Akses

- IDCODE (32 bit)

- BYPASS (1 bit)

Apa yang harus menonjol di sini adalah instruksi DPACC dan APACC, dan register data terkait. DPACC (Debug Port Access) dan APACC (Access Port Access) adalah instruksi/register yang digunakan untuk meneruskan perintah ke DP dan AP terkait perangkat. Dengan menetapkan nilai yang berbeda dalam register data DPACC atau APACC, debugger dapat menjalankan operasi yang berbeda, umumnya berinteraksi dengan register DP dan AP itu sendiri. Perhatikan perbedaan antara register DPACC dan APACC ini (register JTAG) dan register yang dibangun ke dalam DP dan AP.

Metodologi umum di sini adalah bahwa debugger menggunakan antarmuka JTAG atau SWD untuk mengeksekusi instruksi dengan melalui mesin negara TAP, kemudian instruksi mengambil data dan memuatnya ke DP atau AP, dan tergantung pada data, register yang berbeda dalam DP atau AP diakses, menyediakan tautan yang diinginkan ke sistem.

Jadi, apa itu register DP dan AP? Daftar DP yang tersedia antara lain:

- CTRL/STAT, digunakan untuk mengontrol dan memperoleh informasi status tentang DP

- DLCR, register Data Link Control, mengontrol mode operasi Data Link

- DLPIDR, register Identifikasi Protokol Tautan Data, informasi versi protokol

- DPIDR, register Identifikasi Port Debug, informasi Port Debug

- EVENTSTAT, register Status Peristiwa, digunakan oleh sistem untuk memberi sinyal peristiwa ke debugger eksternal

- RDBUFF, register Baca Buffer, menyediakan operasi baca; tergantung pada DP (JTAG atau SWD)

- SELECT, AP Select register, pilih Access Port dan bank register aktif dengan AP tersebut; memilih bank alamat DP

- TARGETID, memberikan informasi tentang target saat host terhubung ke satu perangkat

Sedangkan register MEM-AP adalah:

- Kontrol/Status Word register (CSW, 0x00), menyimpan kontrol dan informasi status

- Transfer Address Register (TAR, 0x04), menyimpan alamat untuk akses berikutnya ke sistem memori atau sumber daya sistem

- Register Baca/Tulis Data (DRW, 0x0C), mengatur pembacaan atau penulisan alamat di TAR – jika Anda membaca DRW, aksesnya diatur untuk membaca; jika Anda menulis ke DRW, aksesnya diatur untuk menulis

- Register Data Banked (BD0 to BD3, 0x10, 0x14, 0x18, 0x1C), menyediakan akses baca atau tulis langsung ke empat blok memori 32-bit, mulai dari alamat di TAR

- Register konfigurasi (CFG, 0xF4), informasi tentang konfigurasi MEM-AP

- Register Alamat Basis Debase (BASE, 0xF8), penunjuk ke sistem memori, baik awal set register debug atau awal tabel ROM

- Identification Register (IDR, 0xFC), mengidentifikasi MEM-AP.

Koneksi ditunjukkan secara skematis pada Gambar 1, di bawah ini.

Gambar 1. Diagram Antarmuka Arm Debug, meringkas koneksi. Catatan:tidak semua register ditampilkan untuk DP dan AP.

Rincian register DP/AP dan pemetaan memori dapat ditemukan dalam spesifikasi, IHI 0031E. Daripada membahas lebih jauh ke detailnya, saya ingin fokus pada jenis port debug lainnya, SWD-DP, dan cara mengimplementasikan JTAG hanya dengan menggunakan dua kabel.

Serial Wire Debug (SWD)

Sementara JTAG-DP adalah contoh umum dan familiar dari antarmuka debugging, yang paling relevan dengan diskusi kita adalah alternatif JTAG yang ditentukan untuk perangkat Arm, Arm Serial Wire Debug (SWD). SWD dikembangkan sebagai antarmuka dua kabel untuk perangkat Arm-core dengan jumlah pin terbatas. Karena mikrokontroler cenderung cukup padat di periferal, sebagian besar perangkat Cortex-M akan menerapkan SWD menggantikan JTAG penuh untuk menghemat pin real-estate. Jadi bagaimana cara kerja protokol ini?

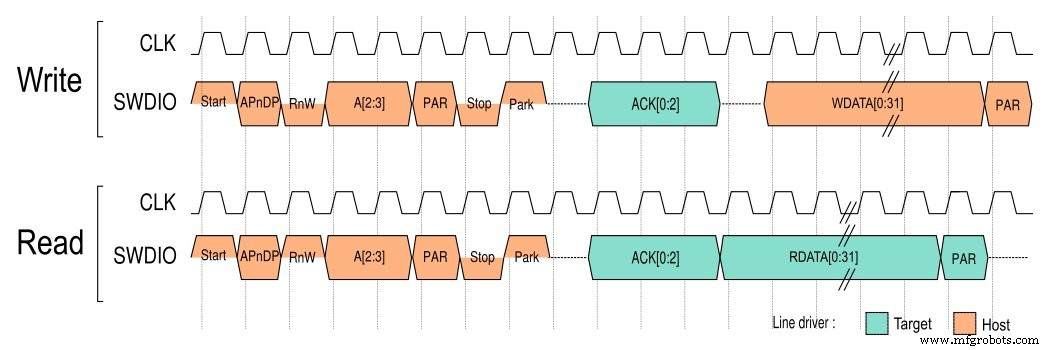

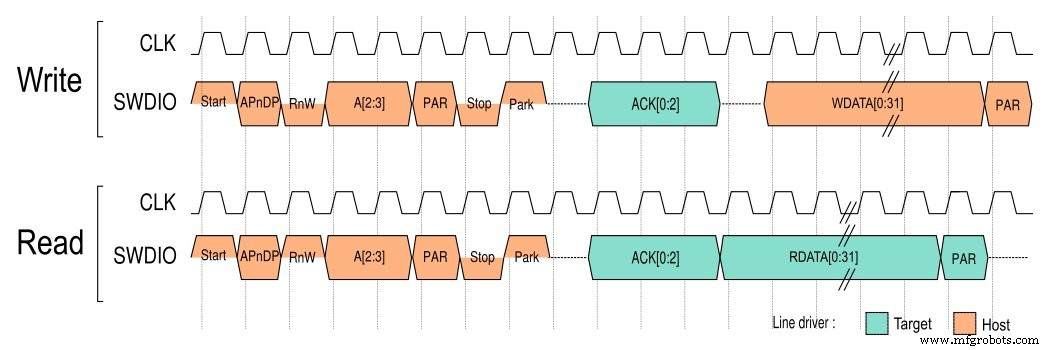

SWD ditentukan dalam spesifikasi ADIv5 (bab B4). Pin TDI dan TDO dari JTAG digantikan oleh pin dua arah tunggal yang disebut SWDIO; pin test mode select (TMS) dihapus seluruhnya; dan jam (TCK) tetap sama (diberi label ulang CLK atau SWCLK). Dengan demikian SWD hanya menggunakan dua pin dibandingkan dengan empat pin yang digunakan pada JTAG. Untuk membuat ini bekerja, SWD bergantung pada sifat berulang dari operasi JTAG:mesin negara dimanipulasi, data digeser masuk atau keluar, dan proses berulang. Bedanya dengan SWD tidak ada state machine. Sebagai gantinya, perintah dikeluarkan secara serial melalui SWDIO, dan kemudian pin yang sama digunakan untuk membaca atau menulis data.

Ada tiga fase komunikasi SWD:permintaan paket, pengakuan, dan transfer data. Selama permintaan paket, platform host mengeluarkan permintaan ke DP, dan ini harus diikuti dengan respons yang diakui. Jika permintaan paket adalah permintaan baca data atau tulis data, dan ada pengakuan yang valid, sistem memasuki fase transfer data, di mana data di-clock in (tulis) atau di-clock out (dibaca) melalui SWDIO. Setelah transfer data, host bertanggung jawab untuk memulai permintaan paket, atau menjalankan antarmuka SWD dengan siklus idle (melakukan pencatatan SWDIO LOW). Pemeriksaan paritas diterapkan pada permintaan paket dan fase transfer data.

Rincian SWD paling baik dipahami dengan melihat diagram waktu, yang ditunjukkan pada Gambar 2.

Gambar 2. Diagram pengaturan waktu yang menunjukkan operasi baca dan tulis untuk Serial Wire Debug. [Klik untuk memperbesar]

Operasi baca dan tulis keduanya dimulai dengan cara yang sama, dimulai dengan host yang menggerakkan jalur SWDIO ke bit Start, yang merupakan sinyal TINGGI. Ini diikuti oleh konfigurasi, termasuk bit akses AP atau DP (APnDP), bit baca atau tulis (RnW), alamat (A[2:3]), bit paritas (PAR), dan bit Stop ( sinyal RENDAH), akhirnya diikuti oleh bit Park, yaitu saat host menggerakkan jalur HIGH sebelum jalur berubah haluan. Selama turnaround, baik target maupun tuan rumah tidak diizinkan untuk mengarahkan garis.

Tergantung pada nilai RnW, operasi baca atau tulis dipilih. Jika menulis, target memberikan sinyal ACK 3-bit, maka ada periode turnaround lain, diikuti oleh data 32-bit yang akan ditulis (WDATA), dan bit paritas. Jika membaca, target memberikan ACK, dan kemudian melanjutkan jalur dengan data baca 32-bit (RDATA), diikuti oleh bit paritas. Jika kesalahan telah terjadi, bit ACK akan menunjukkan kesalahan, dan tuan rumah dapat mencoba untuk memulai kembali operasi. Perhatikan bahwa WDATA dan RDATA ditransmisikan paling tidak signifikan bit (LSb) terlebih dahulu, ditunjukkan pada Gambar 2 dengan menulis WDATA[0:31], bukan WDATA[31:0].

Dokumen Arm IHI0031E memberikan diagram pengaturan waktu lebih lanjut untuk memperjelas berbagai kasus dalam komunikasi, tetapi kasus di atas adalah kasus penggunaan utama. Perlu dicatat bahwa ada (pada saat penulisan) dua versi SWD; SWDv1 hanya mendukung satu koneksi antara host dan target (point-to-point), sedangkan SWDv2 mengimplementasikan komunikasi multi-target host tunggal (multidrop). Versi 2 hampir kompatibel dengan versi 1, terlepas dari beberapa kasus tepi.

Varian JTAG lainnya

SWD bukan satu-satunya varian dua kabel dari standar JTAG IEEE 1149.1. Khususnya, standar IEEE 1149.7 menyediakan antarmuka JTAG dengan jumlah pin yang dikurangi (2-kawat). Standar 1149.x lainnya seperti IEEE 1149.4 (Standar untuk Bus Uji Sinyal Campuran), dan IEEE 1149.6 (Standar Pemindaian Batas Jaringan Digital Lanjutan) telah dikembangkan dalam dua dekade terakhir, dan menyediakan fungsionalitas tambahan untuk aplikasi yang lebih terlibat. Ini mencakup hal-hal seperti pengujian pemindaian batas analog dan peningkatan kemampuan untuk saluran diferensial dan sambungan AC.

Standar terbaru tersedia dari situs web IEEE Standards Association.

Kesimpulan

Ini menyimpulkan cakupan kami tentang JTAG dan SWD. Sepanjang seri ini, kami telah mempelajari dari mana JTAG berasal, cara kerjanya, dan cara digunakan untuk men-debug dan memprogram perangkat. Kami telah melihat koneksi fisik untuk JTAG, termasuk konektor dan antarmuka yang tersedia, baik komersial maupun open-source. Terakhir, kami menyimpulkan dengan ringkasan implementasi JTAG untuk teknologi inti prosesor Arm yang populer, termasuk antarmuka dua kabel SWD.

Dari sini, kita dapat keluar dan dengan percaya diri menggunakan fitur debugging dan pemrograman dari perangkat tersemat kita, mempelajari detail untuk implementasi yang berbeda, dan memanfaatkan waktu kita sebaik mungkin.