Teknologi Industri

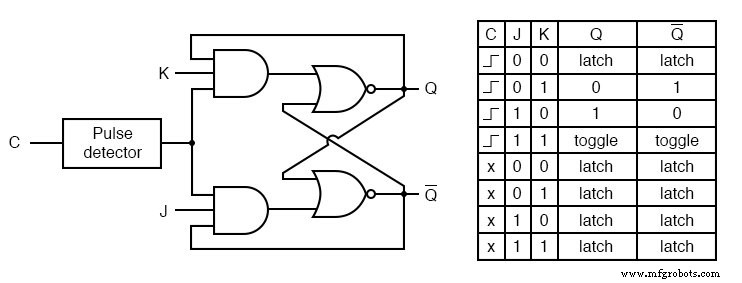

Variasi lain pada tema multivibrator bistabil adalah JK flip-flop. Pada dasarnya, ini adalah versi modifikasi dari flip-flop SR tanpa status keluaran "tidak valid" atau "ilegal". Perhatikan baik-baik diagram berikut untuk melihat bagaimana hal ini dilakukan:

Apa yang dulunya adalah input S dan R sekarang disebut input J dan K, masing-masing. Gerbang AND dua masukan yang lama telah diganti dengan gerbang AND 3 masukan, dan masukan ketiga dari setiap gerbang menerima umpan balik dari keluaran Q dan bukan-Q.

Apa yang dilakukan untuk kita adalah mengizinkan input J untuk memiliki efek hanya ketika rangkaian direset, dan mengizinkan input K untuk memiliki efek hanya ketika rangkaian disetel.

Dengan kata lain, kedua input saling bertautan , untuk menggunakan istilah logika relai, sehingga keduanya tidak dapat diaktifkan secara bersamaan.

Jika rangkaian "diset", input J dihambat oleh status 0 dari not-Q melalui gerbang AND yang lebih rendah; jika rangkaian "reset", input K dihambat oleh status 0 Q melalui gerbang AND atas.

Namun, ketika input J dan K keduanya adalah 1, sesuatu yang unik terjadi. Karena aksi penghambatan selektif dari gerbang AND 3-input tersebut, keadaan “set” menghambat input J sehingga flip-flop bertindak seolah-olah J=0 sedangkan K=1 padahal sebenarnya keduanya 1.

Pada pulsa clock berikutnya, output akan beralih (“toggle”) dari set (Q=1 dan bukan-Q=0) ke reset (Q=0 dan bukan-Q=1). Sebaliknya, status “reset” menghambat input K sehingga flip-flop bertindak seolah-olah J=1 dan K=0 padahal keduanya adalah 1. Pulsa clock berikutnya mengaktifkan rangkaian lagi dari reset ke set.

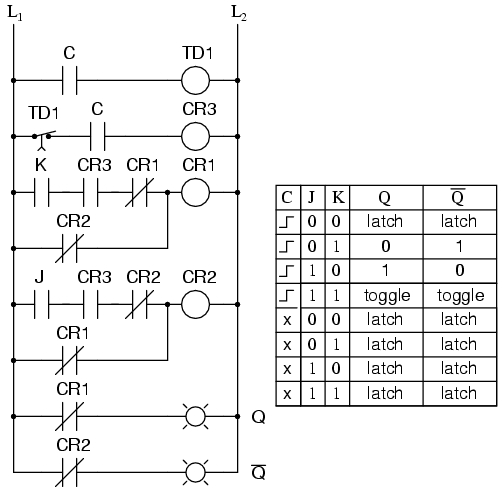

Lihat apakah Anda dapat mengikuti urutan logis ini dengan logika tangga yang setara dengan flip-flop JK:

Hasil akhirnya adalah bahwa status "tidak valid" SR flip-flop dihilangkan (bersama dengan kondisi balapan yang ditimbulkannya) dan kami mendapatkan fitur yang berguna sebagai bonus:kemampuan untuk beralih di antara dua status keluaran (bistabil) dengan setiap transisi sinyal input jam.

Tidak ada yang namanya gerendel JK, yang ada hanya sandal jepit JK. Tanpa pemicu tepi input clock, sirkuit akan terus beralih di antara dua status outputnya saat J dan K ditahan tinggi (1), menjadikannya perangkat astabil alih-alih perangkat bistable dalam keadaan itu.

Jika kita ingin mempertahankan operasi bistable untuk semua kombinasi status input, kita harus gunakan edge-triggering sehingga beralih hanya ketika kita memerintahkannya, satu langkah (pulsa clock) pada satu waktu.

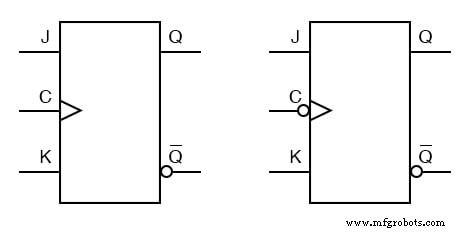

Simbol blok untuk flip-flop JK jauh lebih tidak menakutkan daripada sirkuit internalnya, dan seperti halnya flip-flop SR dan D, flip-flop JK hadir dalam dua jenis jam (dipicu tepi negatif dan positif):

TINJAUAN:

LEMBAR KERJA TERKAIT:

Teknologi Industri

Dari mengurangi biaya hingga meningkatkan efisiensi hingga memacu inovasi, banyak orang sangat antusias dengan dampak pencetakan 3D terhadap masa depan manufaktur. Namun, kenyataannya, hal itu telah memberikan dampak yang signifikan pada industri. Lihat kembali evolusi pencetakan 3D untuk melihat b

Hari Perempuan Internasional adalah hari global yang merayakan pencapaian sosial, ekonomi, budaya dan politik perempuan — sekaligus menandai seruan untuk bertindak untuk mempercepat kesetaraan gender. Untuk menghargai kampanye Every for Equal tahun ini, Jaringan Nasional MEPTM merilis video baru yan

Subyek reshoring manufaktur telah menjadi titik perdebatan di seluruh Industri Inggris sejak produksi rekayasa telah disubkontrakkan ke perusahaan lepas pantai. Sejauh ini, sektor manufaktur telah bertahan dan Inggris adalah negara manufaktur terbesar ke-9 di planet ini. Tetapi munculnya virus COVID

Ada dua output aktif-rendah pada IC 74LS47 yang dapat menggerakkan LED anoda umum atau indikasi pijar. Sebagai input, dibutuhkan desimal berkode biner, sehingga mengubahnya menjadi pola yang menggerakkan tampilan tujuh segmen yang menampilkan angka nol hingga sembilan (dari Setiap digit angka dikode