Desain dan Implementasi Papan Sakelar Interkoneksi FDR Kepadatan Tinggi

Saat ini kecepatan transmisi jaringan interkoneksi komputer berkinerja tinggi dengan penerapan transmisi serial berkecepatan tinggi telah berkembang menjadi FDR (Fourteen Data Rate, 14Gb/s), generasi ke-4 dari SDR primer (Single Data Rate, 2.5Gb/s). d), DDR (Laju Data Ganda, 5 Gb/dtk) dan QDR (Laju Data Quad, 10 Gb/dtk). Desain PCB (Printed Circuit Board) dengan interkoneksi dan papan sakelar dan kartu antarmuka yang penting untuk pembentukan Internet telah memasuki bidang kecepatan dan frekuensi tinggi FDR. Sejak meningkatnya waktu sinyal FDR telah berkurang secara drastis menjadi 10ps, serangkaian masalah mengenai integritas sinyal telah menjadi fitur utama untuk menentukan kemungkinan implementasi fungsionalitas dan operasi yang andal, seperti redaman, crosstalk, refleksi, interferensi elektromagnetik, dll. Berdasarkan fitur chip interkoneksi FDR termasuk beberapa port, beberapa saluran, beberapa kategori daya dan konsumsi energi yang tinggi, beberapa chip interkoneksi selalu diperlukan untuk diintegrasikan pada satu papan interkoneksi untuk meningkatkan tingkat throughput. Di papan dengan ruang terbatas, di satu sisi, beberapa persyaratan harus dipenuhi termasuk tata letak komponen dan pembuangan panas, perutean dengan kepadatan tinggi, transmisi jarak jauh di bagian belakang papan dan integritas semua jenis sinyal. Di sisi lain, beberapa elemen harus dipertimbangkan termasuk periode desain PCB, batasan teknik fabrikasi PCB dan pengendalian biaya. Oleh karena itu, sangat sulit untuk implementasi desain dan verifikasi simulasi. Berdasarkan contoh desain PCB interkoneksi FDR dan papan sakelar, artikel ini membahas beberapa metode optimasi dalam hal pemilihan bahan substrat, desain tumpukan, aturan perutean, dan desain anti-interferensi untuk menyelesaikan masalah integritas semua jenis sinyal di proses desain PCB berkecepatan tinggi FDR.

Pemilihan Atribut Atenuasi dan Material Substrat

Untuk sinyal frekuensi tinggi FDR, kehilangan saluran transmisi adalah masalah yang berkaitan dengan integritas sinyal. Ketika sinyal FDR ditransmisikan dari terminal transmisi ke terminal penerima di sepanjang saluran interkoneksi, karena redaman frekuensi tinggi jauh lebih besar daripada redaman frekuensi rendah, deformasi serius telah terjadi pada bentuk gelombang sinyal yang tiba di terminal penerima. Deformasi terutama diklasifikasikan menjadi dua aspek:ayunan tegangan sinyal telah sangat menurun sementara degradasi buruk telah terjadi pada tepi kenaikan sinyal. Yang pertama membatasi jarak transmisi sinyal sementara yang kedua mengarah pada interferensi antar kode. Rugi saluran transmisi A dapat dianggap sebagai jumlah rugi konduktor Acond dan rugi dielektrik Adiel seperti yang ditunjukkan pada Rumus (1):A =Adiel + Acond .

Kerugian konduktor mengacu pada kerugian yang disebabkan oleh resistor serial pada konduktor tembaga antara jalur sinyal dan jalur kembali. Dalam situasi frekuensi tinggi, efek kulit membuat arus mengalir di permukaan konduktor tembaga di sekitarnya. Dengan meningkatnya resistansi seri ekivalen konduktor tembaga, rugi konduktor akan meningkat dengan meningkatnya frekuensi yang berbanding lurus dengan akar kuadrat frekuensi, yang diilustrasikan pada Rumus (2): .

.

Rugi dielektrik mengacu pada kerugian yang dihasilkan oleh media bahan substrat, terutama ditentukan oleh atribut bahan dan tidak terkait dengan konstruksi geometris termasuk lebar konduktor, berbanding lurus dengan frekuensi, yang ditunjukkan pada Rumus (3): .

.

Berdasarkan Rumus (2), penambahan lebar saluran mampu mengurangi rugi-rugi konduktor. Namun, dalam desain PCB praktis, lebar konduktor tidak akan pernah bisa lebar tanpa batas sebagai akibat dari pembatasan jarak antara pin, papan, jumlah lapisan sinyal dan impedansi. Lebar/jarak/lebar konduktor yang umum diterapkan dalam desain FDR biasanya 7mil/7mil/7mil atau 8mil/10mil/8mil. Jika lebar konduktor sama, rugi konduktor berbanding lurus dengan panjang konduktor, tanpa ada hubungannya dengan material. Oleh karena itu, untuk mengurangi rugi-rugi transmisi secara keseluruhan, hanya rugi-rugi dielektrik yang harus dipertimbangkan. Berdasarkan Rumus (3), rugi dielektrik sebanding dengan faktor disipasi dan penerapan faktor disipasi kecil dapat membantu mengurangi rugi dielektrik, yang menyebabkan hilangnya transmisi secara keseluruhan.

Tabel 1 mencantumkan parameter atribut dari tiga bahan papan kecepatan tinggi biasa dan nilai kerugian yang dihitung menurut Rumus (1), (2) dan (3) ketika laju transmisi 14 Gb/dtk, lebar konduktor 8mil, dan impedansi 50Ω.

Dapat ditunjukkan bahwa dengan kecepatan transmisi 14 Gb/dtk dan panjang transmisi 30 inci, kerugian transmisi keseluruhan Nelco4000-13SI kira-kira 14dB sedangkan redaman ayunan tegangan yang dapat ditahan oleh chip FDR tipikal berkisar antara 20dB hingga 25dB. Oleh karena itu, bahan papan jenis ini dapat diterapkan dalam desain papan sakelar interkoneksi FDR dengan jarak transmisi kurang dari 30 inci. Namun, redaman transmisi keseluruhan FR4 adalah sekitar 27dB dan FR4 tidak dapat diterapkan untuk desain FDR desain jarak jauh tetapi kartu antarmuka interkoneksi FDR dengan jarak transmisi pendek diperbolehkan untuk memilih FR4 untuk mengurangi biaya. Adapun Megtron6 yang redaman transmisi keseluruhannya terkecil, fitur biaya tertinggi dan penerapannya di FDR menyebabkan peningkatan biaya arsitektur sistem. Kesimpulannya, untuk PCB frekuensi tinggi, bahan papan adalah dasar dan pemilihan bahan papan menentukan panjang transmisi sinyal.

Tata Letak dan Desain Tumpukan

Untuk desain PCB, struktur dan tumpukan papan sirkuit harus dipertimbangkan terlebih dahulu. Biasanya, pola dan bentuk papan sirkuit telah ditentukan dan penentuan nomor tumpukan terletak pada frekuensi sinyal, kepadatan pin papan sirkuit, biaya fabrikasi PCB, periode pembuatan dan persyaratan keandalan. Papan sakelar interkoneksi FDR memiliki frekuensi dan kepadatan tinggi dan penerapan papan multi-lapisan adalah langkah yang diperlukan untuk mengurangi interferensi. Selain itu, penentuan nomor tumpukan sangat penting.

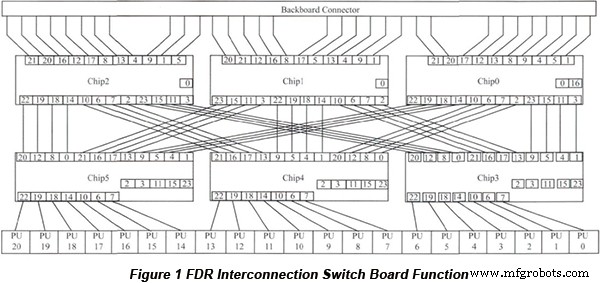

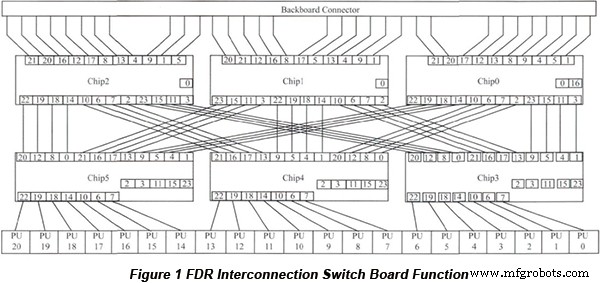

Ada 24 port pada chip interkoneksi FDR dan masing-masing port memiliki 8 saluran Tx dan 8 saluran Rx dalam metode operasi intercoupling. 6 chip interkoneksi dan 3 chip downlink diterapkan oleh papan interkoneksi FDR dan 32 port diakses melalui konektor papan belakang. 3 chip uplink mengakses 21 port melalui serat optik QSFP (Quad Small Form-factor Pluggable). Chip uplink dan chip downlink dihubungkan satu sama lain melalui 4 port, yang ditunjukkan pada Gambar 1.

FDR memiliki paket BGA (Ball Grid Array) dengan luas 50mmx50mm, 1157 pin dan jarak 1,0mm dan pin P/N pada port Tx dan Rx didistribusikan menurut 3 lingkaran konsentris. Secara teoritis, 3 lapisan sinyal dapat diterapkan untuk mengarahkan semua pin di semua port keluar dari BGA. Dengan mempertimbangkan dua elemen berikut, dua lapisan sinyal dapat digunakan untuk mengakses sekelompok pin lingkaran konsentris.

a. Karena batasan jarak, lebar garis/jarak/lebar garis diferensial adalah 4mil/4mil/4mil dan akan diperluas menjadi 8mil/10mil/8mil yang keluar dari BGA dan jarak antara pasangan garis diferensial tidak boleh kurang dari 50 juta Oleh karena itu, sepasang garis diferensial harus mengambil lebar 2mm dan 48 pasang sinyal berada di sepanjang tepi dengan kerapatan terbesar. Sehingga sulit untuk menerapkan metode ini.

b. Jarak antar pin BGA adalah 1mm. Jika lapisan sinyal diterapkan untuk mengakses sekelompok sinyal lingkaran konsentris, jarak antara pasangan garis diferensial di bawah BGA hanya 14mil yang jauh dari 50mil yang diperlukan. Selain itu, panjang perutean paralel maksimum hanya 20mm, yang akan menghasilkan beberapa crosstalk.

Untuk menghindari faktor negatif yang disebutkan di atas, dua lapisan sinyal diterapkan untuk mengakses sekelompok sinyal lingkaran konsentris dan sinyal diferensial pada setiap lapisan sinyal harus diarahkan keluar dari BGA menurut jarak 50mil. Oleh karena itu, setidaknya 6 lapisan diperlukan oleh papan interkoneksi FDR untuk membuat semua sinyal diferensial keluar dari BGA. Dengan mempertimbangkan konektivitas dan jumlah perutean papan dan permukaan papan yang cukup untuk kapasitor kopling pertukaran, 8 sinyal internal dan 22 tumpukan lapisan diterapkan.

Analisis Lintas Batas dan Tindakan Pengurangan

Crosstalk adalah pertimbangan pertama dalam hal desain sirkuit berkecepatan tinggi dan kepadatan tinggi. Ketika tegangan dan arus di saluran ofensif berubah, kopling elektromagnetik akan terjadi melalui kapasitansi timbal balik dan induktansi timbal balik antara saluran ofensif dan saluran korban. Crosstalk yang mengalir menuju terminal transmisi sepanjang jalur korban disebut crosstalk dekat terminal sedangkan crosstalk yang mengalir menuju terminal penerima di sepanjang jalur korban disebut crosstalk terminal jauh. Secara umum, tegangan kebisingan keseluruhan pada saluran korban harus dikontrol kurang dari 5% dari tegangan sinyal. Yang terbaik adalah mengontrol anggaran crosstalk dari garis ofensif satu sisi dalam 1% dengan sumber kebisingan lain dan garis ofensif di sekitar dua sisi garis korban dipertimbangkan.

Poin-poin penting yang harus diikuti dalam hal pengurangan crosstalk meliputi:

a. Jarak antara garis ofensif dan garis korban harus diperbesar dan panjang rute paralel harus dikurangi.

b. Ground terintegrasi diterapkan untuk menjadi jalur kembalinya sinyal. Menurut hukum empiris, untuk garis strip 50Ω, ketika jaraknya tiga kali lebar garis, crosstalk dekat-ujung sekitar 0,5%. Untuk garis mikrostrip 50Ω, ketika jaraknya tiga kali lebar garis, crosstalk dekat-ujung sekitar 1%. Crosstalk ujung jauh pada jalur strip atau jalur mikrostrip tertanam penuh hampir nol dan polaritas crosstalk ujung jauh saluran transmisi mikrostrip negatif dengan magnitudonya yang relatif besar karena pengaruh kopling induktif lebih besar daripada kopling kapasitif.

• Perutean interval

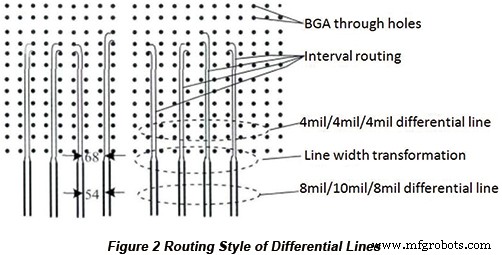

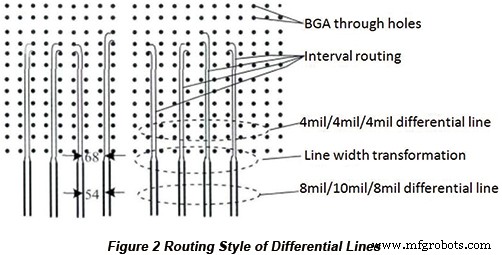

Dalam desain ini, impedansi diferensial dari saluran diferensial kecepatan tinggi adalah 100Ω. Berdasarkan pemecah bidang Si9000, lebar garis/spasi/lebar garis dihitung menjadi 8mil/10mil/8mil. Semakin lebar salurannya, semakin kecil redamannya dan jarak 10mil adalah untuk mempertahankan impedansi diferensial 100Ω. Jenis garis diferensial ini diterapkan di luar area chip BGA. Untuk mengurangi crosstalk, jarak antara dua pasang garis diferensial tidak kurang dari 80mil. The spacing between pins of interconnection chip in this article is 1mm and the through hole size limitation of BGA makes the line width/spacing/line width of the differential line in the BGA chip area 4mil/4mil/4mil. Although the differential impedance of this type of differential line is 100Ω as well, the lead loss is big, requiring differential line of 4mil/4mil/4mil to be transformed into 8mil/10mil/8mil as soon as it enters BGA chip area. In order to reduce crosstalk, differential line of 4mil/4mil/4mil in BGA chip area applies the way of interval routing to ensure the spacing between two pairs of differential lines more than 50mil as well, which is shown in Figure 2.

• Differential holes

Specific differential holes are set in this design for the application of exchange coupling capacitance on the connection surface layer. Ground holes have to be placed beside differential holes to provide backflow channel for returning path. Design of four ground holes features the best effect and two ground holes can be also applied when the area of board is limited. Besides, measures such as back drilling and internal pad eliminationhave should be taken to differential holes to reduce the impedance change at differential holes in order to decrease crosstalk and reflection.

• Preventing Tx and Rx from being routed in the same layer

In order to reduce crosstalk, Tx differential line should be routed in the different layer from Rx differential line. Here, Tx refers to the source terminal of differential line while Rx refers to the receiving terminal of differential line. If both of them have to be routed in the same layer, the spacing between them has to be over 5mm to ensure safety.

• 20H rule

In the PCB circuit with high frequency and high speed, RF energy is coupled by PCB power layer and ground layer and edge magnetic flux leakage is generated between power layer and ground layer. The radio RF energy can be radiated to the free space. 20H rule indicates that if there are high-speed currents on the board, there are electromagnetic fields associated with them. In the design of this article, the distance between all the routings and board edge should be at least 20 times of line width and the distance between high-speed differential holes and power plane cut-off lines is at least 5mm.

• Routing on the surface layer

In the design of high-frequency PCBs, with the relatively big far-end crosstalk between microstrip lines and strip lines considered, high-speed differential lines are prohibited on the surface layer. In the design of this article, at most 8 internal routing layers are required owing to the limitation of manufacturing craft. Moreover, the terminal arrangement limitation of interconnection chip makes it impossible for internal layers only to implement the connections of the interconnection differential lines between 6 chips inside connection board.

Helpful Resources

• Something You Must Know about HDI

• History of High-Density Packaging Technology

• 3 Keys to Designing a Successful HDI PCB

• Advantages of HDI Printed Circuit Boards

• Full Feature PCB Manufacturing Service from PCBCart - Multiple Value-added options

• Advanced PCB Assembly Service from PCBCart - Start from 1 piece

.

. .

.