Verilog

case pernyataan memeriksa apakah ekspresi yang diberikan cocok dengan salah satu ekspresi lain dalam daftar dan bercabang sesuai. Biasanya digunakan untuk mengimplementasikan multiplexer. Konstruksi if-else mungkin tidak cocok jika ada banyak kondisi yang harus diperiksa dan akan disintesis menjadi encoder prioritas alih-alih multiplexer.

Sebuah Verilog kasus pernyataan dimulai dengan case kata kunci dan diakhiri dengan endcase kata kunci. Ekspresi dalam parantheses akan dievaluasi tepat satu kali dan dibandingkan dengan daftar alternatif dalam urutan penulisannya dan pernyataan yang alternatifnya cocok dengan ekspresi yang diberikan akan dieksekusi. Sebuah blok dari beberapa pernyataan harus dikelompokkan dan berada dalam begin dan end .

// Here 'expression' should match one of the items (item 1,2,3 or 4)

case (<expression>)

case_item1 : <single statement>

case_item2,

case_item3 : <single statement>

case_item4 : begin

<multiple statements>

end

default : <statement>

endcase

Jika tidak ada item kasus yang cocok dengan ekspresi yang diberikan, pernyataan dalam default barang dieksekusi. default pernyataan adalah opsional, dan hanya boleh ada satu default pernyataan dalam pernyataan kasus. Pernyataan kasus dapat disarangkan.

Eksekusi akan keluar dari blok kasus tanpa melakukan apa pun jika tidak ada item yang cocok dengan ekspresi dan default pernyataan tidak diberikan.

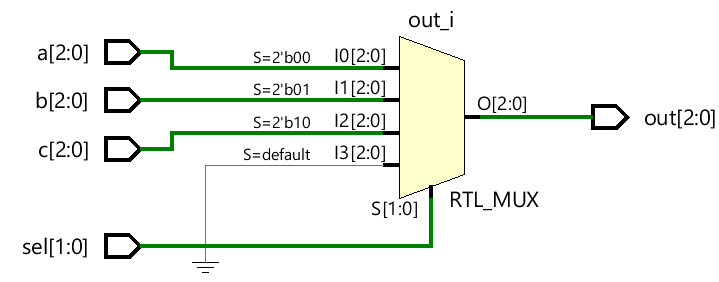

Modul desain yang ditunjukkan di bawah ini memiliki sinyal pilih 2-bit untuk merutekan salah satu dari tiga input 3-bit lainnya ke sinyal output yang dipanggil. Sebuah case pernyataan digunakan untuk menetapkan input yang benar ke output berdasarkan nilai sel. Karena sel adalah sinyal 2-bit, ia dapat memiliki 2

2

kombinasi, 0 hingga 3. Pernyataan default membantu menyetel output ke 0 jika sel adalah 3.

module my_mux (input [2:0] a, b, c, // Three 3-bit inputs

[1:0] sel, // 2-bit select signal to choose from a, b, c

output reg [2:0] out); // Output 3-bit signal

// This always block is executed whenever a, b, c or sel changes in value

always @ (a, b, c, sel) begin

case(sel)

2'b00 : out = a; // If sel=0, output is a

2'b01 : out = b; // If sel=1, output is b

2'b10 : out = c; // If sel=2, output is c

default : out = 0; // If sel is anything else, out is always 0

endcase

end

endmodule

Kode rtl dielaborasi untuk mendapatkan skema perangkat keras yang mewakili multiplexer 4 ke 1.

Lihat bahwa output adalah nol ketika sel adalah 3 dan sesuai dengan input yang ditetapkan untuk nilai lain.

Log Simulasincsim> run [0] a=0x4 b=0x1 c=0x1 sel=0b11 out=0x0 [10] a=0x5 b=0x5 c=0x5 sel=0b10 out=0x5 [20] a=0x1 b=0x5 c=0x6 sel=0b01 out=0x5 [30] a=0x5 b=0x4 c=0x1 sel=0b10 out=0x1 [40] a=0x5 b=0x2 c=0x5 sel=0b11 out=0x0 ncsim: *W,RNQUIE: Simulation is complete.

Dalam pernyataan kasus, perbandingan hanya berhasil ketika setiap bit ekspresi cocok dengan salah satu alternatif termasuk 0, 1, x dan z. Pada contoh di atas, jika salah satu bit dalam sel adalah x atau z, default pernyataan akan dieksekusi karena tidak ada alternatif lain yang cocok. Dalam kasus seperti itu, output akan menjadi nol.

ncsim> run [0] a=0x4 b=0x1 c=0x1 sel=0bxx out=0x0 [10] a=0x3 b=0x5 c=0x5 sel=0bzx out=0x0 [20] a=0x5 b=0x2 c=0x1 sel=0bxx out=0x0 [30] a=0x5 b=0x6 c=0x5 sel=0bzx out=0x0 [40] a=0x5 b=0x4 c=0x1 sel=0bxz out=0x0 [50] a=0x6 b=0x5 c=0x2 sel=0bxz out=0x0 [60] a=0x5 b=0x7 c=0x2 sel=0bzx out=0x0 [70] a=0x7 b=0x2 c=0x6 sel=0bzz out=0x0 [80] a=0x0 b=0x5 c=0x4 sel=0bxx out=0x0 [90] a=0x5 b=0x5 c=0x5 sel=0bxz out=0x0 ncsim: *W,RNQUIE: Simulation is complete.

Jika pernyataan kasus dalam desain memiliki x dan z dalam alternatif item kasus, hasilnya akan sangat berbeda.

module my_mux (input [2:0] a, b, c,

[1:0] sel,

output reg [2:0] out);

// Case items have x and z and sel has to match the exact value for

// output to be assigned with the corresponding input

always @ (a, b, c, sel) begin

case(sel)

2'bxz : out = a;

2'bzx : out = b;

2'bxx : out = c;

default : out = 0;

endcase

end

endmodule

Log Simulasi ncsim> run [0] a=0x4 b=0x1 c=0x1 sel=0bxx out=0x1 [10] a=0x3 b=0x5 c=0x5 sel=0bzx out=0x5 [20] a=0x5 b=0x2 c=0x1 sel=0bxx out=0x1 [30] a=0x5 b=0x6 c=0x5 sel=0bzx out=0x6 [40] a=0x5 b=0x4 c=0x1 sel=0bxz out=0x5 [50] a=0x6 b=0x5 c=0x2 sel=0bxz out=0x6 [60] a=0x5 b=0x7 c=0x2 sel=0bzx out=0x7 [70] a=0x7 b=0x2 c=0x6 sel=0bzz out=0x0 [80] a=0x0 b=0x5 c=0x4 sel=0bxx out=0x4 [90] a=0x5 b=0x5 c=0x5 sel=0bxz out=0x5 ncsim: *W,RNQUIE: Simulation is complete.

case pernyataan berbeda dari if-else-if dalam dua cara:

if-else blok lebih umum saat berada dalam case blok, satu ekspresi dicocokkan dengan beberapa itemcase akan memberikan hasil yang pasti ketika ada nilai X dan Z dalam suatu ekspresiVerilog

Sebuah generate block memungkinkan untuk menggandakan instance modul atau melakukan instantiasi bersyarat dari modul apa pun. Ini memberikan kemampuan untuk desain yang akan dibangun berdasarkan parameter Verilog. Pernyataan ini sangat cocok ketika operasi yang sama atau contoh modul perlu diulang b

Sebuah for loop adalah loop yang paling banyak digunakan dalam perangkat lunak, tetapi terutama digunakan untuk mereplikasi logika perangkat keras di Verilog. Ide di balik for loop adalah untuk mengulangi satu set pernyataan yang diberikan dalam loop selama kondisi yang diberikan benar. Ini sangat m

Parameter adalah konstruksi Verilog yang memungkinkan modul untuk digunakan kembali dengan spesifikasi yang berbeda. Misalnya, penambah 4-bit dapat diparameterisasi untuk menerima nilai jumlah bit dan nilai parameter baru dapat diteruskan selama pembuatan modul. Jadi, penambah N-bit bisa menjadi pen

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan? Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang