Verilog

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan?

Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang berbeda untuk memeriksa apakah kode RTL berperilaku dengan cara yang diinginkan. Pada dasarnya, simulasi adalah teknik yang diikuti dengan baik untuk memverifikasi kekokohan desain. Ini juga mirip dengan bagaimana chip yang dibuat akan digunakan di dunia nyata dan bagaimana ia bereaksi terhadap input yang berbeda.

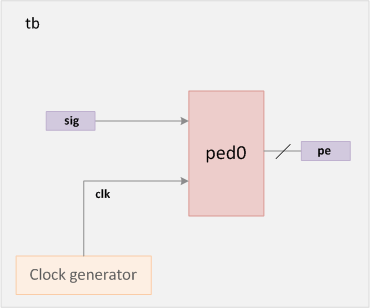

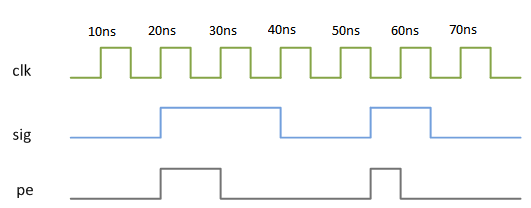

Misalnya, desain di atas mewakili detektor tepi positif dengan input clock dan sinyal yang dievaluasi secara berkala untuk menemukan output pe seperti yang ditunjukkan. Simulasi memungkinkan kita untuk melihat diagram waktu sinyal terkait untuk memahami bagaimana deskripsi desain di Verilog sebenarnya berperilaku.

Ada beberapa perusahaan EDA yang mengembangkan simulator mampu mencari tahu output untuk berbagai input ke desain. Verilog didefinisikan dalam istilah peristiwa terpisah model eksekusi dan simulator yang berbeda bebas menggunakan algoritme yang berbeda untuk memberikan serangkaian hasil yang konsisten kepada pengguna. Kode Verilog dibagi menjadi beberapa proses dan utas dan dapat dievaluasi pada waktu yang berbeda selama simulasi, yang akan dibahas nanti.

Testbench yang disebut tb adalah wadah untuk menampung modul desain. Namun, dalam contoh ini kami tidak menggunakan contoh desain apa pun. Ada dua variabel atau sinyal yang dapat diberi nilai tertentu pada waktu tertentu. clk mewakili jam yang dihasilkan dalam testbench. Ini dilakukan oleh always pernyataan dengan mengganti nilai jam setelah setiap 5ns. initial blok berisi satu set pernyataan yang menetapkan nilai yang berbeda untuk kedua sinyal pada waktu yang berbeda.

module tb;

reg clk;

reg sig;

// Clock generation

// Process starts at time 0ns and loops after every 5ns

always #5 clk = ~clk;

// Initial block : Process starts at time 0ns

initial begin

// This system task will print out the signal values everytime they change

$monitor("Time = %0t clk = %0d sig = %0d", $time, clk, sig);

// Also called stimulus, we simply assign different values to the variables

// after some simulation "delay"

sig = 0;

#5 clk = 0; // Assign clk to 0 at time 5ns

#15 sig = 1; // Assign sig to 1 at time 20ns (#5 + #15)

#20 sig = 0; // Assign sig to 0 at time 40ns (#5 + #15 + #20)

#15 sig = 1; // Assign sig to 1 at time 55ns (#5 + #15 + #20 + #15)

#10 sig = 0; // Assign sig to 0 at time 65ns (#5 + #15 + #20 + #15 + #10)

#20 $finish; // Finish simulation at time 85ns

end

endmodule

Simulator memberikan output berikut setelah eksekusi testbench di atas.

Log Simulasincsim> run Time = 0 clk = x sig = 0 Time = 5 clk = 0 sig = 0 Time = 10 clk = 1 sig = 0 Time = 15 clk = 0 sig = 0 Time = 20 clk = 1 sig = 1 Time = 25 clk = 0 sig = 1 Time = 30 clk = 1 sig = 1 Time = 35 clk = 0 sig = 1 Time = 40 clk = 1 sig = 0 Time = 45 clk = 0 sig = 0 Time = 50 clk = 1 sig = 0 Time = 55 clk = 0 sig = 1 Time = 60 clk = 1 sig = 1 Time = 65 clk = 0 sig = 0 Time = 70 clk = 1 sig = 0 Time = 75 clk = 0 sig = 0 Time = 80 clk = 1 sig = 0 Simulation complete via $finish(1) at time 85 NS + 0

Simulasi memungkinkan kami untuk membuang sinyal desain dan testbench ke dalam bentuk gelombang yang dapat direpresentasikan secara grafis untuk menganalisis dan men-debug fungsionalitas desain RTL. Bentuk gelombang yang ditunjukkan di bawah ini diperoleh dari alat EDA dan menunjukkan kemajuan setiap sinyal terhadap waktu dan sama dengan diagram waktu yang ditunjukkan sebelumnya.

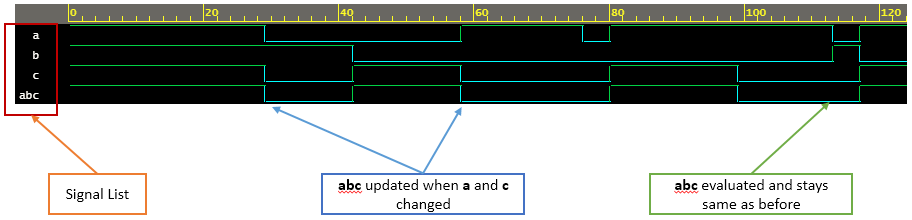

Setiap perubahan nilai variabel atau net disebut peristiwa pembaruan . Dan proses sensitif terhadap perbarui acara sedemikian rupa sehingga proses ini dievaluasi setiap kali peristiwa pembaruan terjadi dan disebut peristiwa evaluasi . Karena kemungkinan memiliki beberapa proses yang dievaluasi secara sewenang-wenang, urutan perubahan harus dilacak dalam sesuatu yang disebut sebagai antrean peristiwa .

Secara alami, mereka diperintahkan oleh waktu simulasi. Penempatan acara baru pada antrian disebut penjadwalan . Waktu simulasi digunakan untuk merujuk pada nilai waktu yang dipertahankan oleh simulator untuk memodelkan waktu aktual yang diperlukan untuk rangkaian yang disimulasikan. Nilai waktu untuk contoh di atas ditampilkan dalam nanodetik ns dalam diagram waktu.

module des;

wire abc;

wire a, b, c;

assign abc = a & b | c; // abc is updated via the assign statement (process) whenever a, b or c change -> update event

endmodule

Refresh Verilog dan lihat contohnya !

Antrean acara Verilog secara logis dibagi menjadi lima wilayah, dan acara dapat ditambahkan ke salah satu dari mereka. Namun, itu hanya dapat dihapus dari wilayah aktif.

Siklus simulasi adalah tempat semua peristiwa aktif diproses. Standar menjamin urutan penjadwalan tertentu kecuali untuk beberapa kasus dan. Misalnya, pernyataan di dalam blok awal-akhir hanya akan dieksekusi sesuai urutan kemunculannya.

module tb;

reg [3:0] a;

reg [3:0] b;

initial begin // Statements are executed one after the other at appropriate simulation times

a = 5; // At time 0ns, a is assigned 5

b = 2; // In the same simulation step (time 0ns), b is assigned 2

#10 a = 7; // When simulation advances to 10ns, a is assigned 7

end

endmodule

Antrian acara mendefinisikan tugas itu ke b harus terjadi setelah penugasan ke a .

Verilog

Sebuah for loop adalah loop yang paling banyak digunakan dalam perangkat lunak, tetapi terutama digunakan untuk mereplikasi logika perangkat keras di Verilog. Ide di balik for loop adalah untuk mengulangi satu set pernyataan yang diberikan dalam loop selama kondisi yang diberikan benar. Ini sangat m

case pernyataan memeriksa apakah ekspresi yang diberikan cocok dengan salah satu ekspresi lain dalam daftar dan bercabang sesuai. Biasanya digunakan untuk mengimplementasikan multiplexer. Konstruksi if-else mungkin tidak cocok jika ada banyak kondisi yang harus diperiksa dan akan disintesis menjadi

Parameter adalah konstruksi Verilog yang memungkinkan modul untuk digunakan kembali dengan spesifikasi yang berbeda. Misalnya, penambah 4-bit dapat diparameterisasi untuk menerima nilai jumlah bit dan nilai parameter baru dapat diteruskan selama pembuatan modul. Jadi, penambah N-bit bisa menjadi pen

Simulasi Verilog tergantung pada bagaimana waktu didefinisikan karena simulator perlu mengetahui apa arti #1 dalam hal waktu. `timescale direktif compiler menentukan unit waktu dan presisi untuk modul yang mengikutinya. Sintaks `timescale <time_unit>/<time_precision> // Example `ti