VHDL

Semua Desainer Digital harus memahami cara kerja matematika di dalam FPGA atau ASIC. Langkah pertama untuk itu adalah memahami cara kerja jenis sinyal yang ditandatangani dan tidak ditandatangani. Jenis yang ditandatangani dan tidak ditandatangani ada di numeric_std paket, yang merupakan bagian dari perpustakaan ieee. Perlu dicatat bahwa ada file paket lain yang sering digunakan untuk melakukan operasi matematika:std_logic_arith . Namun, std_logic_arith bukan file paket resmi yang didukung ieee dan tidak disarankan untuk digunakan dalam desain digital.

Sinyal yang didefinisikan sebagai tipe ditandatangani berarti bahwa alat menafsirkan sinyal ini menjadi positif atau negatif. Sinyal yang didefinisikan sebagai tipe tidak ditandatangani berarti bahwa sinyal hanya akan positif. Secara internal, FPGA akan menggunakan Two's Complement perwakilan. Misalnya, sinyal 3-bit dapat diinterpretasikan sesuai dengan tabel di bawah ini:

Apakah Anda masih bingung? Anda harus, ini tidak intuitif! Mari kita lihat contoh yang mudah-mudahan akan memperjelas semuanya. File di bawah ini menguji cara kerja unsigned yang ditandatangani. Yang perlu dipahami adalah bahwa apakah sinyal didefinisikan sebagai ditandatangani atau tidak, tidak mempengaruhi bagaimana matematika biner sebenarnya dilakukan.

Misalnya:Untuk dua vektor bertanda 10001 + 00010 jawabannya tetap 10011, TETAPI interpretasinya dari hasil yang berbeda.

Untuk kasus yang tidak ditandatangani, jawabannya (10011) mewakili 19.

Untuk kasus yang ditandatangani, jawabannya (10011) mewakili -13.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity signed_unsigned is

port (

i_rst_l : in std_logic;

i_clk : in std_logic;

i_a : in std_logic_vector(4 downto 0);

i_b : in std_logic_vector(4 downto 0)

);

end signed_unsigned;

architecture behave of signed_unsigned is

signal rs_SUM_RESULT : signed(4 downto 0) := (others => '0');

signal ru_SUM_RESULT : unsigned(4 downto 0) := (others => '0');

signal rs_SUB_RESULT : signed(4 downto 0) := (others => '0');

signal ru_SUB_RESULT : unsigned(4 downto 0) := (others => '0');

begin

-- Purpose: Add two numbers. Does both the signed and unsigned

-- addition for demonstration. This process is synthesizable.

p_SUM : process (i_clk, i_rst_l)

begin

if i_rst_l = '0' then -- asynchronous reset (active low)

rs_SUM_RESULT <= (others => '0');

ru_SUM_RESULT <= (others => '0');

elsif rising_edge(i_clk) then

ru_SUM_RESULT <= unsigned(i_a) + unsigned(i_b);

rs_SUM_RESULT <= signed(i_a) + signed(i_b);

end if;

end process p_SUM;

-- Purpose: Subtract two numbers. Does both the signed and unsigned

-- subtraction for demonstration. This process is synthesizable.

p_SUB : process (i_clk, i_rst_l)

begin

if i_rst_l = '0' then -- asynchronous reset (active low)

rs_SUB_RESULT <= (others => '0');

ru_SUB_RESULT <= (others => '0');

elsif rising_edge(i_clk) then

ru_SUB_RESULT <= unsigned(i_a) - unsigned(i_b);

rs_SUB_RESULT <= signed(i_a) - signed(i_b);

end if;

end process p_SUB;

end behave;

Testbench:

library ieee;

use ieee.std_logic_1164.all;

entity example_signed_unsigned_tb is

end example_signed_unsigned_tb;

architecture behave of example_signed_unsigned_tb is

--Registers

signal r_CLK : std_logic := '0';

signal r_RST_L : std_logic := '0';

signal r_A : natural := 0;

signal r_B : natural := 0;

signal r_A_SLV : std_logic_vector(4 downto 0) := (others => '0');

signal r_B_SLV : std_logic_vector(4 downto 0) := (others => '0');

constant c_CLK_PERIOD : time := 10 ns;

component example_signed_unsigned is

port (

i_rst_l : in std_logic;

i_clk : in std_logic;

i_a : in std_logic_vector(4 downto 0);

i_b : in std_logic_vector(4 downto 0)

);

end component example_signed_unsigned;

begin

i_DUT: example_signed_unsigned

port map (

i_rst_l => r_RST_L,

i_clk => r_CLK,

i_a => r_A_SLV,

i_b => r_B_SLV

);

clk_gen : process is

begin

r_CLK <= '0' after c_CLK_PERIOD/2, '1' after c_CLK_PERIOD;

wait for c_CLK_PERIOD;

end process clk_gen;

process

begin

r_RST_L <= '0';

wait for 20 ns;

r_RST_L <= '1';

wait for 20 ns;

r_A_SLV <= "01001";

r_B_SLV <= "00110";

wait for 20 ns;

r_A_SLV <= "10001";

r_B_SLV <= "00110";

wait for 20 ns;

r_A_SLV <= "10001";

r_B_SLV <= "00001";

wait for 20 ns;

r_A_SLV <= "10001";

r_B_SLV <= "00010";

wait for 20 ns;

r_A_SLV <= "11111";

r_B_SLV <= "00001";

wait for 20 ns;

r_A_SLV <= "00000";

r_B_SLV <= "00001";

wait for 20 ns;

wait;

end process;

end behave;

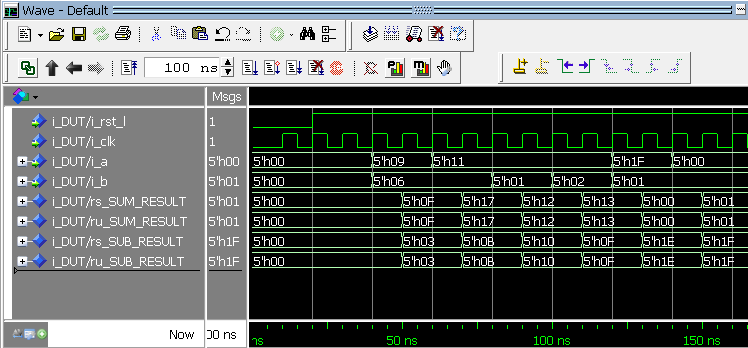

Nilai keluaran gelombang simulasi modelsim Ditampilkan dalam HEX

Nilai keluaran gelombang simulasi modelsim Ditampilkan dalam HEX

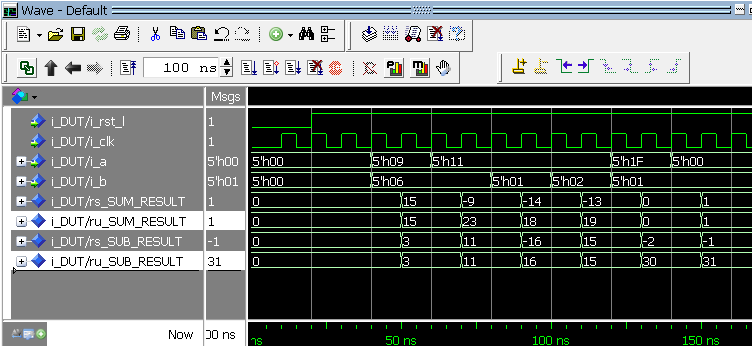

Nilai keluaran gelombang simulasi modelsim Ditampilkan dalam DECIMAL

Nilai keluaran gelombang simulasi modelsim Ditampilkan dalam DECIMAL Bandingkan kedua screenshot modelsim di atas. Pada bagian pertama Anda dapat melihat bahwa hasil dari fungsi matematika yang persis sama ketika direpresentasikan dalam hex. Ini adalah interpretasi dari hasil yang berbeda. Ini dapat dilihat dengan melihat tangkapan layar bagian bawah. Ketika Modelsim menampilkan hasil dalam desimal itu menafsirkan beberapa dari mereka sebagai angka negatif. Saat menggunakan tipe yang ditandatangani dan tidak ditandatangani, Anda harus sangat berhati-hati! Semoga Anda memahami topik ini sedikit lebih baik. Saya merasa ini adalah area yang banyak diperjuangkan oleh desainer digital, jadi jika ada sesuatu yang tidak sepenuhnya Anda pahami, kirimkan saya email melalui Tautan Kontak di Bilah Sisi dan saya akan mencoba membuatnya lebih jelas.

VHDL

Pada tutorial sebelumnya kita telah belajar bagaimana mendeklarasikan sebuah variabel dalam sebuah proses. Variabel bagus untuk membuat algoritme dalam suatu proses, tetapi tidak dapat diakses oleh dunia luar. Jika ruang lingkup variabel hanya dalam satu proses, bagaimana ia dapat berinteraksi denga

Dalam tutorial sebelumnya, kita belajar bagaimana menggunakan For-Loop untuk melakukan iterasi pada rentang integer. Tetapi bagaimana jika kita menginginkan kontrol loop yang lebih rinci daripada sekadar rentang bilangan bulat tetap? Kita bisa menggunakan While-Loop untuk ini. While-Loop akan terus

Pada tutorial sebelumnya kita belajar membuat infinite loop dengan menggunakan loop penyataan. Kami juga mempelajari cara keluar dari loop dengan menggunakan exit penyataan. Tetapi bagaimana jika kita ingin loop berulang beberapa kali? For-Loop adalah cara termudah untuk melakukannya. For-Loop memu

Singkatnya, VHDL adalah bahasa komputer yang digunakan untuk merancang sirkuit digital. Saya menggunakan istilah bahasa komputer untuk membedakan VHDL dari bahasa pemrograman lain yang lebih umum seperti Java atau C++. Tetapi apakah VHDL adalah bahasa pemrograman? Ya itu. Ini adalah bahasa pemro