VHDL

Singkatnya, VHDL adalah bahasa komputer yang digunakan untuk merancang sirkuit digital.

Saya menggunakan istilah "bahasa komputer" untuk membedakan VHDL dari bahasa pemrograman lain yang lebih umum seperti Java atau C++. Tetapi apakah VHDL adalah bahasa pemrograman? Ya itu. Ini adalah bahasa pemrograman yang tidak berguna untuk membuat program komputer!

VHDL adalah bahasa pemrograman paralel yang digerakkan oleh peristiwa. Meskipun tidak cocok untuk membuat program yang dapat dijalankan oleh CPU di komputer, ini bagus untuk membuat CPU yang sebenarnya. Ini adalah Bahasa Deskripsi Perangkat Keras, yang berarti dapat digunakan untuk merancang logika digital.

Akses seri Tutorial VHDL Dasar di sini!

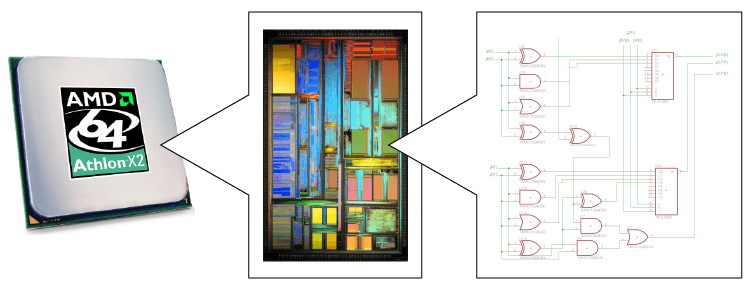

Perhatikan ilustrasi di atas. Di dalam chip CPU terdapat banyak sekali sirkuit elektronik digital (tengah). Sirkuit digital ini dapat ditampilkan menggunakan diagram skematik (kanan). Saat membuat chip sirkuit terintegrasi, seperti CPU, kita harus mulai dengan membuat diagram sirkuit logis di sebelah kanan.

Ini adalah asumsi yang adil bahwa diagram sirkuit semacam itu dibuat dalam semacam editor skematik, tetapi ini bukan cara melakukannya. Sirkuit dijelaskan dalam bahasa tekstual seperti VHDL.

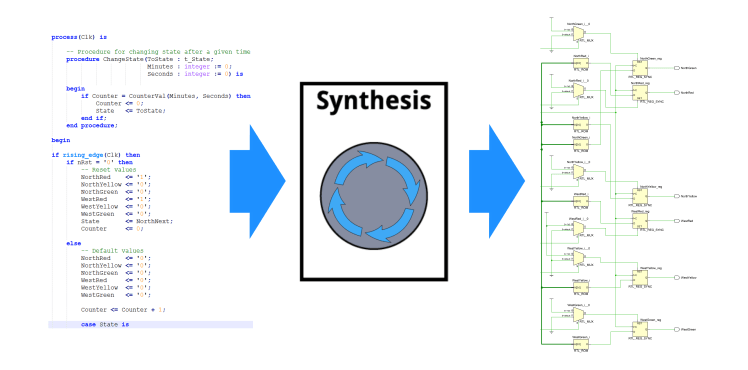

Alih-alih menggambar sirkuit yang tepat dalam editor skema, kami menggunakan VHDL untuk menggambarkan perilaku sirkuit yang diinginkan. Kode VHDL kemudian dapat diubah menjadi skema yang tepat dalam proses yang disebut sintesis . Alat sintesis adalah aplikasi perangkat lunak yang mengambil kode VHDL dan mencoba menemukan solusi yang mungkin untuk perilaku yang telah Anda jelaskan.

Jika berhasil, output dari synthesizer akan menjadi netlist yang selanjutnya dapat dilihat di editor skematik.

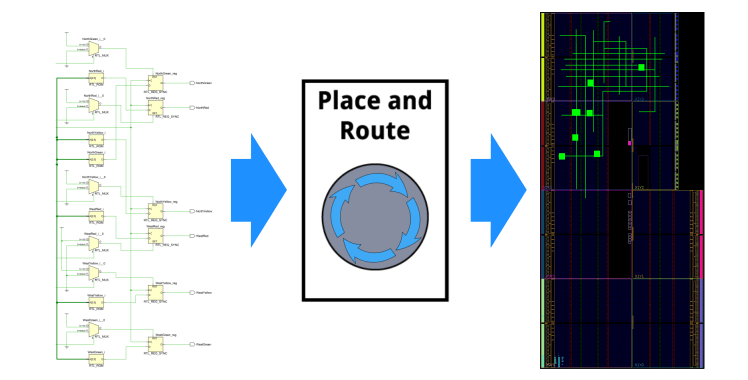

Sementara netlist memberikan deskripsi logis yang tepat dari rangkaian, tidak mengatakan apa-apa tentang implementasi fisik. Untuk mendapatkan deskripsi yang tepat dari tata letak fisik, netlist dijalankan melalui proses yang disebut tempat dan rute , atau PAR singkatnya. Router akan mencoba mengalokasikan elemen dari netlist ke komponen fisik pada perangkat target. Itu juga perlu merutekan kabel di antara semua komponen. Ini adalah teka-teki raksasa yang harus dipecahkan oleh router!

Jika berhasil, output dari PAR akan menjadi netlist jenis lain. Netlist ini berisi info penempatan dan perutean, dan khusus untuk jenis perangkat target. Jika perangkat target adalah FPGA, netlist yang dirutekan dapat diubah menjadi file pemrograman. Jika perangkat target adalah ASIC, semuanya akan menjadi sedikit lebih rumit.

Ini adalah semacam bahasa pemrograman yang digunakan untuk membuat logika digital untuk sirkuit terintegrasi.

Ikuti tutorial dasar VHDL di sini>>>P>

VHDL

Apa itu Golang? Go adalah bahasa pemrograman open source yang dikembangkan oleh Google. Ini adalah bahasa kompilasi yang diketik secara statis. Bahasa ini mendukung pemrograman bersamaan dan juga memungkinkan menjalankan beberapa proses secara bersamaan. Ini dicapai dengan menggunakan saluran, goro

Mentransmisi Pembentukan cairan logam, atau pengecoran biasanya mengacu pada cara pemesinan yang menuangkan logam cair ke dalam rongga pengecoran yang sesuai dengan bentuk dan ukuran bagian, dan kemudian didinginkan dan dipadatkan untuk mendapatkan blank atau bagian. Proses Teknologi Bagian peng

Apakah Anda memiliki gambar dalam pikiran yang ingin Anda buat? Pencetakan 3D memberi Anda platform untuk membuat objek dari imajinasi Anda dengan mudah. Baik Anda bekerja di bidang kedokteran, pendidikan, arsitektur, atau bidang lain yang digerakkan oleh teknologi, Pencetakan 3D sering kali berguna

N adalah huruf penting dalam pompa. Ini adalah angka yang membantu menghitung volume cairan dalam wadah, dan dapat digunakan dengan sejumlah unit. Dalam artikel ini, kami akan mengajari Anda cara menggunakan N untuk menyelesaikan masalah terkait pompa, reservoir, dan aliran fluida. Salah satu perta