Tertanam

Listrik cenderung membutuhkan biaya; biaya listrik yang tinggi sangat mahal. Adaptasi yang agak dipaksakan dari kutipan terkenal Lord Acton ini menangkap dua aspek penting dari desain semikonduktor dan konsumsi daya. Melihat konsumsi daya rata-rata dari waktu ke waktu, jelas bahwa chip dengan konsumsi daya tinggi akan dikenakan biaya tinggi. Pada perangkat portabel, lebih banyak daya berarti baterai yang lebih besar dan lebih mahal, atau masa pakai baterai yang lebih pendek. Selanjutnya, lebih banyak daya berarti kemasan yang lebih maju dan lebih mahal untuk menghilangkan panas yang dihasilkan. Ketiga faktor ini juga memiliki biaya efek riak dalam hal harga produk, margin keuntungan, dan kemungkinan sukses di pasar.

Kekhawatiran atas konsumsi daya jauh melampaui perangkat portabel yang berjalan setidaknya sebagian waktu dengan baterai. Perangkat bertenaga dinding juga dikenakan biaya tambahan dalam hal pengemasan, catu daya, dan sistem distribusi daya. Masalah yang sama ini meluas hingga ke peternakan server, dengan rak atau server komputasinya, susunan penyimpanan data yang sangat besar, dan sakelar jaringan. Biaya operasional untuk peternakan server sangat besar; penelitian telah menunjukkan bahwa tagihan listrik melebihi harga perangkat keras itu sendiri selama masa pakai setiap server. Peternakan server mungkin terletak di dekat bendungan pembangkit listrik tenaga air atau panel surya besar dalam upaya untuk memenuhi permintaan mereka yang tinggi. Beberapa lokasi juga harus memenuhi “hukum hijau” yang mengatur penarikan daya server.

Pada akhir yang tinggi, konsumsi daya yang berlebihan mungkin memerlukan sistem pendingin cair yang menambah infrastruktur besar dan biaya terkait. Untuk semua alasan ini, mengurangi konsumsi daya rata-rata adalah tujuan di hampir semua proyek semikonduktor, terlepas dari pasar akhir. Saat mempertimbangkan daya puncak, pengurangan mungkin merupakan kebutuhan kritis daripada sekadar tujuan. Beberapa chip dirancang sedemikian rupa sehingga hanya bagian tertentu yang dapat berjalan pada waktu yang sama. Dalam kasus seperti itu, mengaktifkan semua fungsi mungkin memerlukan lebih banyak penarikan arus daripada yang dapat ditangani perangkat, yang mengakibatkan kerusakan termal dan kerusakan permanen.

Tantangan analisis kekuatan

Mengingat semua motivasi untuk membatasi konsumsi daya, industri telah mengembangkan berbagai teknik desain daya rendah. Ini berkisar dari tweak sirkuit tingkat tata letak hingga manajemen daya berbasis perangkat lunak tingkat sistem, sadar aplikasi. Teknik apa pun yang digunakan, sangat berharga untuk dapat menilai dampaknya secara akurat dengan memperkirakan konsumsi daya rata-rata dan puncak selama desain dan verifikasi chip yang sedang dikembangkan. Tidak dapat diterima untuk menunggu sampai setelah fabrikasi untuk menemukan bahwa daya rata-rata terlalu tinggi untuk produk yang layak atau bahwa penarikan daya puncak menghancurkan chip. Analisis daya pra-silikon yang efektif, lebih disukai pada beberapa tahap dalam proyek, diperlukan.

Pendekatan tradisional industri elektronik-desain-otomatis untuk analisis daya bergantung pada simulasi. Verifikasi fungsional chip memerlukan pengembangan testbench dan kemudian menulis atau menghasilkan serangkaian tes yang memeriksa setiap fungsi atau fitur desain chip. Ini adalah masalah yang relatif sederhana untuk mensimulasikan seluruh rangkaian pengujian, atau mungkin hanya sebagian yang representatif, dan memasukkan hasilnya ke dalam alat penanda daya tradisional. Karena sebagian besar konsumsi daya hanya terjadi ketika sirkuit beralih status, simulator dapat menyediakan file aktivitas switching ke alat pemutus daya. Jika dikombinasikan dengan karakteristik daya di perpustakaan untuk teknologi target, alat ini dapat memberikan perkiraan yang cukup akurat untuk konsumsi daya rata-rata dan puncak.

Akurasi ini, bagaimanapun, sepenuhnya relatif terhadap tes yang dijalankan dalam simulasi. Dalam praktiknya, rangkaian uji verifikasi apa pun tidak mewakili operasi chip dengan perangkat lunak produksi yang berjalan. Pengujian yang dirancang untuk verifikasi fungsional, dengan maksud, berfokus pada stimulasi hanya area desain yang diperlukan untuk fitur yang ditargetkan. Testbenches acak terbatas dapat menghasilkan lebih banyak aktivitas paralel tetapi masih tidak mungkin untuk memodelkan penggunaan dunia nyata. Analisis daya yang benar-benar akurat hanya dapat dilakukan dengan menggunakan aktivitas peralihan dari beban kerja perangkat lunak yang sebenarnya, termasuk aplikasi pengguna yang berjalan di atas sistem operasi (OS).

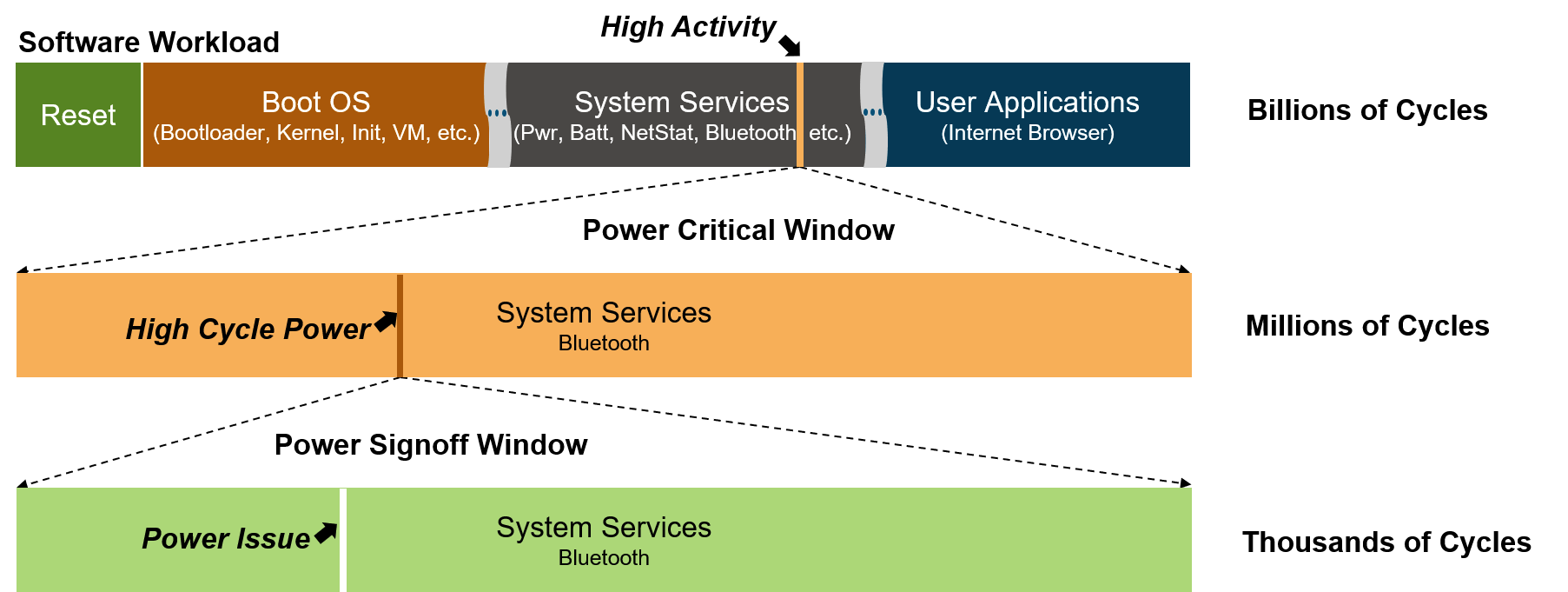

Biasanya diperlukan beberapa miliar siklus jam untuk mem-boot OS, memulai layanan sistem, dan menjalankan aplikasi. Ini akan sangat tidak praktis untuk dijalankan dalam simulasi. Sebaliknya, emulator secara rutin menjalankan miliaran siklus, dari boot OS hingga beberapa aplikasi pengguna yang berjalan secara paralel. Latihan emulasi hanya semacam beban kerja perangkat lunak nyata yang diperlukan untuk melakukan analisis daya dengan akurasi tinggi. Tantangannya adalah alat pemutus daya dirancang untuk menangani ribuan siklus, bukan jutaan, dan tentu saja bukan miliaran. Metodologi baru diperlukan untuk mengidentifikasi beberapa area aktivitas tinggi dalam menjalankan emulasi dan fokus hanya menggunakan jendela ini untuk analisis daya (Gambar 1).

klik untuk gambar lebih besar

Gambar 1. Analisis daya menggunakan power windows (Sumber:Synopsys)

Beralih ke analisis daya berbasis perangkat lunak

Persyaratan pertama untuk alur yang ditunjukkan pada Gambar 1 adalah agar emulator menghasilkan profil yang menunjukkan bagian desain mana yang aktif dari waktu ke waktu. Profil aktivitas ini dapat dilihat sebagai grafik dalam penampil bentuk gelombang atau alat debug perangkat keras lainnya. Karena pemutusan daya tidak dapat dilakukan pada miliaran siklus, langkah selanjutnya adalah bagi pengguna untuk memanfaatkan profil aktivitas untuk mengidentifikasi satu atau beberapa jendela kritis daya di mana aktivitasnya paling tinggi dan konsumsi dayanya kemungkinan besar juga paling tinggi. Jika masing-masing jendela ini dalam jutaan siklus, dapat digunakan untuk tahap analisis daya berikutnya. Sebagai tolok ukur, emulator harus mampu menghasilkan profil aktivitas untuk satu miliar siklus beban kerja perangkat lunak dalam tiga jam.

Tertanam

Analisis Kegagalan Kegagalan komponen dan rakitan peralatan, atau struktur dalam industri dapat menyebabkan hilangnya nyawa, penghentian tidak terjadwal, peningkatan biaya pemeliharaan dan perbaikan, dan perselisihan litigasi yang merusak. Untuk mencegah terulangnya kembali masalah yang disebabka

Analisis Daya Reaktif dalam Sistem Tenaga Daya reaktif adalah kekuatan imajiner, tetapi tetap diperlukan dalam Sistem Tenaga. Jika daya reaktif berlebihan dalam Sistem Tenaga, maka tegangan dapat naik dan jika terjadi kekurangan, tegangan daya reaktif mungkin rendah. Pada artikel ini, kami akan men

Bagaimana Menghitung Konsumsi Daya dan Energi dalam kWh? Kalkulator &Contoh Kalkulator Konsumsi Energi &Daya dalam kWh Masukkan alat listrik di menu tarik-turun atau masukkan peringkat watt manual dalam watt atau kilowatt (kW) dan penggunaan harian perangkat dalam jam. Klik tombol hitung untuk mene

Apakah Anda mencoba mencari tahu semua biaya yang terkait dengan pencetakan 3D? Nah, saya mengambil beberapa waktu untuk mengukur berapa banyak daya yang ditarik Ender 3 saya dengan menggunakan Monitor Penggunaan Listrik, dan saya menguji berapa banyak yang dikonsumsi saat mencetak PLA biasa dengan