Memulai Bahasa Deskripsi Perangkat Keras Verilog

Dalam artikel ini, kita akan mempelajari struktur dasar modul Verilog, lihat beberapa contoh penggunaan tipe data "kawat" Verilog dan bentuk vektor, dan secara singkat menyentuh beberapa perbedaan antara VHDL dan Verilog.

Dalam artikel ini, kita akan mempelajari struktur dasar modul Verilog, melihat beberapa contoh penggunaan tipe data “kawat” Verilog dan bentuk vektornya, dan secara singkat membahas beberapa perbedaan antara VHDL dan Verilog.

Verilog dan VHDL adalah dua bahasa yang umum digunakan untuk menggambarkan sirkuit digital. AAC memiliki serangkaian artikel teknis yang membahas konsep dasar VHDL. Artikel ini berfungsi sebagai titik awal untuk seri kami tentang Verilog.

Apakah Saya Membutuhkan Verilog dan VHDL?

Sebelum memulai diskusi kita, mari kita jawab pertanyaan yang jelas:apakah kita benar-benar perlu mengetahui kedua bahasa ini?

Baik Verilog dan VHDL adalah alat yang ampuh yang dapat digunakan untuk merancang sirkuit digital yang kompleks. Meskipun ada beberapa perbedaan antara kedua HDL ini, Anda bebas memilih salah satu untuk dikuasai dan digunakan. Namun, saya percaya bahwa pada titik tertentu, Anda akan mendapat manfaat dari memiliki setidaknya pemahaman dasar tentang kedua bahasa tersebut. Terkadang sebagai desainer, kami membutuhkan segmen kode sampel untuk mendapatkan ide tentang pengkodean proyek. Kami menjelajahi internet selama berjam-jam dan akhirnya menemukan apa yang kami butuhkan tetapi itu tidak masuk akal bagi kami—tertulis dalam HDL yang sama sekali asing bagi kami. Tanpa memiliki pemahaman dasar bahasa, kita mungkin tidak dapat sepenuhnya memahami tekniknya.

Evolusi Verilog

Verilog dirancang pada awal 1984 oleh Gateway Design Automation (sekitar tiga tahun setelah VHDL diprakarsai oleh Departemen Pertahanan AS). Dengan dukungan DoD, VHDL menjadi standar IEEE pada tahun 1987. Verilog baru muncul pada tahun 1995. Saat ini, VHDL dan Verilog adalah HDL populer dan alat desain FPGA biasanya mendukung kedua bahasa tersebut.

Kata “Verilog” adalah portmanteau dari kata “verifikasi” dan “logika” karena bahasa ini pertama kali diusulkan sebagai alat simulasi dan verifikasi. Mari kita mulai dengan konsep dan sintaks Verilog.

Contoh 1

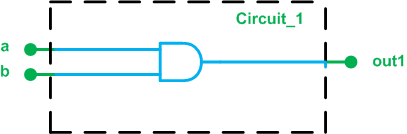

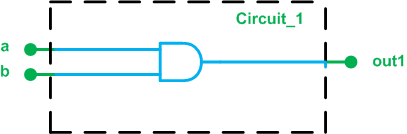

Sebagai contoh pertama, mari kita tulis kode Verilog untuk rangkaian yang digambarkan pada Gambar 1.

Gambar 1. Sirkuit_1

Ada dua input dan satu output. Semua port berukuran satu bit. Fungsi dari rangkaian ini adalah untuk AND dua input dan menempatkan hasilnya pada port out1.

Satu kemungkinan deskripsi Verilog untuk modul Circuit_1 adalah:

Baris 1 dan 8

Kedua baris ini menggunakan kata kunci "modul" dan "endmodule" untuk menentukan bahwa garis di antara (baris 2 hingga 7) semuanya menggambarkan sirkuit bernama "Circuit_1". Nama ini arbitrer dan memungkinkan kita untuk merujuk ke sirkuit ini nanti.

Baris 2 hingga 6

Baris-baris ini menentukan antarmuka "Circuit_1" dengan lingkungan sekitarnya. Port input dan output dijelaskan menggunakan kata kunci “input” dan “output”. Kata kunci ini diikuti oleh kata kunci lain "kawat" dan kemudian nama port (Lihat Gambar 1). Apa yang ditentukan oleh kata kunci "kawat"? "Kawat" adalah tipe data Verilog yang mewakili kabel fisik dalam desain. Kami akan membahas tipe data Verilog secara lebih rinci di artikel mendatang tetapi untuk saat ini, kami tahu bahwa akan ada tiga kabel yang disebut a, b, dan out1 dalam modul kami dan karena ini ditentukan dalam deklarasi port, mereka sesuai dengan antarmuka modul.

Baris 7

Baris ini menggunakan operator AND bitwise, yaitu &, untuk menggambarkan fungsionalitas rangkaian. Kata kunci “assign” menempatkan a&b pada output port out1. Jenis penugasan ini disebut penugasan berkelanjutan. Disebut demikian karena penetapan selalu aktif setiap kali operan di sisi kanan berubah, a&b dievaluasi dan ditetapkan ke out1. Kita dapat membayangkan penugasan berkelanjutan sebagai rangkaian kombinasional yang outputnya terus diperbarui tergantung pada inputnya. Dalam contoh kita, rangkaian kombinasional ini adalah gerbang AND sederhana. Ada juga tugas prosedural di Verilog HDL yang akan dibahas di artikel mendatang.

Sekarang, kita dapat menggunakan paket perangkat lunak seperti Xilinx ISE untuk memverifikasi kode di atas. Anda dapat menemukan tutorial perangkat lunak ini berbasis Verilog di sini (PDF).

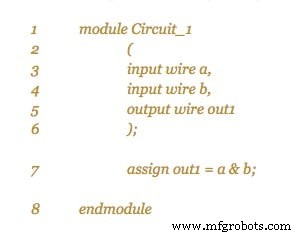

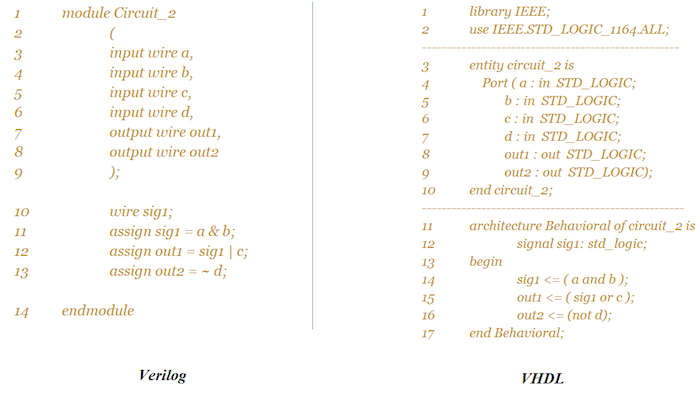

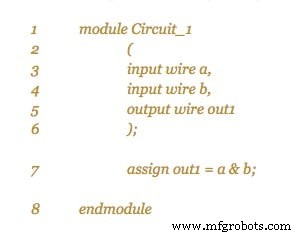

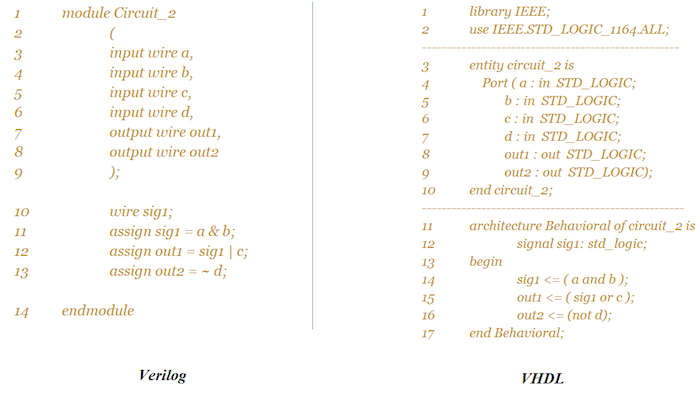

Membandingkan Contoh 1 dengan Kode VHDL

Gambar 2 di bawah menunjukkan deskripsi Verilog dan VHDL untuk modul Circuit_1.

Gambar 2. Perbandingan deskripsi Verilog dan VHDL untuk Circuit_1.

Seperti yang Anda lihat, kita harus menyertakan beberapa library saat coding di VHDL. Pustaka ini memberikan definisi untuk tipe data dan operator. Mempertimbangkan penambahan pustaka ini dan format umum VHDL, kami mengamati bahwa kode VHDL lebih bertele-tele. Namun, verboseness ini bukan tanpa keuntungan. Misalnya, fitur manajemen perpustakaan VHDL dapat membantu ketika memodelkan sistem tingkat yang lebih tinggi. Di artikel mendatang, kami sesekali akan membahas pro dan kontra dari kedua HDL ini.

Verilog memiliki Sistem Empat-Nilai

Ada empat nilai dasar yang digunakan di sebagian besar tipe data Verilog. Kabel yang ditentukan dalam Daftar 1 dapat memiliki salah satu nilai berikut:

- 0:untuk kondisi logika rendah atau salah

- 1:untuk kondisi logika high atau true

- z:untuk keadaan impedansi tinggi (dapat digunakan untuk menggambarkan keluaran buffer tri-status)

- x:untuk nilai yang tidak penting atau tidak diketahui (bila input tidak diinisialisasi atau dua atau lebih output yang bertentangan dihubungkan bersama).

Tipe data std_logic VHDL dapat mengambil sembilan nilai yang berbeda tetapi nilai yang umum digunakan adalah '0', '1', 'Z', dan '-' ('-' menunjukkan a tidak peduli).

Contoh 2

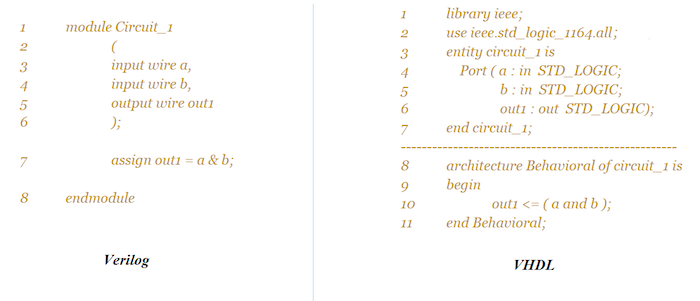

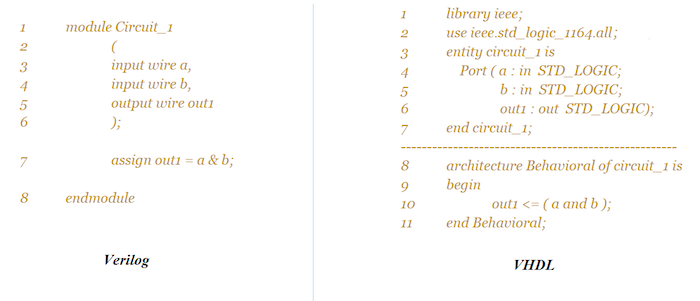

Sebagai contoh lain, mari kita tulis kode Verilog untuk rangkaian (yang akan kita beri label Circuit_2) yang ditunjukkan pada Gambar 3.

Gambar 3. Sirkuit_2

Kode Verilog berikut menjelaskan sirkuit ini:

Elemen yang digunakan dalam kode di atas mirip dengan yang ada pada Contoh 1, kecuali bahwa sinyal internal didefinisikan pada baris 10 kode. Kata kunci "kawat" digunakan untuk menentukan tipe data koneksi ini. Seperti dibahas di atas, tipe data “kawat” akan diterjemahkan menjadi kabel fisik dalam desain.

Kode di atas juga menggunakan beberapa operator bitwise Verilog baru:~ untuk NOT dan | untuk operasi ATAU. Operator bitwise lain yang berguna adalah ^ untuk operasi XOR. Gambar 4 menunjukkan deskripsi Verilog dan VHDL untuk modul Circuit_2. Perbandingan tersebut dapat membantu Anda melihat perbedaan dan persamaan antara kedua bahasa ini.

Gambar 4. Perbandingan deskripsi Verilog dan VHDL untuk Circuit_2.

Contoh 3

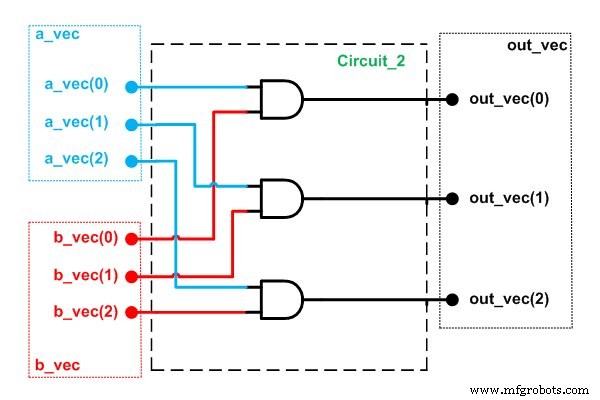

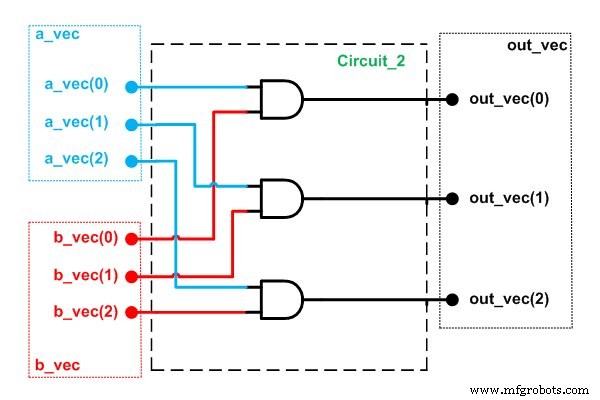

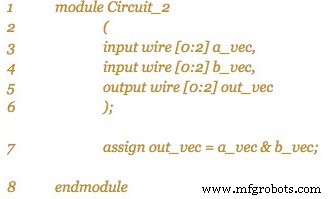

Untuk contoh ketiga dan terakhir kami, kami akan memberikan kode Verilog untuk skema yang ditunjukkan pada Gambar 5.

Gambar 5. Skema misalnya 3.

Seperti yang Anda lihat, ada hubungan tertentu antara port input biru dan port merah:input yang sesuai digabungkan dengan operator AND. Hasilnya ditugaskan ke port output. Dalam kasus seperti itu, kita dapat mengelompokkan sinyal dan memperlakukannya sebagai vektor. Ini membuat kode menjadi ringkas dan mudah dibaca.

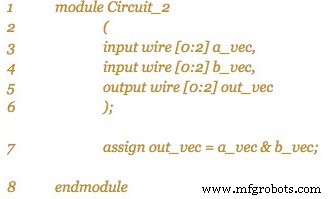

Menggunakan konsep vektor di Verilog, kita dapat dengan mudah memperluas kode di Daftar 1 untuk menggambarkan rangkaian di atas (Lihat kode di Daftar 3 di bawah).

Perhatikan bahwa rentang indeks vektor dapat berupa menaik ([0:2] seperti yang digunakan di atas) atau menurun ([2:0]). Meskipun format menaik digunakan di atas, biasanya kurang rawan kesalahan untuk menggunakan bentuk menurun. Hal ini disebabkan oleh fakta bahwa gaya menurun sesuai dengan persepsi kita bahwa posisi paling kiri dari bilangan biner memiliki indeks tertinggi. Perhatikan bahwa vektor juga digunakan dalam VHDL.

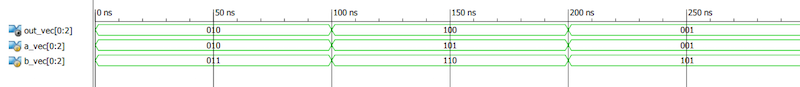

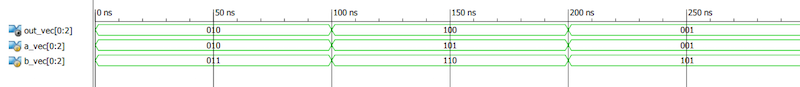

Gambar 6 di bawah ini menunjukkan simulasi ISE dari kode di Listing 3.

Gambar 6. Simulasi ISE dari kode Contoh 3.

Dalam artikel ini, kami membahas bahwa mempelajari VHDL dan Verilog adalah ide yang bagus, kami mempelajari struktur dasar modul Verilog, dan kami mengenal tipe data "kawat" Verilog dan bentuk vektornya. Kami juga secara singkat menyentuh beberapa perbedaan antara VHDL dan Verilog. Artikel berikutnya dalam seri Verilog kami akan membahas merancang sirkuit kombinasional di Verilog.