Tertanam

06 Januari 2019 oleh Dr. Steve Arar

Artikel ini memperkenalkan teknik untuk mendeskripsikan rangkaian kombinasional di Verilog dengan memeriksa cara menggunakan operator kondisional untuk mendeskripsikan tabel kebenaran kombinasional. Ini juga menunjukkan cara menggunakan blok “selalu” Verilog untuk mendeskripsikan sirkuit kombinasional—blok “selalu” dapat memberi kita solusi yang lebih mudah untuk mendeskripsikan sirkuit digital.

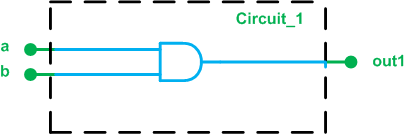

Dalam artikel sebelumnya, kami membahas penggunaan kata kunci “assign” Verilog untuk melakukan penugasan berkelanjutan. Penugasan seperti itu selalu aktif dan dapat digunakan untuk memperoleh deskripsi tingkat gerbang dari sirkuit digital. Sebagai contoh, dalam kode berikut, yang menjelaskan gerbang AND, ruas kanan dievaluasi secara terus menerus dan hasilnya diletakkan pada jaring keluar1:

tetapkan out1 =a &b; Verilog memiliki operator kondisional (?:) yang memungkinkan kita untuk memeriksa kondisi sebelum membuat penugasan tersebut. Sintaksnya diberikan di bawah ini:

tetapkan [signal_name] =[conditional_expression] ? [value_if_true] :[value_if_false]; The "conditional_expression" dievaluasi. Jika benar, “value_if_true” ditetapkan ke “signal_name”. Jika tidak benar, “signal_name” mendapat “value_if_false”. Sebagai contoh, perhatikan kode berikut:

assign out1 =(sel) ? (a &b) :(a|b); Jika "sel" benar, a&b akan ditetapkan ke "out1". Jika tidak benar, “out1” akan mendapatkan a|b. Oleh karena itu, kode di atas mengimplementasikan fungsionalitas multiplekser 2-ke-1. Implementasi konseptual dari kode ini dapat dilihat pada Gambar 1 di bawah ini.

Penugasan bersyarat memungkinkan kita untuk memiliki deskripsi yang lebih abstrak dari sirkuit tertentu karena memiliki fungsi pernyataan "jika" yang ditemukan dalam bahasa pemrograman komputer tradisional. Operator kondisional dapat digunakan dalam bentuk bersarang untuk mengimplementasikan sirkuit yang lebih kompleks. Contoh 1 membahas detail ini.

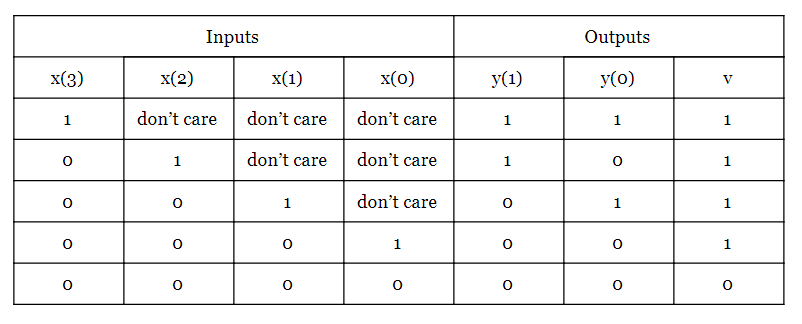

Gunakan operator kondisional (?:) untuk mendeskripsikan encoder prioritas 4-ke-2 dengan tabel kebenaran berikut:

Kode Verilog untuk encoder prioritas ini diberikan di bawah ini:

modul Prio_4_to_2 ( kabel input [3:0] x, kabel output [1:0] y, kabel output v ); tetapkan y =x[3] ? 2'b11 :x[2] ? 2'b10 :x[1] ? 2'b01 :2'b00; tetapkan v =( x[3] | x[2] | x[1] | x[0] ) ? 1'b1 :1'b0; modul akhir Selain baris 7 hingga 10, kode tersebut berisi elemen bahasa dasar yang dibahas dalam artikel kami sebelumnya. Jadi mari kita lihat baris-baris ini.

Istilah 2'b11, 2'b10, 2'b01 mengacu pada notasi Verilog yang mewakili bilangan biner dua bit. Secara umum, angka pertama (sebelum 'b) menentukan jumlah bit. Huruf b menyatakan bahwa bilangan adalah biner. Digit setelah 'b memberikan nilai nomor. Oleh karena itu, 2'b01 adalah notasi Verilog untuk mewakili bilangan biner dua bit dengan nilai 01 dan 3'b100 menunjukkan bilangan biner tiga bit dengan nilai 100.

Baris 7 memeriksa MSB input, x[3], dalam operator bersyarat. Jika x[3]=1, kondisi dievaluasi sebagai benar dan 2'b11 ditetapkan ke y (nilai yang ditetapkan diambil dari tabel kebenaran). Jika x[3]=0, kondisi dievaluasi sebagai salah dan ekspresi setelah titik dua (:) akan ditetapkan ke y. Ekspresi setelah titik dua adalah kode di Baris 8 yang merupakan operator kondisional lainnya.

Operator kondisional kedua di Baris 8 memeriksa bit input paling signifikan kedua, x[2], untuk menentukan apakah 2'b10 harus ditetapkan ke y atau ekspresi setelah titik dua yang lagi-lagi merupakan operator kondisional lain (Baris 9) harus dievaluasi. Anda dapat memverifikasi bahwa nilai yang ditetapkan untuk y cocok dengan tabel kebenaran yang diberikan.

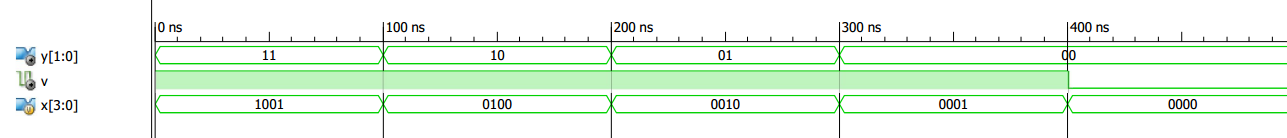

Output yang valid (v) dari tabel kebenaran akan berlogika tinggi jika setidaknya satu bit dari input berlogika tinggi. Baris 11 menunjukkan deskripsi ini dengan menerapkan operator OR bitwise (|) ke bit input. Simulasi Xilinx ISE dari kode di atas ditunjukkan pada Gambar 2.

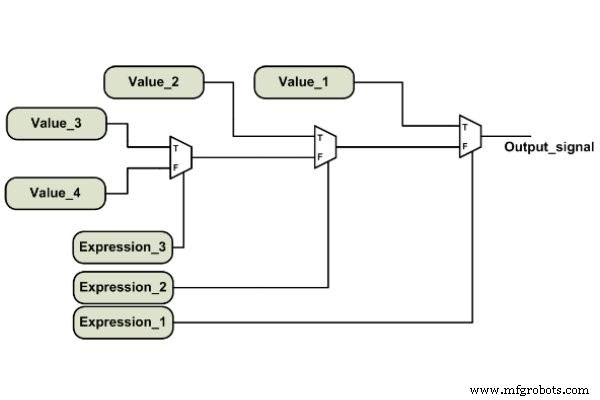

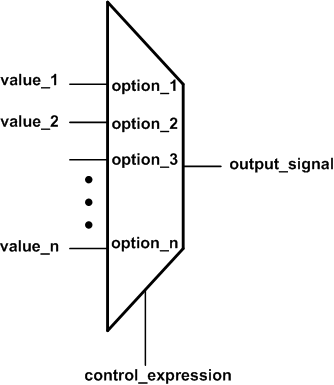

Penting untuk dicatat bahwa ekspresi kondisional dievaluasi secara berurutan hingga ekspresi yang benar ditemukan. Penugasan yang sesuai dengan ekspresi sebenarnya ini akan dilakukan. Akibatnya, ekspresi yang dievaluasi sebelumnya memiliki prioritas lebih tinggi dibandingkan dengan yang berikutnya. Ini berarti, secara teoritis, operator kondisional lebih cocok untuk mengimplementasikan jaringan prioritas (Gambar 3) daripada struktur yang seimbang seperti multiplekser (Gambar 4).

Artikel sebelumnya mengungkapkan diskusi serupa tentang penetapan serentak VHDL.

Kita dapat memisahkan rangkaian kombinasional apa pun menjadi beberapa gerbang logika dasar (AND, OR, NOT, dll.) dan menggunakan pernyataan "assign" untuk mendeskripsikan gerbang ini (deskripsi tingkat gerbang). Kita juga dapat menggunakan operator kondisional yang dibahas di bagian sebelumnya untuk mendapatkan cara yang lebih abstrak dalam mendeskripsikan beberapa rangkaian kombinasional (mirip dengan pernyataan “jika” dalam bahasa pemrograman komputer). Namun, masih ada solusi yang lebih kuat:menggunakan blok “selalu” Verilog.

Di dalam blok "selalu", kita dapat memiliki pernyataan prosedural yang dieksekusi secara berurutan. Selain itu, blok "selalu" mendukung konstruksi bahasa abstrak seperti pernyataan "jika" dan "kasus".

Fitur eksekusi sekuensial bersama dengan konstruksi bahasa abstrak yang tersedia dalam blok "selalu" memungkinkan kita untuk lebih mudah menggambarkan fungsionalitas sirkuit, karena fakta bahwa penalaran manusia memiliki sifat sekuensial dan bergantung pada deskripsi abstrak. Kami biasanya berpikir dalam mode tingkat tinggi algoritmik daripada dalam hal gerbang logika tingkat rendah. Blok "selalu" dapat memberi kita solusi yang lebih mudah untuk menggambarkan sirkuit digital. Untuk detail selengkapnya tentang mengapa HDL mendukung deskripsi berdasarkan pernyataan berurutan, silakan lihat artikel saya Pengantar Pernyataan VHDL Berurutan.

Sintaks sederhana dari blok "selalu" diberikan di bawah ini:

selalu @(sensitivity_list) mulai sekuensial_pernyataan; akhir Sensitivitas_list menentukan kapan pernyataan berurutan di dalam blok "selalu" harus dieksekusi. Misalnya, pertimbangkan untuk menggunakan blok “selalu” untuk menggambarkan rangkaian pada Gambar 5.

Ketika a atau b berubah, output dapat berubah, yang berarti a dan b harus berada dalam daftar sensitivitas blok "selalu". Secara umum, untuk rangkaian kombinasional, semua sinyal input harus dimasukkan dalam daftar sensitivitas.

Sekarang, kita dapat menggunakan operator AND bitwise untuk menggambarkan fungsionalitas rangkaian (a&b) dan menetapkan hasilnya ke output. Dalam blok “selalu”, ada dua jenis penetapan yang berbeda:penetapan pemblokiran (=) dan penetapan non-pemblokiran (<=). Menggunakan tugas pemblokiran, kami mendapatkan kode berikut:

selalu @(a, b)mulai1 =a &b;akhir Apa perbedaan antara penetapan pemblokiran dan penugasan non-pemblokiran?

Dengan tugas pemblokiran, sisi kanan dievaluasi dan segera ditugaskan ke out1. Oleh karena itu, ketika Baris 3 dijalankan, out1 segera diperbarui sebelum kita melanjutkan ke baris kode berikutnya. Nama "pemblokiran tugas" menekankan bahwa baris yang akan datang diblokir sampai sisi kiri diperbarui.

Dengan penugasan non-pemblokiran, ekspresi tangan kanan dievaluasi tetapi tidak diterapkan ke variabel tangan kiri sampai kita mencapai akhir blok "selalu". Pilihan tugas pemblokiran atau non-pemblokiran dapat membingungkan bagi pemula dan penggunaan yang tidak tepat dapat menyebabkan fungsi yang tidak diinginkan. Misalnya, menggunakan penetapan pemblokiran untuk menyimpulkan sandal jepit dapat menyebabkan kondisi balapan.

Untuk artikel pengantar ini, kami tidak akan membahas lebih lanjut dan kami hanya akan berpegang pada satu pedoman sederhana untuk menghindari potensi jebakan:Gunakan tugas pemblokiran saat menulis kode untuk rangkaian kombinasional. Oleh karena itu, blok “selalu” di Daftar 1 akan digunakan untuk menggambarkan gerbang AND.

Dalam artikel sebelumnya, kami mengenal tipe data "kawat" Verilog. Tipe data ini mewakili kabel fisik dalam desain FPGA kami. Dalam blok "selalu", standar Verilog tidak mengizinkan kami untuk menetapkan nilai ke "kawat". Sebagai gantinya, kami menggunakan tipe data "reg". Nama "reg" agak membingungkan, tetapi perhatikan bahwa "reg" mungkin atau mungkin tidak mengarah ke elemen penyimpanan fisik dalam desain Anda. Kode berikut adalah deskripsi Verilog dari Gambar 5 menggunakan blok "selalu". Perhatikan bahwa tipe data keluaran harus "reg" karena mendapatkan nilainya dari penugasan prosedural.

modul Circuit_1 ( kabel input a, kabel input b, output reg out1 ); selalu @ (a, b) mulai keluar1 =a &b; endmodule Pada artikel ini, kita mengenal operator kondisional Verilog. Kami menggunakan bentuk bersarang dari operator ini untuk menggambarkan encoder prioritas. Kemudian, kami menyentuh konstruksi bahasa yang lebih kuat, blok "selalu", untuk menggambarkan sirkuit kombinasional. Di artikel mendatang, kita akan membahas penggunaan blok “always” untuk mengimplementasikan rangkaian sekuensial.

Tertanam

Konvensi leksikal di Verilog mirip dengan C dalam arti bahwa ia berisi aliran token. Token leksikal dapat terdiri dari satu atau lebih karakter dan token dapat berupa komentar, kata kunci, angka, string, atau spasi. Semua baris harus diakhiri dengan tanda titik koma ; . Verilog peka huruf besar/kec

Sebuah module adalah blok kode Verilog yang mengimplementasikan fungsi tertentu. Modul dapat disematkan di dalam modul lain dan modul tingkat yang lebih tinggi dapat berkomunikasi dengan modul tingkat yang lebih rendah menggunakan port input dan outputnya. Sintaks Sebuah modul harus diapit dalam mo

Sinyal tipe wire atau kabel serupa seperti tipe data memerlukan penetapan nilai yang berkelanjutan. Misalnya, pertimbangkan kabel listrik yang digunakan untuk menghubungkan potongan-potongan pada papan tempat memotong roti. Selama baterai +5V diterapkan ke salah satu ujung kabel, komponen yang terhu

Sebuah always blok adalah salah satu prosedur blok di Verilog. Pernyataan di dalam blok selalu dieksekusi secara berurutan. Sintaks always @ (event) [statement] always @ (event) begin [multiple statements] end always blok dieksekusi pada beberapa acara tertentu. Acara ditentukan oleh da