ADC Perkiraan Berturut-turut

Salah satu metode untuk mengatasi kekurangan digital ramp ADC adalah apa yang disebut successive-approximation ADC. Satu-satunya perubahan dalam desain ini adalah rangkaian penghitung yang sangat khusus yang dikenal sebagai register aproksimasi berurutan .

Alih-alih menghitung dalam urutan biner, register ini menghitung dengan mencoba semua nilai bit yang dimulai dengan bit yang paling signifikan dan diakhiri dengan bit yang paling tidak signifikan. Selama proses pencacahan, register memonitor keluaran komparator untuk melihat apakah bilangan biner kurang dari atau lebih besar dari masukan sinyal analog, menyesuaikan nilai bit yang sesuai.

Cara penghitungan register identik dengan metode "trial-and-fit" dari konversi desimal ke biner, di mana nilai bit yang berbeda dicoba dari MSB ke LSB untuk mendapatkan bilangan biner yang sama dengan bilangan desimal aslinya. Keuntungan dari strategi penghitungan ini adalah hasil yang jauh lebih cepat:keluaran DAC menyatu pada masukan sinyal analog dalam langkah yang jauh lebih besar dibandingkan dengan urutan penghitungan 0-hingga-penuh dari pencacah biasa.

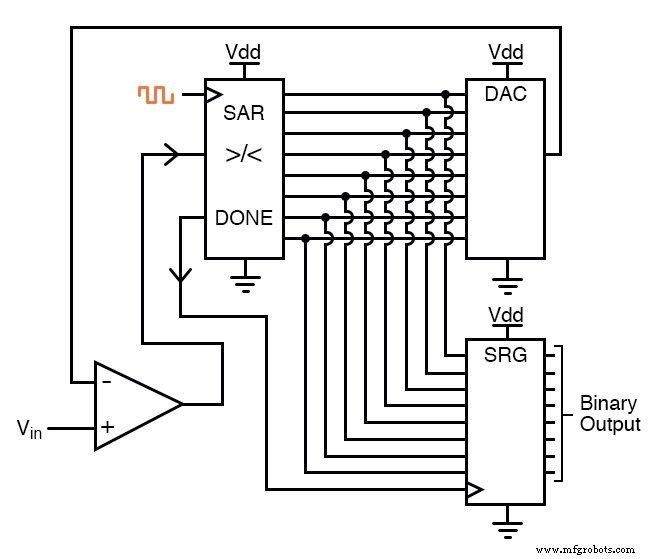

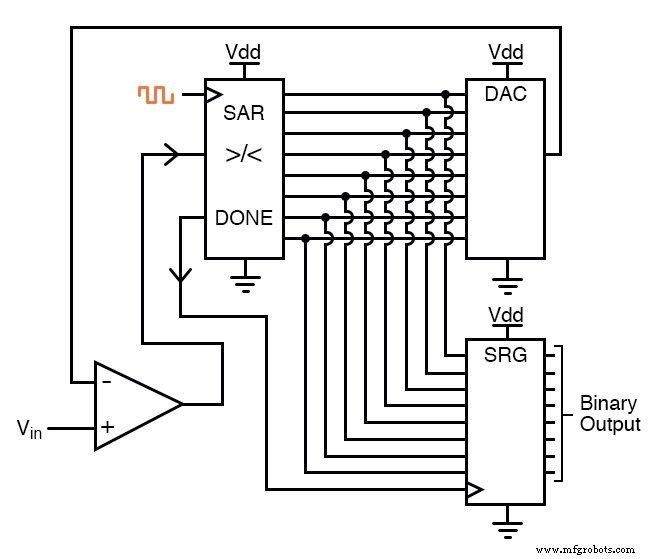

Tanpa menunjukkan cara kerja bagian dalam dari successive-approximation register (SAR), rangkaiannya terlihat seperti ini:

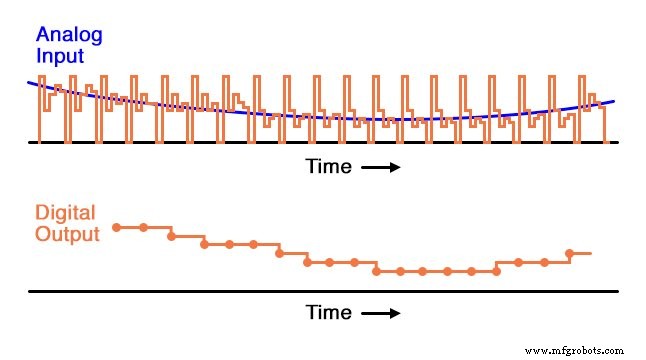

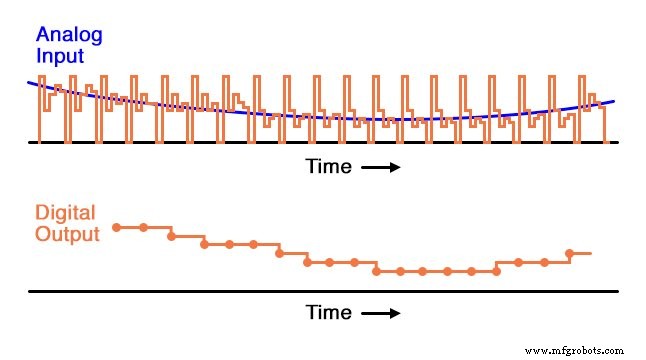

Perlu dicatat bahwa SAR umumnya mampu mengeluarkan angka biner dalam serial (satu per satu) format, sehingga menghilangkan kebutuhan untuk register geser. Diplot dari waktu ke waktu, operasi ADC aproksimasi berurutan terlihat seperti ini:

Perhatikan bagaimana pembaruan untuk ADC ini terjadi secara berkala, tidak seperti sirkuit ADC ramp digital.

LEMBAR KERJA TERKAIT:

- Lembar Kerja ADC Perkiraan Berturut-turut