Shift Registers:Konversi Serial-in, Parallel-out (SIPO)

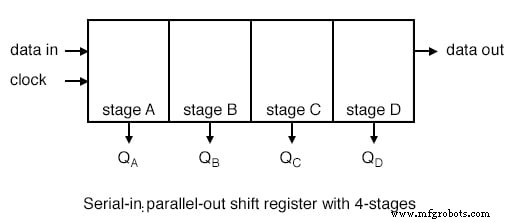

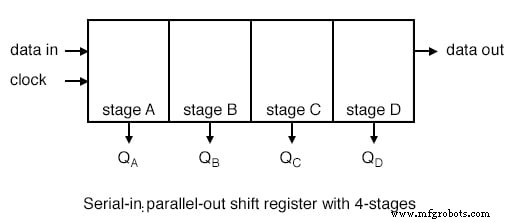

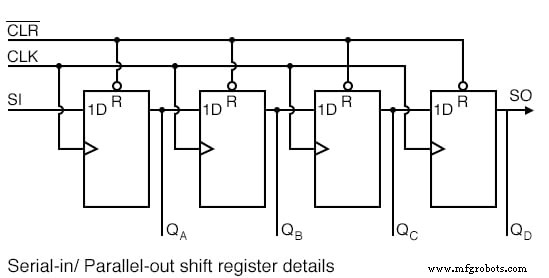

Shift register serial-in, parallel-out mirip dengan shift register serial-in, serial-out yang memindahkan data ke elemen penyimpanan internal dan memindahkan data keluar pada pin serial-out, data-out.

Ini berbeda karena membuat semua tahapan internal tersedia sebagai output. Oleh karena itu, register geser serial-in, paralel-out mengubah data dari format serial ke format paralel.

Contoh Penggunaan Register Geser Serial-in, Parallel-out

Jika empat bit data digeser oleh empat pulsa clock melalui satu kabel pada data-in, di bawah ini, data menjadi tersedia secara bersamaan pada empat Output QA ke TD setelah pulsa jam keempat.

Aplikasi praktis dari register geser serial-in, paralel-out adalah untuk mengubah data dari format serial pada kabel tunggal ke format paralel pada beberapa kabel.

Mari kita nyalakan empat LED (light emitting diodes) dengan empat output (QA TB TC TB ).

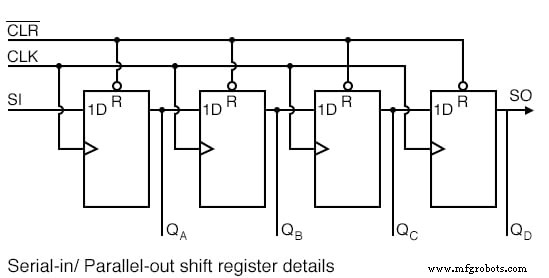

Rincian di atas dari register geser serial-in, paralel-out cukup sederhana. Sepertinya register geser serial-masuk, keluar-seri dengan ketukan ditambahkan ke setiap keluaran tahap.

Data serial bergeser di SI (Masukan Seri). Setelah jumlah clock sama dengan jumlah tahapan, bit data pertama di muncul di SO (QD ) pada gambar di atas.

Secara umum, tidak ada pin SO. Tahap terakhir (QD di atas) berfungsi sebagai SO dan di-cascade ke paket berikutnya jika ada.

Serial-in, Parallel-out vs. Register Geser Serial-in, Serial-out

Jika register geser serial-in, paralel-out sangat mirip dengan register geser serial-in, serial-out, mengapa produsen repot-repot menawarkan kedua jenis?

Mengapa tidak menawarkan register geser serial-in, paralel-out?

Jawabannya adalah mereka sebenarnya hanya menawarkan register geser serial-in, paralel-out, asalkan tidak lebih dari 8-bit.

Perhatikan bahwa register geser serial-in, serial-out datang lebih besar dari panjang 8-bit dari 18 hingga 64-bit.

Tidak praktis untuk menawarkan register geser 64-bit serial-in, paralel-out yang membutuhkan banyak pin output. Lihat bentuk gelombang di bawah untuk register geser di atas.

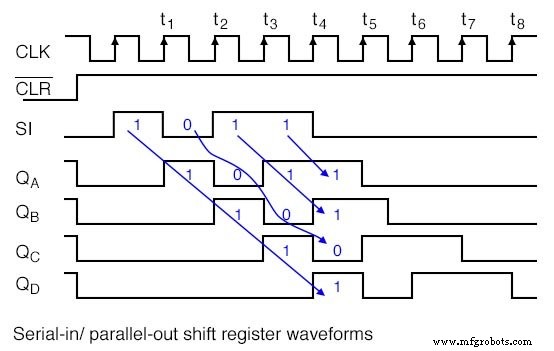

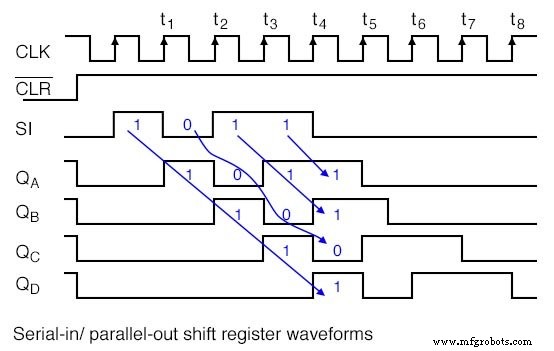

Register geser telah dibersihkan sebelum data apa pun oleh CLR' , sinyal rendah aktif, yang menghapus semua Flip-Flop tipe D dalam register geser.

Perhatikan data serial 1011 pola yang disajikan di SI memasukkan. Data ini disinkronkan dengan jam CLK .

Ini akan menjadi kasus jika sedang digeser dari sesuatu seperti register geser lain, misalnya, register geser paralel-in, serial-out (tidak ditampilkan di sini).

Pada jam pertama di t1 , datanya 1 di SI digeser dari D untuk T dari tahap register geser pertama. Setelah t2 bit data pertama ini berada di QB .

Setelah t3 ada di QC . Setelah t4 ada di QD . Empat pulsa clock telah menggeser bit data pertama hingga tahap terakhir QD .

Data kedua sedikit 0 ada di QC setelah jam ke-4. Data ketiga sedikit 1 ada di QB . Data keempat menggigit 1 . lainnya ada di QA .

Jadi, pola input data serial 1011 terkandung dalam (QD TC TB TJ ). Sekarang tersedia di empat keluaran.

Ini akan tersedia pada empat output dari tepat setelah jam t4 tepat sebelum t5 .

Data paralel ini harus digunakan atau disimpan di antara dua waktu ini, atau akan hilang karena menggeser QD panggung pada jam berikut t5 ke t8 seperti yang ditunjukkan di atas.

Perangkat Serial-in, Parallel-out

Mari kita lihat lebih dekat register geser serial-in, paralel-out yang tersedia sebagai sirkuit terintegrasi, milik Texas Instruments.

Untuk lembar data perangkat lengkap, ikuti tautannya.

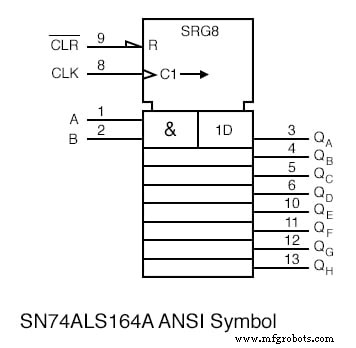

- SN74ALS164A register geser 8-bit serial-in/parallel-out

- SN74AHC594 register geser 8-bit serial-in/ parallel-out dengan register keluaran

- SN74AHC595 register geser 8-bit serial-in/ parallel-out dengan register keluaran

- register geser 8-bit serial-in/parallel-out CD4094 dengan register keluaran

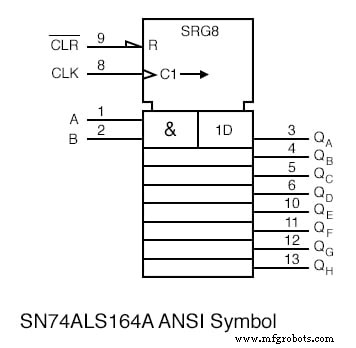

74ALS164A hampir identik dengan diagram kami sebelumnya dengan pengecualian dua input serial A dan B .

Input yang tidak digunakan harus ditarik tinggi untuk mengaktifkan input lainnya. Kami tidak menampilkan semua tahapan di atas.

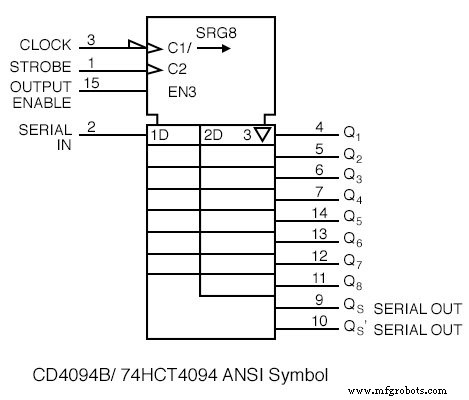

Namun, semua output ditampilkan pada simbol ANSI di bawah ini, bersama dengan nomor pin.

CLK input ke bagian kontrol simbol ANSI di atas memiliki dua fungsi internal C1 , kontrol apa pun dengan awalan 1 .

Ini akan mencatat data pada 1H . Fungsi kedua, tanda panah setelah garis miring (/) adalah pemindahan data ke kanan (bawah) di dalam register geser.

Delapan output tersedia di sebelah kanan delapan register di bawah bagian kontrol. Tahap pertama lebih lebar dari yang lain untuk mengakomodasi A&B masukan.

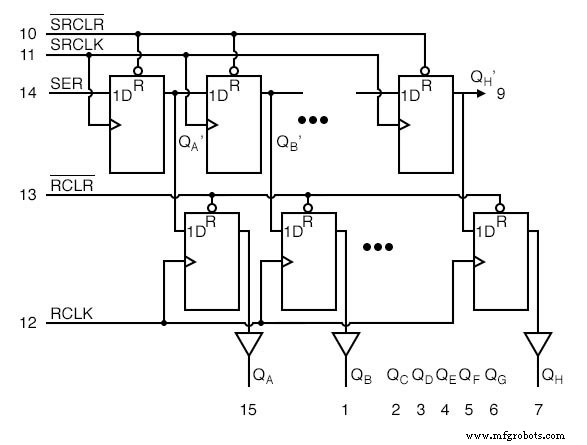

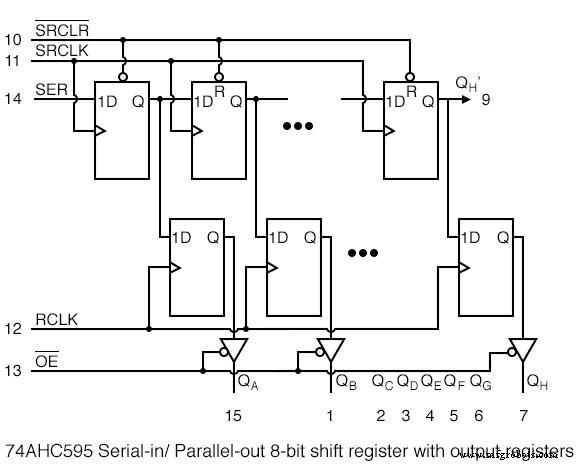

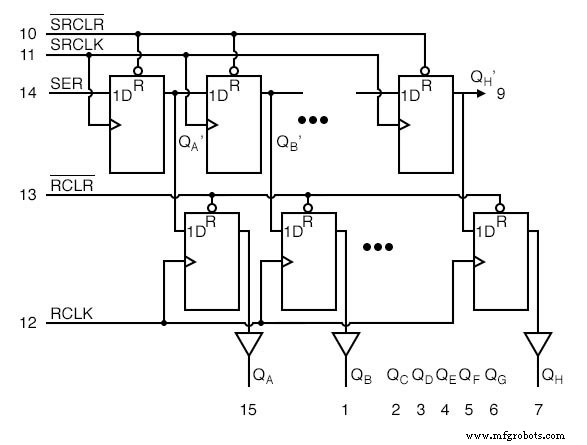

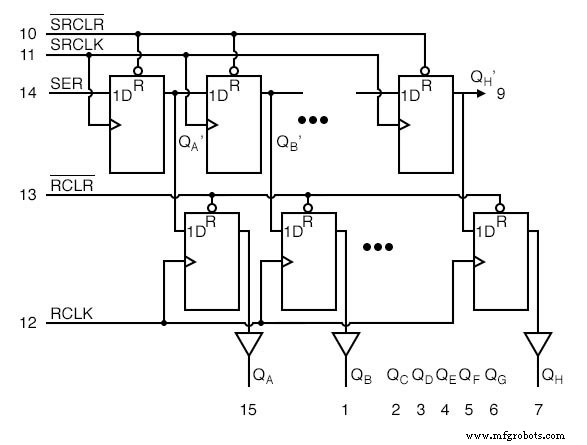

Diagram logika internal di atas diadaptasi dari lembar data TI (Texas Instruments) untuk 74AHC594. FF tipe “D” di baris atas terdiri dari register geser serial-in, paralel-out.

Bagian ini berfungsi seperti perangkat yang dijelaskan sebelumnya. Keluaran (QA ’ TB ' ke TH ' ) dari setengah register geser perangkat mengumpankan FF tipe "D" di bagian bawah secara paralel. TH ' (pin 9) dipindahkan ke paket perangkat kaskade opsional.

Satu sisi jam positif di RCLK akan mentransfer data dari D untuk T dari FF yang lebih rendah. Semua transfer 8-bit secara paralel ke output register (kumpulan elemen penyimpanan).

Tujuan register keluaran adalah untuk mempertahankan keluaran data yang konstan saat data baru dipindahkan ke bagian register geser atas.

Ini diperlukan jika output menggerakkan relai, katup, motor, solenoida, klakson, atau bel. Fitur ini mungkin tidak diperlukan saat mengemudikan LED selama kedipan selama pemindahan gigi tidak menjadi masalah.

Perhatikan bahwa 74AHC594 memiliki jam terpisah untuk register geser (SRCLK ) dan register keluaran ( RCLK ). Selain itu, shifter dapat dibersihkan dengan SRCLR dan, register keluaran oleh RCLR .

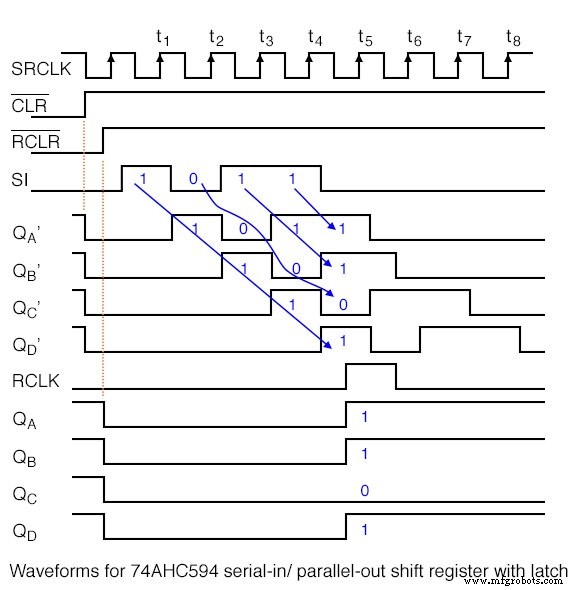

Sebaiknya menempatkan output dalam keadaan yang diketahui saat dihidupkan, khususnya, jika menggerakkan relai, motor, dll. Bentuk gelombang di bawah ini menggambarkan perpindahan dan penguncian data.

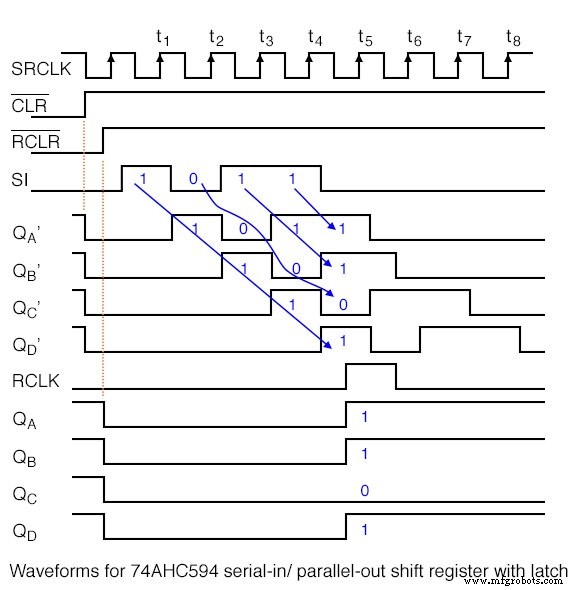

Bentuk gelombang di atas menunjukkan pergeseran 4-bit data ke dalam empat tahap pertama 74AHC594, kemudian transfer paralel ke register keluaran.

Faktanya, 74AHC594 adalah register geser 8-bit, dan akan membutuhkan 8-jam untuk menggeser data 8-bit, yang akan menjadi mode operasi normal.

Namun, 4-bit yang kami tampilkan menghemat ruang dan cukup menggambarkan operasi.

Kami menghapus register geser setengah jam sebelum t0 dengan SRCLR’=0 . SRCLR' harus dilepaskan kembali tinggi sebelum bergeser.

Tepat sebelum t0 register keluaran dikosongkan oleh RCLR’=0 . Itu juga dirilis ( RCLR’=1 ).

Data seri 1011 disajikan pada pin SI antara jam t0 dan t4 . Itu digeser oleh jam t1 t2 t3 t4 muncul pada tahap pergeseran internal QA ’ TB ’ TC ’ TD ' .

Data ini ada pada tahap ini antara t4 dan t5 . Setelah t5 data yang diinginkan (1011 ) tidak akan tersedia pada tahapan shifter internal ini.

Antara t4 dan t5 kami menerapkan RCLK yang positif mentransfer data 1011 untuk mendaftarkan keluaran QA TB TC TB .

Data ini akan dibekukan di sini karena lebih banyak data (0 s) bergeser selama SRCLK . berikutnya s (t5 ke t8 ). Tidak akan ada perubahan data di sini sampai RCLK lainnya diterapkan.

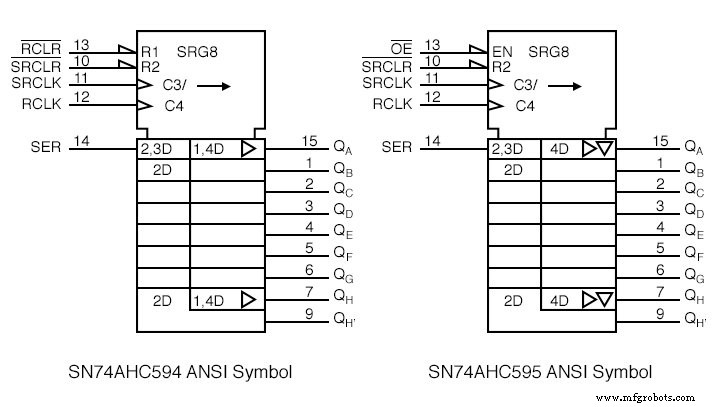

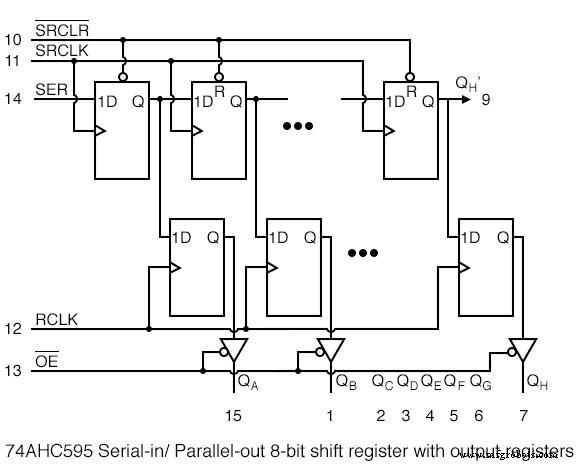

74AHC595 identik dengan '594 kecuali RCLR' digantikan oleh OE' mengaktifkan buffer tri-state pada output dari masing-masing dari delapan bit register output.

Meskipun register keluaran tidak dapat dikosongkan, keluaran mungkin terputus oleh OE’=1 .

Ini akan memungkinkan resistor pull-up atau pull-down eksternal memaksa relai, solenoid, atau driver katup ke status yang diketahui selama sistem dinyalakan.

Setelah sistem dinyalakan dan, katakanlah, mikroprosesor telah menggeser dan mengunci data ke '595, aktifkan output dapat ditegaskan (OE'=0 ) untuk menggerakkan relai, solenoida, dan katup dengan data yang valid, tetapi tidak sebelum waktu tersebut.

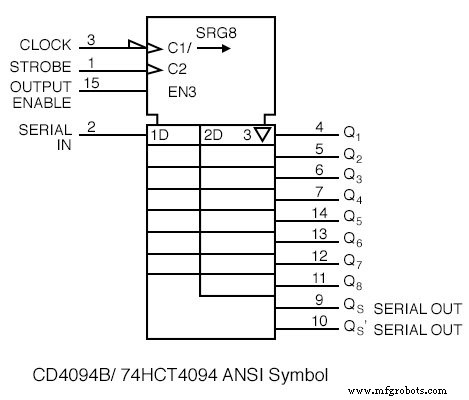

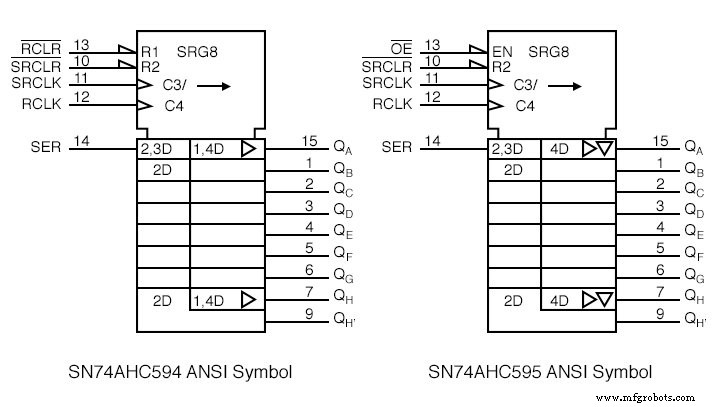

Di atas adalah simbol ANSI yang diusulkan untuk perangkat ini. C3 memasukkan data ke dalam input serial (SEReksternal) ) seperti yang ditunjukkan oleh 3 awalan 2,3D .

Panah setelah C3/ menunjukkan pergeseran ke kanan (bawah) dari register geser, 8-tahap di sebelah kiri simbol '595 di bawah bagian kontrol.

2 awalan 2,3D dan 2D menunjukkan bahwa tahapan ini dapat disetel ulang dengan R2 (SRCLR' eksternal' ).

1 awalan 1,4D pada ‘594 menunjukkan bahwa R1 (RCLR' eksternal' ) dapat mengatur ulang register keluaran, yang berada di sebelah kanan bagian register geser.

‘595 , yang memiliki EN di OE' external eksternal tidak dapat mengatur ulang register keluaran. Namun, ID mengaktifkan buffer output tristate (segitiga terbalik).

Segitiga siku-siku dari kedua ‘594 dan‘595 menunjukkan buffer internal. Keduanya ‘594 dan‘595 register keluaran di-clock oleh C4 seperti yang ditunjukkan oleh 4 dari 1,4D dan 4D masing-masing.

CD4094B adalah 3 hingga 15VDC alternatif register geser yang mampu mengunci perangkat 74AHC594 sebelumnya.

JAM , C 1, menggeser data di SERIAL IN seperti yang tersirat oleh 1 awalan 1D .

Ini juga merupakan jam dari register geser geser kanan (setengah kiri dari badan simbol) seperti yang ditunjukkan oleh /(panah kanan) dari C1 /(panah) di JAM masukan.

strobo , C2 adalah jam untuk register keluaran 8-bit di sebelah kanan badan simbol. 2 dari 2D menunjukkan bahwa C2 adalah jam untuk register keluaran.

Segitiga terbalik di kait keluaran menunjukkan bahwa keluaran tristat, diaktifkan oleh EN3 .

3 sebelum segitiga terbalik dan 3 dari EN3 sering dihilangkan, karena setiap aktifkan (EN ) dipahami untuk mengontrol output tristate. TS dan QS ' adalah output non-latched dari tahap register geser.

TS dapat diturunkan ke SERIAL IN dari perangkat berikutnya.

Aplikasi Praktis

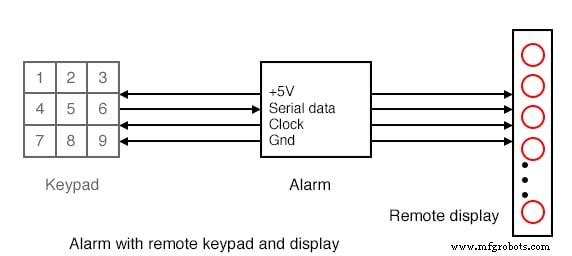

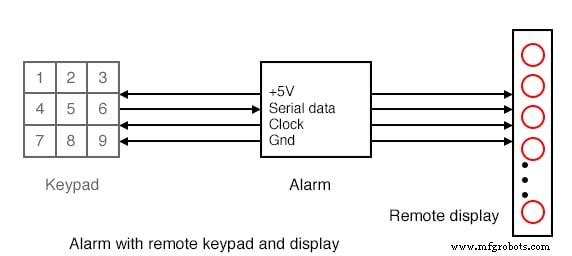

Aplikasi nyata dari register geser serial-in, paralel-out adalah untuk mengeluarkan data dari mikroprosesor ke indikator panel jarak jauh.

Atau, perangkat keluaran jarak jauh lain yang menerima data format serial.

Gambar “Alarm dengan papan tombol jarak jauh” diulang di sini dari bagian masuk-berseri, keluar-seri dengan tambahan tampilan jarak jauh.

Dengan demikian, kita dapat menampilkan, misalnya, status loop alarm yang terhubung ke kotak alarm utama.

Jika Alarm mendeteksi jendela yang terbuka, ia dapat mengirim data serial ke tampilan jarak jauh untuk memberi tahu kami.

Baik keypad dan layar kemungkinan akan berada dalam enklosur jarak jauh yang sama, terpisah dari kotak alarm utama. Namun, kita hanya akan melihat panel tampilan di bagian ini.

Jika tampilan berada di papan yang sama dengan Alarm, kami hanya dapat menjalankan delapan kabel ke delapan LED bersama dengan dua kabel untuk daya dan arde.

Kedelapan kabel ini jauh kurang diinginkan dalam jangka panjang ke panel jarak jauh. Dengan menggunakan register geser, kita hanya perlu menjalankan lima jam kabel, data serial, strobo, daya, dan ground.

Jika panel hanya beberapa inci dari papan utama, mungkin masih diinginkan untuk mengurangi jumlah kabel dalam kabel penghubung untuk meningkatkan keandalan.

Selain itu, terkadang kami menggunakan sebagian besar pin yang tersedia pada mikroprosesor dan perlu menggunakan teknik serial untuk memperluas jumlah output.

Beberapa perangkat output sirkuit terintegrasi, seperti konverter Digital ke Analog berisi register geser serial-in, paralel-out untuk menerima data dari mikroprosesor.

Teknik yang diilustrasikan di sini berlaku untuk bagian tersebut.

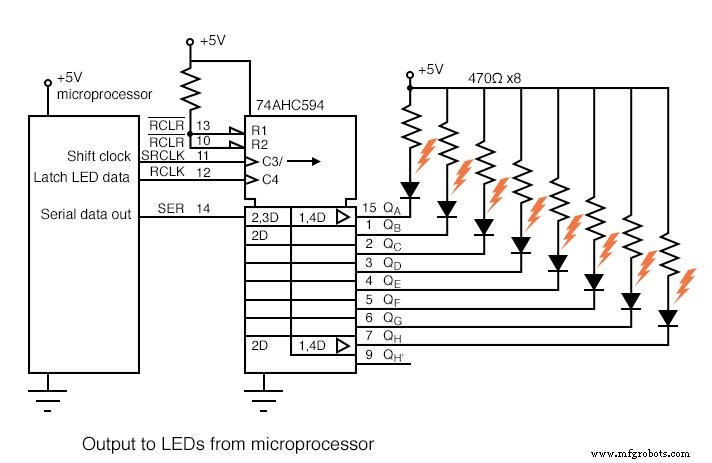

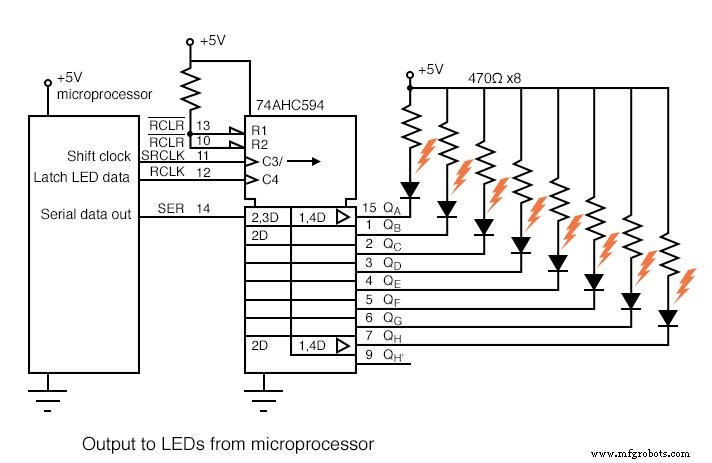

Kami telah memilih register geser seri-in, paralel-out 74AHC594 dengan register keluaran; meskipun, itu membutuhkan pin tambahan, RCLK , untuk memuat secara paralel data yang digeser ke pin output.

Pin ekstra ini mencegah keluaran berubah saat data masuk. Ini bukan masalah besar bagi LED. Tapi, akan menjadi masalah jika menggerakkan relay, valve, motor, dll.

Kode yang dieksekusi di dalam mikroprosesor akan dimulai dengan 8-bit data yang akan dikeluarkan. Satu bit akan dikeluarkan pada pin “Serial data out”, menggerakkan SER dari 74AHC594 jarak jauh.

Selanjutnya, mikroprosesor menghasilkan transisi rendah ke tinggi pada “Shift clock”, menggerakkan SRCLK dari '595 register geser.

Jam positif ini menggeser bit data pada SER dari "D" ke "Q" dari tahap register geser pertama.

Ini tidak berpengaruh pada QA LED saat ini karena register keluaran 8-bit internal antara register geser dan pin keluaran (QA ke TH ).

Akhirnya, "Shift clock" ditarik kembali rendah oleh mikroprosesor. Ini melengkapi perpindahan satu bit ke '595.

Prosedur di atas diulang tujuh kali lagi untuk menyelesaikan pemindahan 8-bit data dari mikroprosesor ke register geser paralel-in, paralel-out 74AHC594.

Untuk mentransfer 8-bit data dalam register geser '595 internal ke output memerlukan mikroprosesor menghasilkan transisi rendah ke tinggi pada RCLK , jam register keluaran.

Ini menerapkan data baru ke LED. RCLK perlu ditarik kembali rendah untuk mengantisipasi transfer data 8-bit berikutnya.

Data yang ada pada output '595 akan tetap ada sampai proses dalam dua paragraf di atas diulang untuk data 8-bit baru.

Secara khusus, data baru dapat dipindahkan ke register geser internal '595 tanpa mempengaruhi LED. LED hanya akan diperbarui dengan data baru dengan penerapan RCLK tepi naik.

Bagaimana jika kita perlu menggerakkan lebih dari delapan LED? Cukup cascade 74AHC594 SER lainnya sematkan ke QH ' dari shifter yang ada.

Paralel dengan SRCLK dan RCLK pin. Mikroprosesor perlu mentransfer data 16-bit dengan 16-jam sebelum menghasilkan RCLK memberi makan kedua perangkat.

Indikator LED diskrit, yang kami tampilkan, dapat berupa LED 7 segmen. Padahal, ada perangkat LSI (Large Scale Integration) yang mampu menggerakkan beberapa digit 7-segmen.

Perangkat ini menerima data dari mikroprosesor dalam format serial, menggerakkan lebih banyak segmen LED daripada yang dimilikinya dengan menggandakan LED.

LEMBAR KERJA TERKAIT:

- Lembar Kerja Daftar Shift