Teknologi Industri

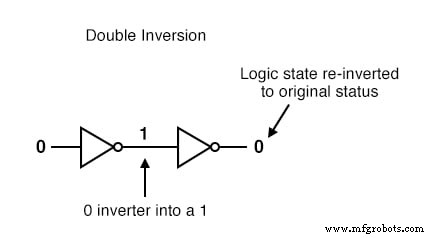

Jika kita menghubungkan dua gerbang inverter bersama-sama sehingga keluaran yang satu diumpankan ke masukan yang lain, kedua fungsi inversi akan “membatalkan” satu sama lain sehingga tidak akan ada inversi dari masukan ke keluaran akhir:

Meskipun ini mungkin tampak seperti hal yang sia-sia untuk dilakukan, itu memang memiliki aplikasi praktis. Ingatlah bahwa sirkuit gerbang adalah penguat sinyal , terlepas dari fungsi logika apa yang mungkin mereka lakukan.

Sumber sinyal yang lemah (yang tidak mampu mengalirkan atau menenggelamkan banyak arus ke beban) dapat dikuatkan melalui dua inverter seperti pasangan yang ditunjukkan pada ilustrasi sebelumnya. Tingkat logika tidak berubah, tetapi kemampuan sumber arus atau sinking penuh dari inverter final tersedia untuk mendorong resistensi beban jika diperlukan.

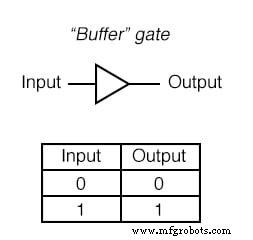

Untuk tujuan ini, gerbang logika khusus yang disebut buffer diproduksi untuk melakukan fungsi yang sama seperti dua inverter. Simbolnya hanyalah segitiga, tanpa “gelembung” pembalik pada terminal keluaran:

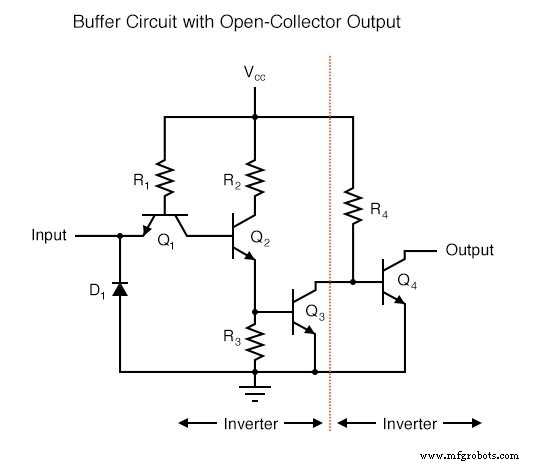

Sirkuit Buffer dengan Output Kolektor Terbuka

Diagram skematik internal untuk buffer kolektor terbuka tipikal tidak jauh berbeda dengan inverter sederhana:hanya satu tahap transistor emitor umum yang ditambahkan untuk membalikkan kembali sinyal output.

Analisis Masukan “Tinggi”

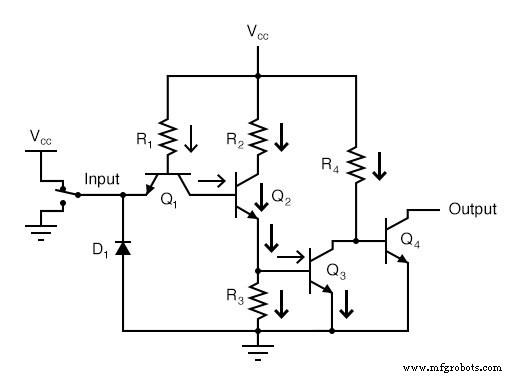

Mari kita analisis rangkaian ini untuk dua kondisi:level logika input "1" dan level logika input "0." Pertama, masukan “tinggi” (1):

Seperti sebelumnya dengan rangkaian inverter, input "tinggi" tidak menyebabkan konduksi melalui dioda kemudi kiri Q1 (persimpangan PN emitor-ke-basis). Semua arus R1 melewati basis transistor Q2, menjenuhkannya:

Memiliki Q2 jenuh menyebabkan Q3 menjadi jenuh juga, menghasilkan tegangan yang sangat sedikit turun antara basis dan emitor dari transistor keluaran akhir Q4. Dengan demikian, Q4 akan berada dalam mode cutoff, tidak mengalirkan arus.

Terminal keluaran akan mengambang (tidak terhubung ke ground atau Vcc), dan ini akan setara dengan status "tinggi" pada input gerbang TTL berikutnya yang dimasukkan ke dalam terminal ini. Jadi, input "tinggi" memberikan output "tinggi".

Analisis Input “Rendah”

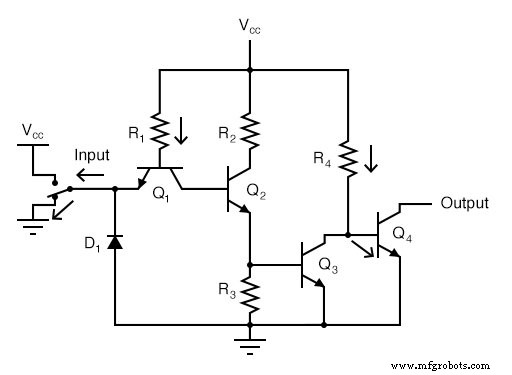

Dengan sinyal input "rendah" (terminal input diarde), analisisnya terlihat seperti ini:

Semua arus R1 sekarang dialihkan melalui sakelar input, sehingga menghilangkan arus basis melalui Q2. Ini memaksa transistor Q2 menjadi cutoff sehingga tidak ada arus basis yang melewati Q3 juga.

Dengan cutoff Q3 juga, Q4 akan jenuh oleh arus melalui resistor R4, sehingga menghubungkan terminal output ke ground, menjadikannya level logika "rendah". Jadi, input "rendah" memberikan output "rendah".

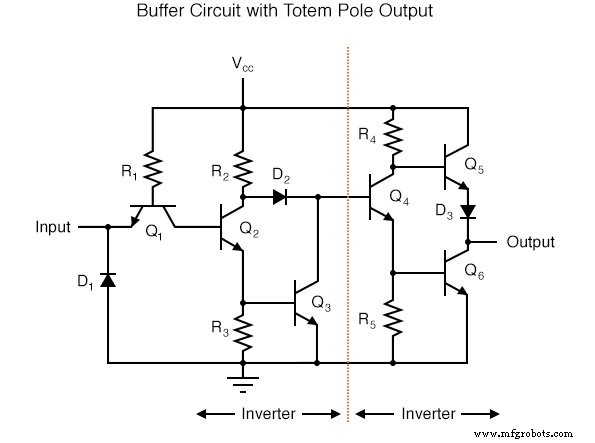

Diagram Skema dengan Transistor Output Tiang Totem

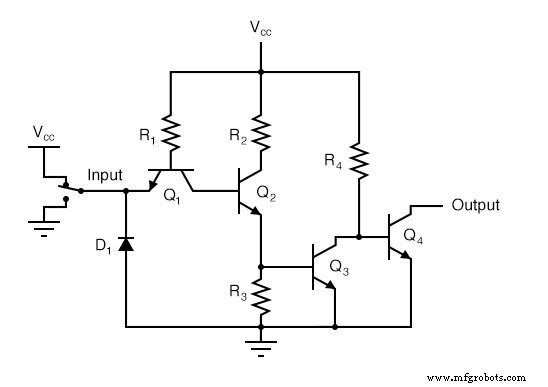

Diagram skema untuk rangkaian penyangga dengan transistor keluaran tiang totem sedikit lebih rumit, tetapi prinsip dasarnya, dan tentu saja tabel kebenarannya, sama dengan rangkaian kolektor terbuka:

TINJAUAN:

LEMBAR KERJA TERKAIT:

Teknologi Industri

Sistem konversi daya di EV mengikuti konfigurasi setengah jembatan. Artikel ini membahas desain setengah jembatan IGBT dari sisi tegangan tinggi (tahap keluaran) dari driver gerbang. EV adalah semua tentang kekuatan. Paket baterai besar menyalurkan daya ke berbagai sistem konversi daya melalui tega

Apa itu Solar Charge Controller? Jenis, Ukuran, dan Pemilihan Pengontrol Pengisian PWM &MPPT Pengendali muatan tenaga surya adalah bagian penting dari setiap instalasi tenaga surya. Mereka mengamankan komponen penyimpanan baterai Anda dan memastikannya berjalan dengan lancar dan andal selama masa pa

Terkadang sebuah rangkaian mungkin perlu mengisolasi gerbang logika rangkaian tanpa bergantung pada inverter. Di situlah buffer digital memberikan keuntungan. Tidak hanya menawarkan kemampuan isolasi, tetapi juga meningkatkan kekuatan sinyal sirkuit. Ini adalah pendekatan yang efektif karena memasti

Ada dua output aktif-rendah pada IC 74LS47 yang dapat menggerakkan LED anoda umum atau indikasi pijar. Sebagai input, dibutuhkan desimal berkode biner, sehingga mengubahnya menjadi pola yang menggerakkan tampilan tujuh segmen yang menampilkan angka nol hingga sembilan (dari Setiap digit angka dikode