Verilog

Flip-flop menangkap data pada inputnya di tepi positif atau negatif jam. Hal penting yang perlu diperhatikan adalah bahwa apapun yang terjadi pada data setelah tepi jam sampai tepi jam berikutnya tidak akan tercermin dalam output. Sebuah gerendel di sisi lain, tidak menangkap di tepi jam, sebaliknya output mengikuti input selama pin aktifkan dinyatakan.

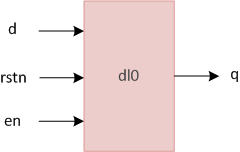

Dalam contoh ini, kita akan membuat gerendel yang memiliki tiga input dan satu output. Masukan d singkatan dari data yang dapat berupa 0 atau 1, pertama singkatan dari reset aktif-rendah dan en singkatan dari enable yang digunakan untuk membuat data input latching ke output. Reset menjadi aktif-rendah berarti bahwa elemen desain akan direset ketika input ini menjadi 0 atau dengan kata lain, reset aktif ketika nilainya rendah. Nilai keluaran q ditentukan oleh input d , id dan pertama .

module d_latch ( input d, // 1-bit input pin for data

input en, // 1-bit input pin for enabling the latch

input rstn, // 1-bit input pin for active-low reset

output reg q); // 1-bit output pin for data output

// This always block is "always" triggered whenever en/rstn/d changes

// If reset is asserted then output will be zero

// Else as long as enable is high, output q follows input d

always @ (en or rstn or d)

if (!rstn)

q <= 0;

else

if (en)

q <= d;

endmodule

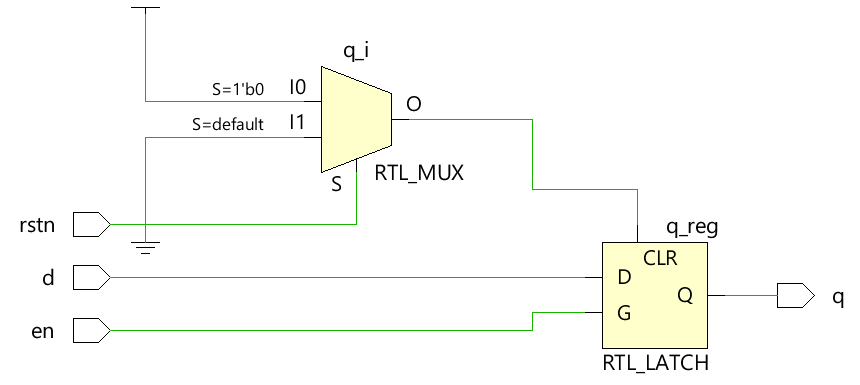

Perhatikan bahwa daftar sensitivitas terhadap always blok berisi semua sinyal yang diperlukan untuk memperbarui output. Blok ini akan dipicu setiap kali salah satu sinyal dalam daftar sensitivitas mengubah nilainya. Juga q akan mendapatkan nilai d hanya jika en tinggi, dan karenanya adalah positif kait.

module tb_latch;

// Declare variables that can be used to drive values to the design

reg d;

reg en;

reg rstn;

reg [2:0] delay;

reg [1:0] delay2;

integer i;

// Instantiate design and connect design ports with TB signals

d_latch dl0 ( .d (d),

.en (en),

.rstn (rstn),

.q (q));

// This initial block forms the stimulus to test the design

initial begin

$monitor ("[%0t] en=%0b d=%0b q=%0b", $time, en, d, q);

// 1. Initialize testbench variables

d <= 0;

en <= 0;

rstn <= 0;

// 2. Release reset

#10 rstn <= 1;

// 3. Randomly change d and enable

for (i = 0; i < 5; i=i+1) begin

delay = $random;

delay2 = $random;

#(delay2) en <= ~en;

#(delay) d <= i;

end

end

endmodule

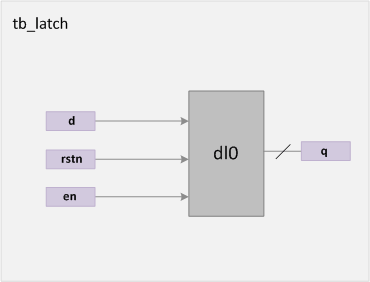

Untuk membuat testbench kami menegaskan dan menonaktifkan sinyal dengan cara yang lebih acak, kami telah mendeklarasikan reg variabel yang disebut penundaan berukuran 3 bit sehingga dapat mengambil nilai apapun dari 0 sampai 7. Kemudian delay variabel digunakan untuk menunda penugasan d dan id untuk mendapatkan pola yang berbeda di setiap loop.

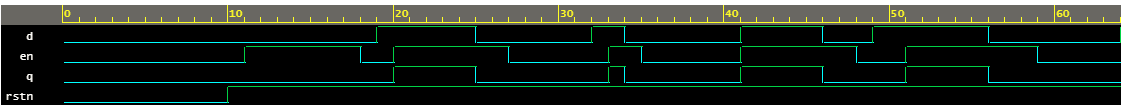

ncsim> run [0] en=0 d=0 q=0 [11] en=1 d=0 q=0 [18] en=0 d=0 q=0 [19] en=0 d=1 q=0 [20] en=1 d=1 q=1 [25] en=1 d=0 q=0 [27] en=0 d=0 q=0 [32] en=0 d=1 q=0 [33] en=1 d=1 q=1 [34] en=1 d=0 q=0 ncsim: *W,RNQUIE: Simulation is complete.

Klik pada gambar untuk membuatnya lebih besar.

Verilog

Untuk mengatasi tantangan dalam menciptakan tegangan bias DC yang diperlukan untuk sinyal input penguat tanpa menggunakan baterai secara seri dengan sumber sinyal AC, kami menggunakan pembagi tegangan yang terhubung ke sumber daya DC. Untuk membuat ini bekerja bersama dengan sinyal input AC, kami me

Port adalah seperangkat sinyal yang bertindak sebagai input dan output ke modul tertentu dan merupakan cara utama untuk berkomunikasi dengannya. Pikirkan modul sebagai chip buatan yang ditempatkan pada PCB dan menjadi sangat jelas bahwa satu-satunya cara untuk berkomunikasi dengan chip adalah melalu

Primitif Verilog standar seperti nand dan not mungkin tidak selalu mudah atau cukup untuk mewakili logika yang kompleks. Elemen primitif baru yang disebut UDP atau primitif yang ditentukan pengguna dapat didefinisikan untuk memodelkan logika kombinasional atau sekuensial. Semua UDP memiliki tepat s

Apa itu mux atau multiplexer? Multiplexer atau mux singkatnya, adalah elemen digital yang mentransfer data dari salah satu input N ke output berdasarkan sinyal pilih. Kasus yang ditunjukkan di bawah ini adalah ketika N sama dengan 4. Misalnya, multiplexer 4 bit akan memiliki N input masing-masing 4