Teknologi Industri

Shift register serial-in, serial-out menunda data satu jam waktu untuk setiap tahap.

Mereka akan menyimpan sedikit data untuk setiap register. Shift register serial-in, serial-out mungkin memiliki panjang satu hingga 64 bit, lebih lama jika register atau paket di-cascade.

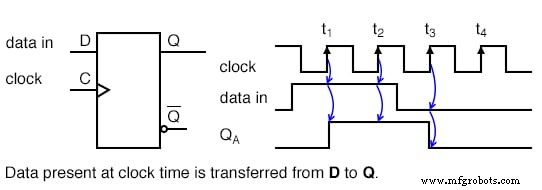

Di bawah ini adalah register geser satu tahap yang menerima data yang tidak disinkronkan dengan jam register.

“Data masuk” di D pin jenis D FF (Flip-Flop) tidak mengubah level saat jam berubah dari rendah ke tinggi.

Kami mungkin ingin menyinkronkan data ke jam seluruh sistem di papan sirkuit untuk meningkatkan keandalan sirkuit logika digital.

Poin yang jelas (dibandingkan dengan gambar di bawah) yang diilustrasikan di atas adalah bahwa "data masuk" apa pun yang ada di D pin bertipe D FF ditransfer dari D ke output Q pada waktu clock.

Karena register geser contoh kami menggunakan elemen penyimpanan sensitif tepi positif, output Q mengikuti D masukan ketika jam bertransisi dari rendah ke tinggi seperti yang ditunjukkan oleh panah atas pada diagram di atas.

Tidak diragukan lagi level logika apa yang ada pada waktu clock karena data stabil baik sebelum dan sesudah tepi clock.

Ini jarang terjadi pada register geser multi-tahap. Tapi, ini adalah contoh yang mudah untuk memulai. Kami hanya peduli dengan tepi jam positif, rendah ke tinggi.

Tepi jatuh dapat diabaikan. Sangat mudah untuk melihat Q ikuti D pada waktu jam di atas.

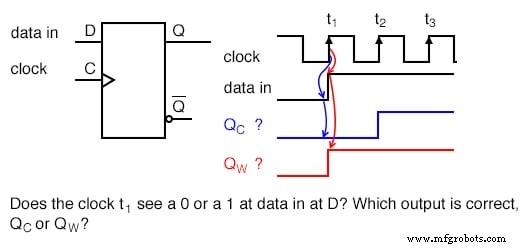

Bandingkan ini dengan diagram di bawah ini di mana "data masuk" tampak berubah dengan tepi jam positif.

Karena "data masuk" tampaknya berubah pada waktu jam t1 di atas, apa jenis D FF lihat pada waktu jam?

Jawaban singkat yang terlalu disederhanakan adalah ia melihat data yang ada di D sebelum jam.

Itulah yang ditransfer ke Q pada waktu jam t1 . Bentuk gelombang yang benar adalah QC . Di t1 Q menjadi nol jika belum nol.

D mendaftar tidak melihat satu sampai waktu t2 , saat Q menjadi tinggi.

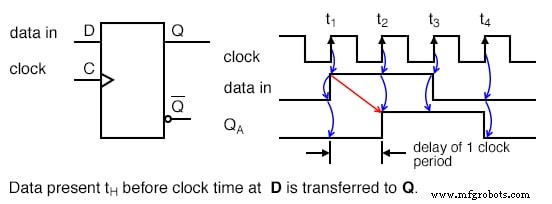

Karena data di atas, hadir pada H clock ke Q pada waktu jam, dan Q tidak dapat berubah hingga waktu jam berikutnya, D FF menunda data dengan satu periode jam, asalkan data sudah disinkronkan ke jam. TA bentuk gelombang sama dengan "data masuk" dengan penundaan periode satu jam.

Tampilan yang lebih detail apa input dari tipe D Flip-Flop melihat pada waktu jam berikut.

Lihat gambar di bawah ini. Karena “data masuk” tampak berubah pada waktu jam (di atas), kami memerlukan informasi lebih lanjut untuk menentukan apa yang D FF melihat.

Jika “data masuk” berasal dari tahap register geser lain, jenis lain yang sama D FF, kita dapat menarik beberapa kesimpulan berdasarkan lembar data informasi.

Produsen logika digital menyediakan informasi tentang bagian-bagiannya dalam lembar data, yang sebelumnya hanya tersedia dalam kumpulan yang disebut buku data .

Buku data masih tersedia; meskipun, situs web produsen adalah sumber modern.

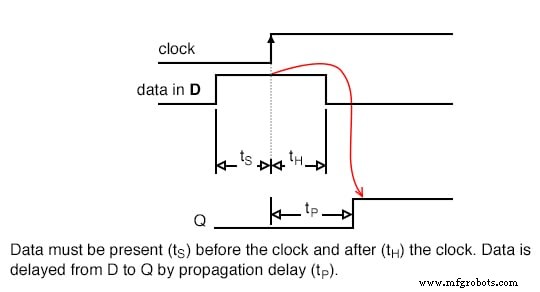

Data berikut diekstraksi dari lembar data CD4006b untuk operasi pada 5VDC , yang berfungsi sebagai contoh untuk menggambarkan waktu. [*]

tS adalah waktu penyiapan , data waktu harus ada sebelum waktu jam. Dalam hal ini, data harus ada di D 100 detik sebelum jam.

Selanjutnya, data harus disimpan untuk waktu penahanan tH =60ns setelah waktu jam. Kedua kondisi ini harus dipenuhi untuk data clock yang andal dari D untuk T dari Flip-Flop.

Tidak ada masalah untuk memenuhi waktu penyiapan 60ns sebagai data pada H telah ada untuk seluruh periode jam sebelumnya jika itu berasal dari tahap register geser lain.

Misalnya, pada frekuensi clock 1 Mhz, periode clock adalah 1000 s, banyak waktu.

Data sebenarnya akan ada selama 1000 detik sebelum jam, yang jauh lebih besar dari tS minimum yang diperlukan dari 60n.

Waktu penahanan tH =60ns terpenuhi karena D terhubung ke Q tahap lain tidak dapat berubah lebih cepat dari penundaan propagasi tahap sebelumnya tP =200n.

Waktu tunggu terpenuhi selama penundaan propagasi D . sebelumnya FF lebih besar dari waktu penahanan.

Data pada H didorong oleh tahap lain Q tidak akan berubah lebih cepat dari 200ns untuk CD4006b.

Untuk meringkas, keluarkan Q mengikuti input D hampir sepanjang waktu jika Flip-Flop di-cascade ke dalam register geser multi-tahap.

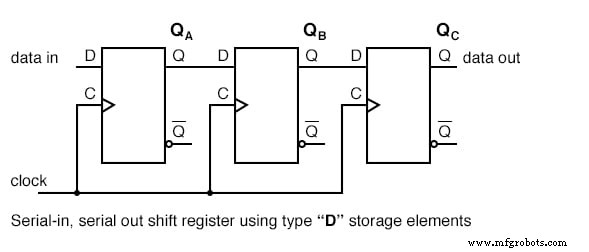

Tiga jenis D Flip-Flop mengalir dari Q ke D dan jam diparalelkan untuk membentuk register geser tiga tahap di atas.

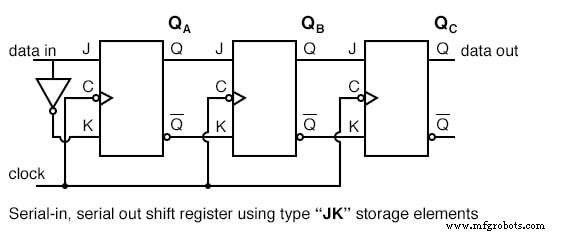

Ketik JK Flip Flops mengalirkan Q ke J, Q’ ke K dengan jam paralel untuk menghasilkan bentuk alternatif dari register geser di atas.

Shift register serial-in/serial-out memiliki input clock, input data, dan output data dari tahap terakhir.

Secara umum, output tahap lainnya tidak tersedia. Jika tidak, itu akan menjadi register geser serial-in, paralel-out.

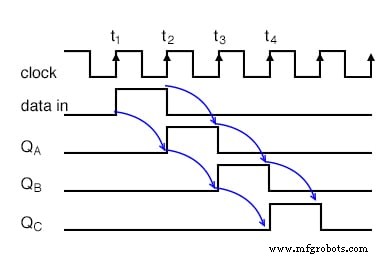

Bentuk gelombang di bawah ini berlaku untuk salah satu dari dua versi sebelumnya dari register geser serial-in, serial-out.

Tiga pasang panah menunjukkan bahwa register geser tiga tahap menyimpan sementara 3-bit data dan menundanya selama tiga periode jam dari input ke output.

Pada waktu jam t1 "data masuk" 0 clock dari D untuk T dari ketiga tahap tersebut. Khususnya, D tahap A melihat logika 0 , yang diatur ke QA dimana tetap sampai waktu t2 .

Pada waktu jam t2 "data masuk" 1 clock dari D ke TA . Pada tahap B dan C , a 0 , diumpankan dari tahapan sebelumnya di-clock ke QB dan TC .

Pada waktu jam t3 "data masuk" 0 clock dari D ke TA . TJ menjadi rendah dan tetap rendah untuk jam yang tersisa karena "data masuk" menjadi 0 . TB menjadi tinggi pada t3 karena 1 dari tahap sebelumnya. TC masih rendah setelah t3 karena rendah dari tahap sebelumnya.

TC akhirnya menjadi tinggi pada jam t4 karena diumpankan tinggi ke D dari tahap sebelumnya QB . Semua tahapan sebelumnya memiliki 0 s bergeser ke mereka. Dan, setelah jam berikutnya pulsa di t5 , semua logika 1 s akan digeser, digantikan oleh 0 s

Kami akan melihat lebih dekat pada bagian berikut yang tersedia sebagai sirkuit terintegrasi, milik Texas Instruments.

Untuk lembar data perangkat lengkap, ikuti tautannya.

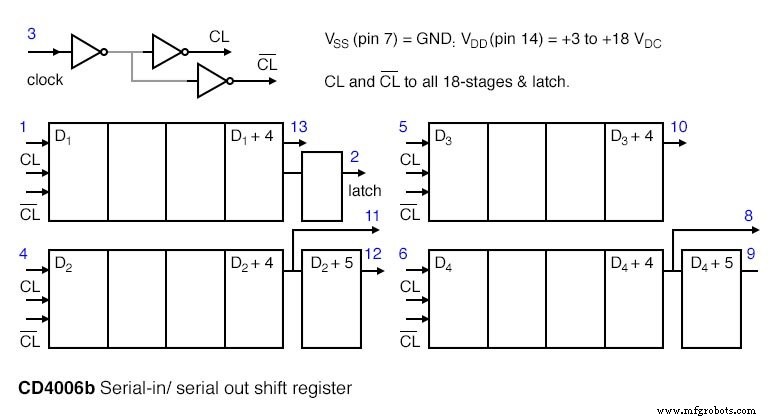

Shift register serial-in/ serial-out berikut adalah seri 4000 CMOS (Pelengkap Metal Oxide Semiconductor) bagian keluarga.

Dengan demikian, Mereka akan menerima VDD , catu daya positif dari 3-Volt hingga 15-Volt. VSS pin diarde.

Frekuensi maksimum jam shift, yang bervariasi dengan VDD , adalah beberapa megahertz.

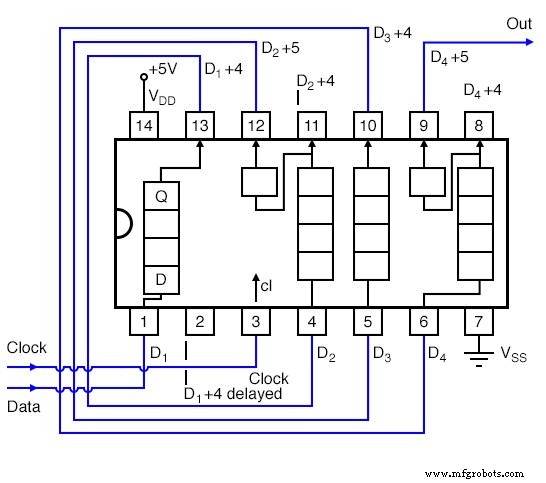

CD4006b 18-bit terdiri dari dua tahap 4-bit dan dua tahap lagi 5-bit dengan tap keluaran pada 4-bit.

Dengan demikian, tahapan 5 bit dapat digunakan sebagai register geser 4 bit.

Untuk mendapatkan register geser 18-bit penuh, output dari satu register geser harus mengalir ke input yang lain dan seterusnya sampai semua tahapan membuat register geser tunggal seperti yang ditunjukkan di bawah ini.

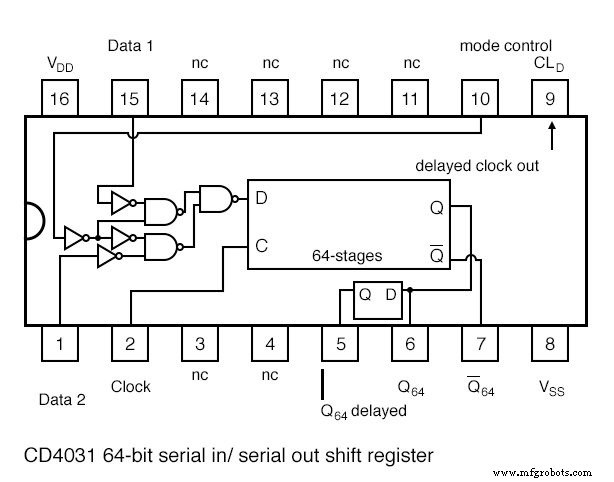

Register geser CD4031 64-bit serial-in/ serial-out ditunjukkan di bawah ini.

Sejumlah pin tidak terhubung (nc). Baik Q dan Q’ tersedia dari tahap ke-64, sebenarnya Q64 dan Q’64 .

Ada juga Q64 "tertunda" dari setengah tahap yang tertunda setengah siklus jam. Fitur utama adalah pemilih data yang ada di input data ke register geser.

“Mode control” memilih antara dua input:data 1 dan data 2. Jika “mode control” tinggi, data akan dipilih dari “data 2” untuk input ke register geser.

Dalam kasus "kontrol mode" menjadi logika rendah, "data 1" dipilih. Contohnya ditunjukkan pada dua gambar di bawah ini.

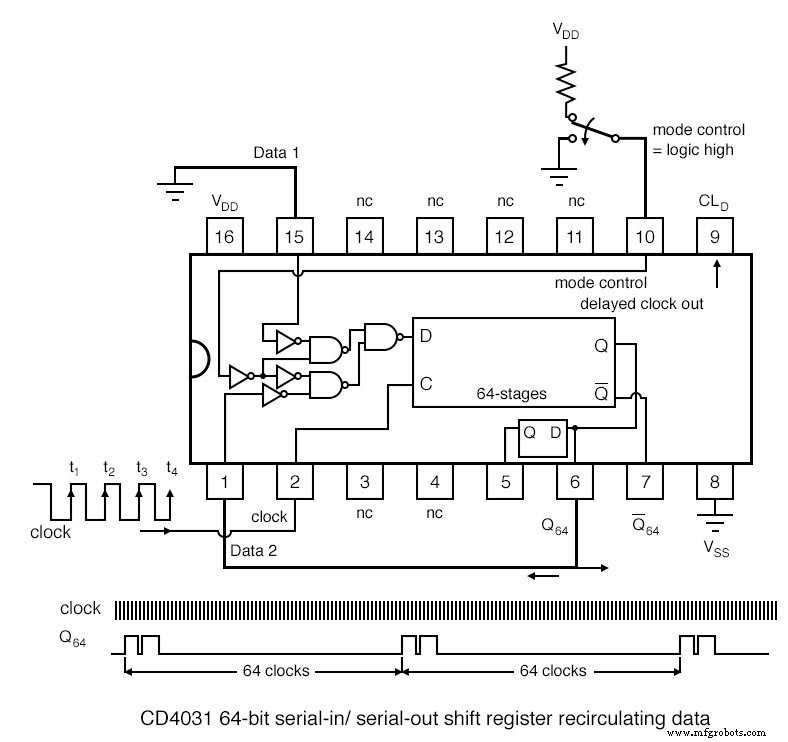

“Data 2” di atas disambungkan ke Q64 keluaran dari register geser. Dengan "kontrol mode" tinggi, Q64 output dialihkan kembali ke input data shifter D.

Data akan disirkulasikan dari keluaran ke masukan. Data akan berulang setiap 64 pulsa clock seperti yang ditunjukkan di atas.

Pertanyaan yang muncul adalah bagaimana pola data ini bisa masuk ke register geser?

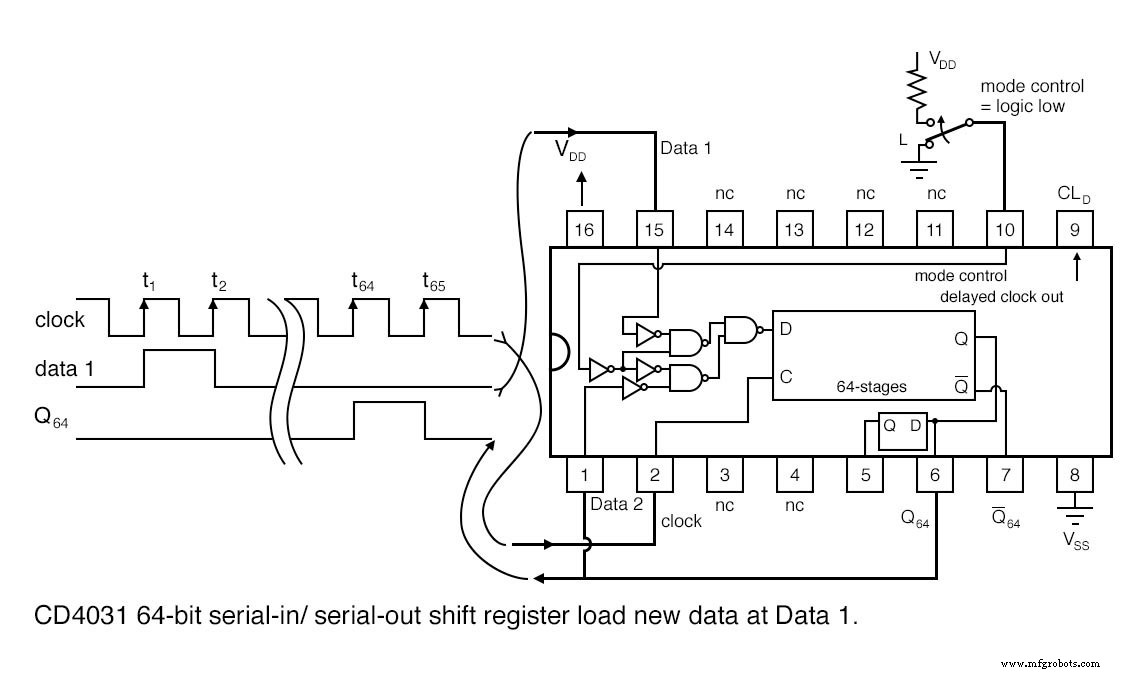

Dengan “mode control” rendah, CD4031 “data 1” dipilih untuk input ke shifter.

Outputnya, Q64 , tidak disirkulasi ulang karena gerbang pemilih data bawah dinonaktifkan .

Dengan menonaktifkan yang kami maksudkan bahwa logika "pilih mode" rendah terbalik dua kali ke rendah di gerbang NAND bawah mencegahnya untuk melewatkan sinyal apa pun pada pin bawah (data 2) ke output gerbang.

Dengan demikian, ini dinonaktifkan.

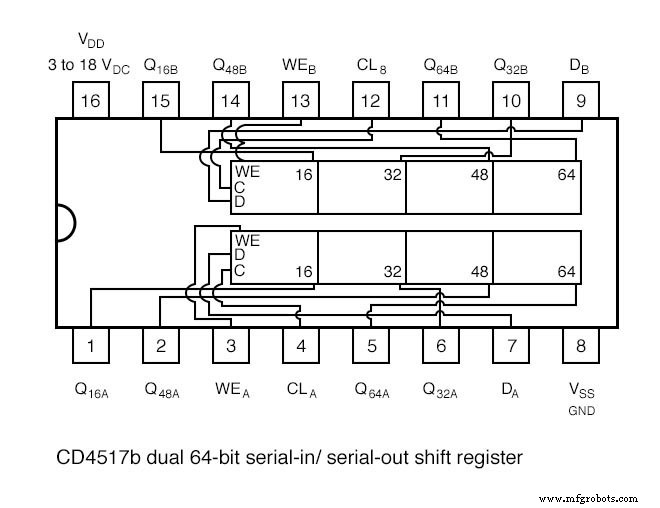

Sebuah register geser 64-bit ganda CD4517b ditunjukkan di atas. Perhatikan tap pada tahap 16, 32, dan 48.

Itu berarti bahwa register geser dengan panjang tersebut dapat dikonfigurasi dari salah satu shifter 64-bit.

Tentu saja, shifter 64-bit dapat di-cascade untuk menghasilkan register geser 80-bit, 96-bit, 112-bit, atau 128-bit.

Jam CLA dan CLB perlu diparalelkan saat mengalirkan dua shifter. KAMIB dan KAMIB di-ground untuk operasi pemindahan gigi normal.

Input data ke register geser A dan B adalah DA dan DB masing-masing.

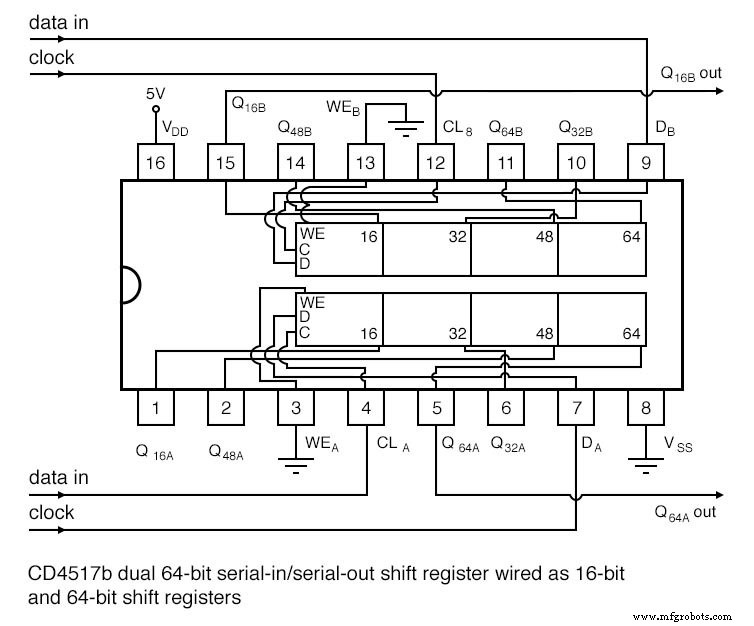

Misalkan kita memerlukan register geser 16-bit.

Bisakah ini dikonfigurasi dengan CD4517b? Bagaimana dengan register 64 shift dari bagian yang sama?

Di atas kami menunjukkan kabel CD4517b sebagai register geser 16-bit untuk bagian B.

Jam untuk bagian B adalah CLB . Data dicatat di CLB . Dan data yang tertunda 16 jam diambil dari Q16B . KAMIB , pengaktifan penulisan, di-ground.

Di atas kami juga menunjukkan kabel CD4517b yang sama sebagai register geser 64-bit untuk bagian independen A.

Jam untuk bagian A adalah CLA . Data masuk di CLA . Data tertunda oleh pulsa 64-clock diambil dari Q64A . KAMIA , pengaktifan tulis untuk bagian A, di-ground.

LEMBAR KERJA TERKAIT:

Teknologi Industri

Kami telah menggunakan analitik untuk meningkatkan proses produksi kami di pabrik Bosch selama bertahun-tahun. Jadi, apa yang baru dalam analitik di bidang manufaktur, dan apa langkah selanjutnya? Metodologi kami untuk analisis persyaratan membuat semua perbedaan Ada berbagai cara untuk menjalanka

Komponen dan persediaan Arduino Nano R3 × 1 Texas Instruments Shift Register- Serial to Parallel 74HC595 × 4 Ukuran Penuh Papan Tempat Memotong Roti Tanpa Solder × 1 LED (generik) Tergantung pada preferensi Anda. × 1 Resistor 100 ohm Tergantung pada LED

Arduino Serial:Komunikasi Serial oleh Arduino Latar Belakang Komunikasi Serial: Ketika mikrokontroler atau mikroprosesor perlu berkomunikasi dengan dunia luar, maka mereka menyediakan data dalam bentuk paket 8 bit, jadi jika satu sistem perlu berkomunikasi dengan yang lain, maka total 8 kabel kabel

easymon adalah solusi pemantauan jarak jauh yang menghadirkan kemudahan penggunaan dunia ponsel cerdas ke domain pengontrol mesin. Hanya perlu menginstal ekstensi fungsi PLCnext dari toko PLCnext dan aplikasi smartphone yang sesuai dari iOS atau Google Play Store. Setelah konfigurasi yang cepat dan