Teknologi Industri

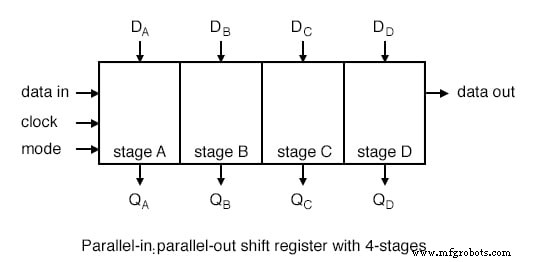

Tujuan dari register geser paralel-in/parallel-out adalah untuk mengambil data paralel, menggesernya, kemudian mengeluarkannya seperti gambar di bawah ini.

Register geser universal adalah perangkat melakukan segalanya selain fungsi paralel-in/parallel-out.

Di atas kami menerapkan empat bit data ke register geser paralel-in/parallel-out di DA DB DC DD . Kontrol mode, yang mungkin berupa beberapa input, mengontrol pemuatan paralel vs pemindahan.

Kontrol mode juga dapat mengontrol arah perpindahan di beberapa perangkat nyata. Data akan digeser satu posisi bit untuk setiap pulsa clock.

Data yang digeser tersedia di output QA TB TC TB . "Data masuk" dan "data keluar" disediakan untuk beberapa tahap.

Padahal, di atas, kita hanya bisa mengalirkan data untuk pergeseran ke kanan. Kami dapat mengakomodasi cascading data shift kiri dengan menambahkan sepasang sinyal penunjuk kiri, “data masuk” dan “data keluar”, di atas.

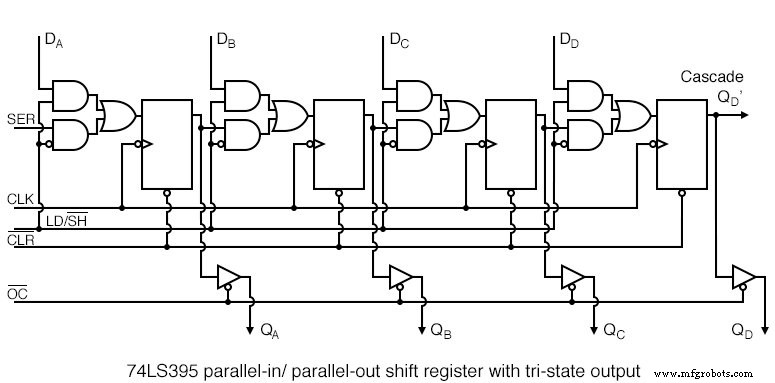

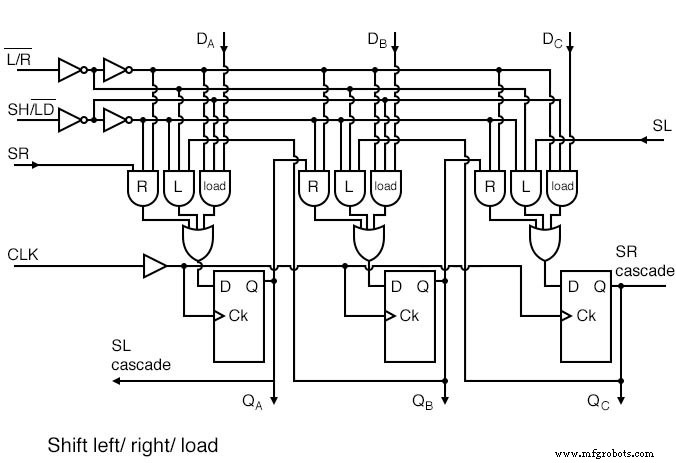

Detail internal dari register geser paralel-in/parallel-out pemindah kanan ditunjukkan di bawah ini.

Buffer tri-state tidak sepenuhnya diperlukan untuk register geser paralel-in/parallel-out, tetapi merupakan bagian dari perangkat dunia nyata yang ditunjukkan di bawah ini.

74LS395 sangat cocok dengan konsep kami tentang register geser paralel-masuk/paralel-keluar hipotetis kanan sehingga kami menggunakan versi detail lembar data di atas yang terlalu disederhanakan.

Lihat tautan ke lembar data lengkap lebih detail, nanti di bab ini.

LD/SH’ mengontrol multiplexer DAN-ATAU pada input data ke FF. Jika LD/SH’=1 , empat gerbang AND atas diaktifkan memungkinkan penerapan input paralel DA DB DC DD ke empat input data FF.

Perhatikan gelembung inverter pada input clock dari empat FF. Ini menunjukkan bahwa 74LS395 mencatat data pada clock negatif, yang merupakan transisi tinggi ke rendah.

Empat bit data akan di-clock secara paralel dari DA DB DC DD ke TA TB TC TB pada jam negatif berikutnya. Di "bagian nyata" ini, OC' harus rendah jika data harus tersedia di pin keluaran aktual, bukan hanya di FF internal.

Data yang dimuat sebelumnya dapat digeser ke kanan satu posisi bit jika LD/SH’=0 untuk tepi jam negatif berikutnya.

Empat jam akan menggeser data sepenuhnya dari register geser 4-bit kami. Data akan hilang kecuali perangkat kita diturunkan dari QD ' ke SER perangkat lain.

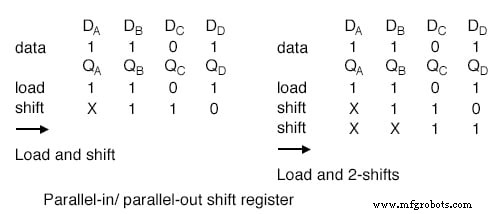

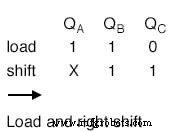

Di atas, pola data disajikan ke input DA DB DC DD . Pola dimuat ke QA TB TC TB . Kemudian digeser sedikit ke kanan.

Data yang masuk ditunjukkan dengan X , artinya kita tidak tahu apa itu. Jika masukan (SER ) di-ground, misalnya, kita akan mengetahui data apa (0 ) digeser masuk.

Juga ditampilkan, adalah pergeseran ke kanan dengan dua posisi, membutuhkan dua jam.

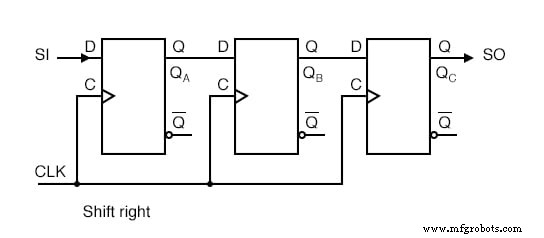

Gambar di atas berfungsi sebagai referensi untuk perangkat keras yang terlibat dalam pemindahan data ke kanan.

Terlalu sederhana untuk mempermasalahkan angka ini, kecuali untuk perbandingan dengan angka yang lebih kompleks untuk diikuti.

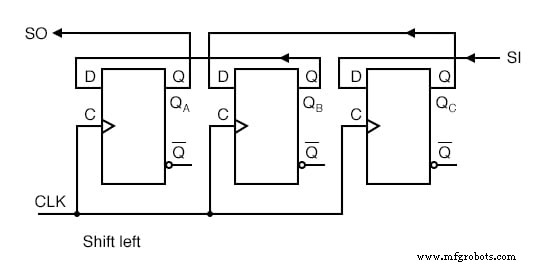

Pergeseran data ke kanan disediakan di atas untuk referensi ke penggeser kanan sebelumnya.

Jika kita perlu bergeser ke kiri, FF perlu dipasang ulang. Bandingkan dengan shifter kanan sebelumnya. Juga, SI dan BENAR telah dibalik. SI bergeser ke QC . TC bergeser ke QB . TB bergeser ke QA . TA meninggalkan SO koneksi, di mana ia bisa mengalir ke shifter lain SI . Urutan shift kiri ini mundur dari urutan shift kanan.

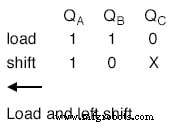

Di atas kita menggeser pola data yang sama ke kiri satu bit.

Ada satu masalah dengan gambar "geser ke kiri" di atas. Tidak ada pasar untuk itu. Tidak ada yang memproduksi bagian shift-kiri.

Sebuah "perangkat nyata" yang menggeser satu arah dapat ditransfer secara eksternal untuk menggeser ke arah lain. Atau, haruskah kita mengatakan tidak ada kiri atau kanan dalam konteks perangkat yang hanya bergeser ke satu arah.

Namun, ada pasar untuk perangkat yang akan bergeser ke kiri atau kanan atas perintah garis kontrol. Tentu saja, kiri dan kanan berlaku dalam konteks itu.

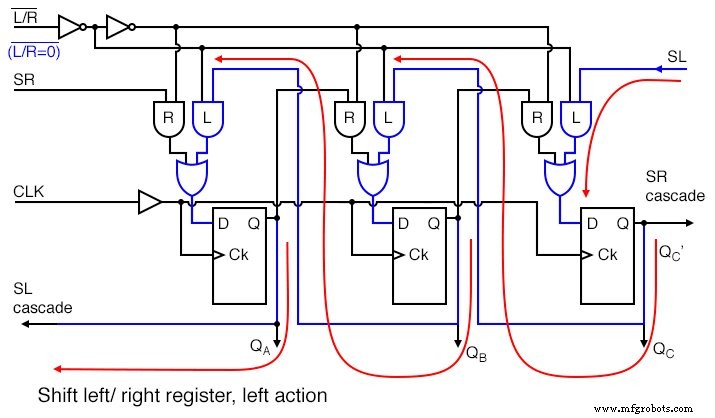

Apa yang kita miliki di atas adalah register geser hipotetis yang mampu menggeser kedua arah di bawah kendali L’/R .

Ini disetel dengan L’/R=1 untuk menggeser arah normal, benar. L’/R=1 mengaktifkan multiplexer AND gerbang berlabel R .

Hal ini memungkinkan data untuk mengikuti jalur yang diilustrasikan oleh panah, ketika sebuah jam diterapkan. Jalur koneksi sama dengan gambar "terlalu sederhana" "geser ke kanan" di atas.

Pergeseran data pada SR , ke TA , ke TB , ke TC , di mana ia pergi pada SR cascade . Pin ini dapat mendorong SR perangkat lain di sebelah kanan.

Bagaimana jika kita mengubah L’/R ke L’/R=0 ?

Dengan L’/R=0 , gerbang AND multiplekser berlabel L diaktifkan, menghasilkan jalur, yang ditunjukkan oleh panah, sama seperti gambar “geser ke kiri” di atas.

Pergeseran data di SL , ke TC , ke TB , ke TA , di mana ia pergi pada SL cascade . Pin ini dapat mendorong SL perangkat lain di sebelah kiri.

Keutamaan utama dari dua gambar di atas yang menggambarkan "register geser kiri/kanan" adalah kesederhanaan.

Pengoperasian kontrol kiri kanan L’/R=0 mudah diikuti. Bagian komersial membutuhkan pemuatan data paralel yang tersirat oleh judul bagian. Ini tampak pada gambar di bawah.

Sekarang kita dapat menggeser kiri dan kanan melalui L’/R , mari kita tambahkan SH/LD' , shift/ load, dan gerbang AND berlabel “load” untuk menyediakan pemuatan paralel data dari input DA DB DC .

Saat SH/LD’=0 , Gerbang AND R dan L dinonaktifkan, gerbang AND “memuat” diaktifkan untuk meneruskan data DA DB DC ke input data FF. jam berikutnya CLK akan mencatat data ke QA TB TC .

Selama data yang sama ada, itu akan dimuat ulang pada jam berikutnya. Namun, data yang ada hanya untuk satu jam akan hilang dari output saat tidak ada lagi di input data.

Salah satu solusinya adalah dengan memuat data pada satu jam, kemudian dilanjutkan dengan menggeser pada empat jam berikutnya. Masalah ini diatasi di 74ALS299 dengan penambahan gerbang AND lain ke multiplexer.

Jika SH/LD' diubah menjadi SH/LD’=1 , gerbang AND berlabel “beban” dinonaktifkan, memungkinkan kontrol kiri/kanan L’/R untuk mengatur arah shift pada L atau R DAN gerbang. Pergeseran seperti pada gambar sebelumnya.

Satu-satunya hal yang diperlukan untuk menghasilkan perangkat terintegrasi yang layak adalah menambahkan gerbang AND keempat ke multiplexer seperti yang disinggung untuk 74ALS299.

Ini ditunjukkan di bagian berikutnya untuk bagian itu.

Mari kita lihat lebih dekat register geser Serial-in/parallel-out yang tersedia sebagai sirkuit terintegrasi, milik Texas Instruments.

Untuk lembar data perangkat lengkap, ikuti tautannya.

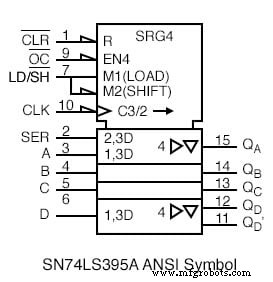

register geser 4-bit paralel-in/parallel-out SN74LS395A

SN74ALS299 register geser universal 8-bit paralel-in/ paralel-out

Kami telah melihat detail internal SN74LS395A, lihat gambar sebelumnya di atas, register geser paralel-in/parallel-out 74LS395 dengan output tri-status.

Tepat di atas adalah simbol ANSI untuk 74LS395.

Mengapa hanya 4-bit, seperti yang ditunjukkan oleh SRG4 di atas? Memiliki input paralel dan output paralel, selain pin kontrol dan daya, tidak memungkinkan bit I/O (Input/Output) lagi dalam DIP 16-pin (Paket Sebaris Ganda).

B menunjukkan bahwa tahapan register geser diatur ulang dengan memasukkan CLR’ (setengah panah pembalik rendah aktif pada input) dari bagian kontrol di bagian atas simbol. OC' , saat rendah, (panah balik lagi) akan mengaktifkan (EN4 ) empat buffer keluaran tristate (QA TB TC TB ) di bagian data.

Muat/geser’ (LD/SH’ ) di pin (7) sesuai dengan internal M1 (memuat) dan M2 (menggeser). Cari awalan 1 dan 2 di sisa simbol untuk memastikan apa yang dikendalikan oleh ini.

Jam sensitif tepi negatif (ditunjukkan dengan panah terbalik di pin-10) C3/2 memiliki dua fungsi.

Pertama, 3 dari C3/2 memengaruhi input apa pun yang memiliki awalan 3 , ucapkan 2,3D atau 1,3D di bagian data.

Ini akan menjadi beban paralel di A, B, C, D dikaitkan dengan M1 dan C3 untuk 1,3D . Kedua, 2 dari C3/2 -panah kanan menunjukkan pencatatan jam kerja data di mana pun 2 muncul di awalan (2,3D di pin-2).

Jadi kami memiliki pencatatan jam kerja data di SER menjadi QA dengan mode 2 . Panah kanan setelah C3/2 memperhitungkan pergeseran pada tahap register geser internal QA TB TC TB .

Segitiga menunjuk kanan menunjukkan buffering; segitiga terbalik menunjukkan tri-state, dikendalikan oleh EN4 .

Perhatikan, semua 4 s dalam simbol yang terkait dengan EN sering dihilangkan. Tahapan QB TC dipahami memiliki atribut yang sama dengan QD . TD ' mengalir ke SER paket berikutnya ke kanan.

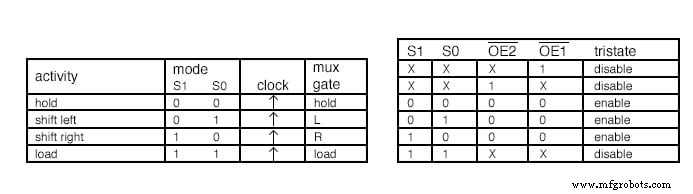

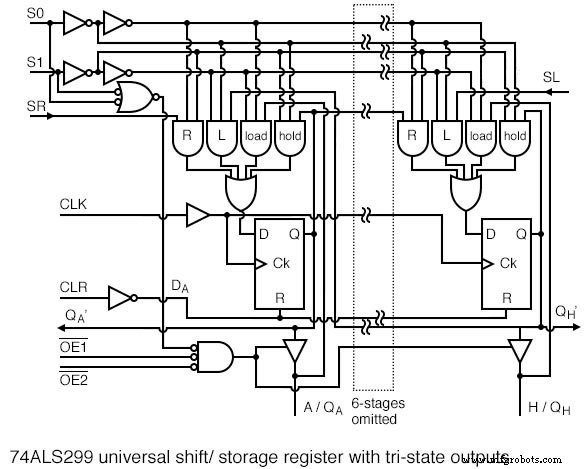

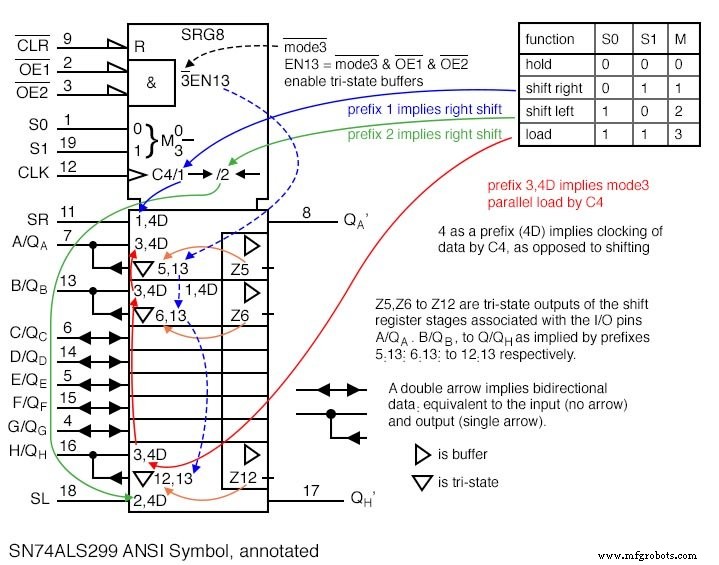

Tabel di atas, diringkas dari lembar data ‘299 data, merangkum pengoperasian register geser/penyimpanan universal 74ALS299.

Ikuti tautan '299 di atas untuk detail lengkap. Gerbang Multiplexer R , L , muat beroperasi seperti pada gambar “shift kiri/kanan register” sebelumnya.

Perbedaannya adalah bahwa mode memasukkan S1 dan S0 pilih shift left, shift right, dan load dengan mode yang disetel ke S1 S0 = ke 01 , 10 , dan 11 masing-masing seperti yang ditunjukkan pada tabel, mengaktifkan gerbang multiplekser L , B , dan muat masing-masing.

Lihat tabel. Perbedaan kecil adalah jalur beban paralel dari output tri-state. Sebenarnya buffer tri-state (harus) dinonaktifkan oleh S1 S0 =11 untuk mengapungkan I/O bus untuk digunakan sebagai input.

Bus adalah kumpulan sinyal yang serupa. Masukan diterapkan ke A , B melalui H (pin yang sama dengan QA , TB , melalui QH ) dan dirutekan ke load gerbang di multiplexer, dan di D masukan dari FF. Data adalah beban paralel pada pulsa clock.

Satu gerbang multiplexer baru adalah gerbang AND berlabel hold , diaktifkan oleh S1 S0 =00 . tahan gerbang memungkinkan jalur dari Q keluaran FF kembali ke tahan gerbang, ke input D dari FF yang sama. Hasilnya adalah dengan mode S1 S0 =00 , output terus dimuat ulang dengan setiap pulsa clock baru. Dengan demikian, data disimpan. Ini diringkas dalam tabel.

Untuk membaca data dari keluaran QA , TB , melalui QH , buffer tri-status harus diaktifkan dengan OE2’, OE1’ =00 dan mode =S1 S0 =00, 01, atau 10 .

Artinya, mode adalah apa saja kecuali memuat . Lihat tabel kedua.

Menggeser data ke kanan dari paket ke kiri, menggeser SR memasukkan. Setiap data bergeser ke kanan dari tahap QH mengalir ke kanan melalui QH '.

Output ini tidak terpengaruh oleh buffer tri-state. Urutan geser ke kanan untuk S1 S0 =10 adalah:

PL> TA> TB> TC> TB> TB> TB> TG> TH (TH ’)

Pergeseran data ke kiri dari sebuah paket ke pergeseran kanan pada SL memasukkan. Setiap data bergeser ke kiri dari tahap QA mengalir ke kiri melalui QA ', juga tidak terpengaruh oleh buffer tri-state. Urutan geser ke kiri untuk S1 S0 =01 adalah:

(TA ’) TA

Pergeseran dapat terjadi dengan buffer tri-status dinonaktifkan oleh salah satu OE2' atau OE1’ =1 . Padahal, output isi register tidak akan dapat diakses. Lihat tabel.

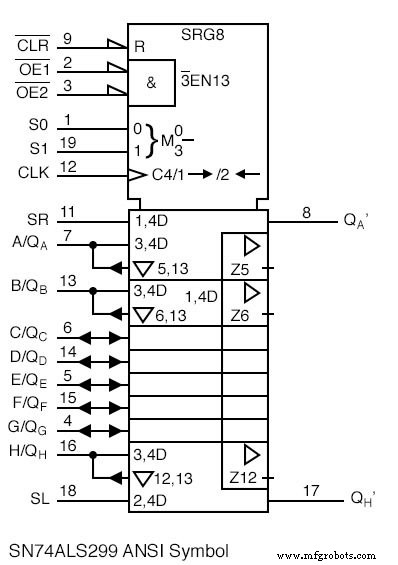

Simbol ANSI "bersih" untuk register geser universal 8-bit paralel-in/parallel-out SN74ALS299 dengan output tri-status ditampilkan untuk referensi di atas.

Versi beranotasi dari simbol ANSI ditampilkan untuk memperjelas terminologi yang terkandung di dalamnya.

Perhatikan bahwa mode ANSI (S0 S1) dibalik dari urutan (S1 S0) yang digunakan pada tabel sebelumnya.

Itu membalikkan angka mode desimal (1 &2). Bagaimanapun, kami sepenuhnya setuju dengan lembar data resmi, menyalin ketidakkonsistenan ini.

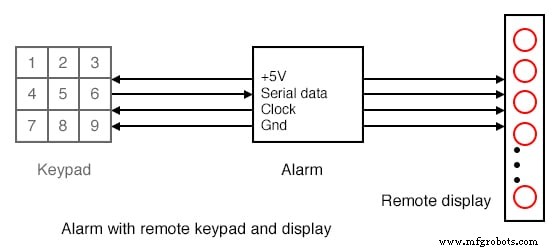

Alarm dengan diagram blok keypad jarak jauh diulang di bawah ini. Sebelumnya, kami membuat pembaca keypad dan tampilan jarak jauh sebagai unit terpisah.

Sekarang kita akan menggabungkan keypad dan tampilan menjadi satu unit menggunakan register geser universal.

Meskipun terpisah dalam diagram, Keypad dan Display keduanya terdapat dalam enklosur jarak jauh yang sama.

Kami akan memuat data keyboard secara paralel ke register geser pada satu pulsa clock, lalu memindahkannya ke kotak alarm utama.

Pada saat yang sama, kami akan memindahkan data LED dari alarm utama ke register geser jarak jauh untuk menerangi LED.

Kami akan secara bersamaan memindahkan data keyboard dan data LED ke register geser.

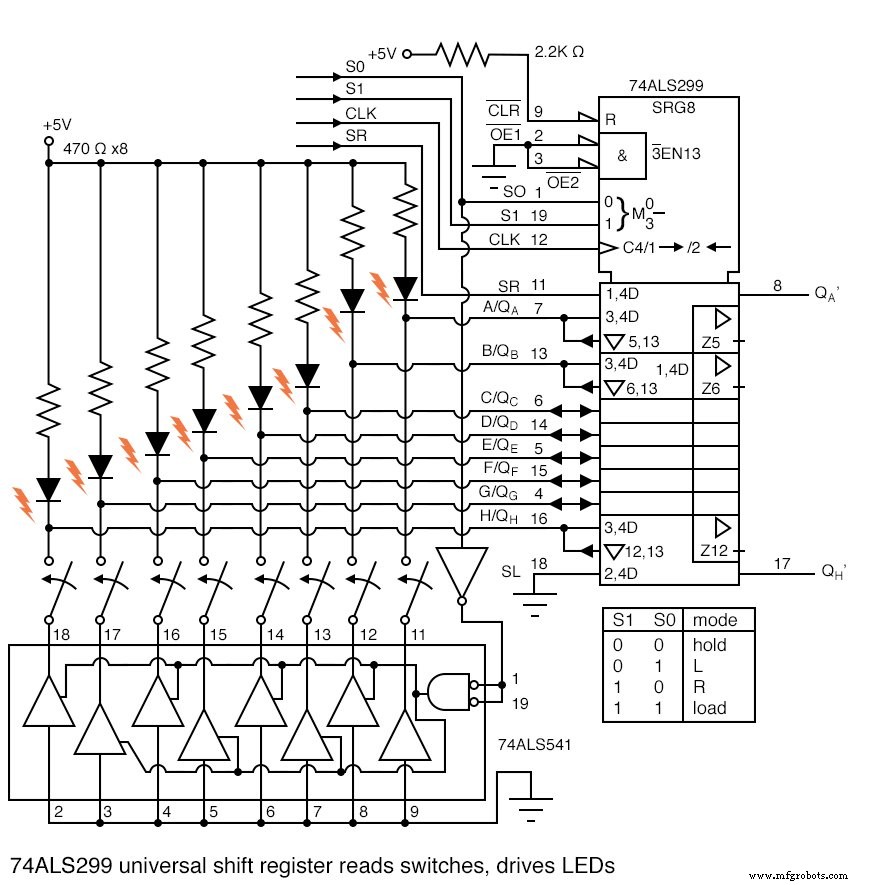

Delapan LED dan resistor pembatas arus terhubung ke delapan pin I/O dari register geser universal 74ALS299.

LED hanya dapat digerakkan selama Mode 3 dengan S1=0 S0=0 . OE1' dan OE2' tristate enable di-ground untuk secara permanen mengaktifkan output tristate selama mode 0, 1, 2 .

Itu akan menyebabkan LED menyala (berkedip) selama pemindahan gigi. Jika ini adalah masalah EN1 ’ dan EN2’ bisa di-unground dan diparalelkan dengan S1 dan S0 masing-masing untuk hanya mengaktifkan buffer tristate dan menyalakan LED selama mode tahan, 3 . Mari kita sederhanakan untuk contoh ini.

Selama pemuatan paralel, S0=1 terbalik ke 0, memungkinkan buffer oktal tristate untuk mengardekan wiper sakelar.

Kontak sakelar atas, terbuka, ditarik ke logika tinggi oleh kombinasi resistor-LED pada delapan input.

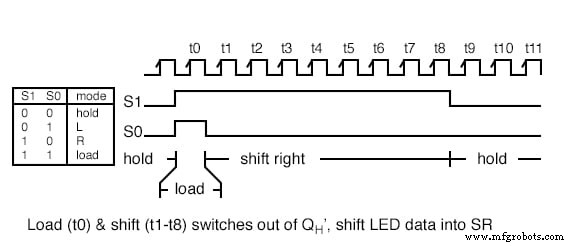

Penutupan sakelar apa pun akan memperpendek input rendah. Kami memuat data sakelar secara paralel ke ‘299 pada jam t0 saat keduanya S0 dan S1 tinggi. Lihat bentuk gelombang di bawah.

Sekali S0 hampir habis, delapan jam (t0 ket8 ) menggeser data penutupan sakelar keluar dari ‘299 melalui Th ' pin.

Pada saat yang sama, data LED baru digeser pada SR dari 299 oleh delapan jam yang sama. Data LED menggantikan data penutupan sakelar saat pemindahan berlangsung.

Setelah jam shift ke-8, t8 , S1 menjadi rendah untuk menghasilkan mode penahanan (S1 S0 =00 ). Data dalam register geser tetap sama meskipun ada lebih banyak jam, misalnya T9 , t10 , dll.

Dari mana datangnya bentuk gelombang? Mereka dapat dihasilkan oleh mikroprosesor jika kecepatan clock tidak lebih dari 100 kHz, dalam hal ini, akan merepotkan untuk menghasilkan clock apa pun setelah t8 .

Jika jam berada dalam kisaran megahertz, jam akan terus berjalan. Jam, S1 dan S0 akan dihasilkan oleh logika digital, tidak ditampilkan di sini.

LEMBAR KERJA TERKAIT:

Teknologi Industri

Kami telah menggunakan analitik untuk meningkatkan proses produksi kami di pabrik Bosch selama bertahun-tahun. Jadi, apa yang baru dalam analitik di bidang manufaktur, dan apa langkah selanjutnya? Metodologi kami untuk analisis persyaratan membuat semua perbedaan Ada berbagai cara untuk menjalanka

Komponen dan persediaan Arduino Nano R3 × 1 Texas Instruments Shift Register- Serial to Parallel 74HC595 × 4 Ukuran Penuh Papan Tempat Memotong Roti Tanpa Solder × 1 LED (generik) Tergantung pada preferensi Anda. × 1 Resistor 100 ohm Tergantung pada LED

Arduino Serial:Komunikasi Serial oleh Arduino Latar Belakang Komunikasi Serial: Ketika mikrokontroler atau mikroprosesor perlu berkomunikasi dengan dunia luar, maka mereka menyediakan data dalam bentuk paket 8 bit, jadi jika satu sistem perlu berkomunikasi dengan yang lain, maka total 8 kabel kabel

easymon adalah solusi pemantauan jarak jauh yang menghadirkan kemudahan penggunaan dunia ponsel cerdas ke domain pengontrol mesin. Hanya perlu menginstal ekstensi fungsi PLCnext dari toko PLCnext dan aplikasi smartphone yang sesuai dari iOS atau Google Play Store. Setelah konfigurasi yang cepat dan