Metode Supresi Refleksi Sinyal dalam Tata Letak PCB Berkecepatan Tinggi

Dengan perkembangan ilmu dan teknologi elektronik yang akan datang, sistem elektronik yang disusun oleh chip IC berkembang pesat menuju skala besar, mini dan kecepatan tinggi. Bersamaan dengan itu, masalah muncul juga bahwa menyusutnya volume sistem elektronik menyebabkan pembesaran kepadatan perutean sirkuit sementara frekuensi sinyal naik terus-menerus dan waktu pergantian tepi sinyal menjadi pendek. Ketika penundaan interkoneksi sinyal lebih besar dari waktu pergantian sinyal sebesar 10%, lead sinyal di papan akan menampilkan efek saluran transmisi, membuat serangkaian masalah seperti refleksi sinyal dan crosstalk semakin menonjol. Munculnya masalah kecepatan tinggi membawa tantangan yang lebih besar untuk desain perangkat keras dan jika beberapa desain yang dianggap benar dari perspektif logika gagal diproses secara tidak sesuai, seluruh desain akan mengalami kegagalan. Oleh karena itu, bagaimana memecahkan masalah sirkuit berkecepatan tinggi telah menjadi salah satu elemen penting yang menentukan keberhasilan sistem.

Prinsip Refleksi dan Pengaruhnya

• Prinsip refleksi

Alasan langsung untuk refleksi terletak pada ketidakcocokan impedansi saluran transmisi yang mengarah pada penyerapan energi sinyal yang tidak lengkap di terminal. Masalah refleksi mencerminkan kualitas sinyal jaringan tunggal, terkait dengan sifat fisik jalur sinyal jaringan tunggal dan jalur kembali. Biasanya, sifat fisik perutean PCB memiliki pengaruh besar pada saluran transmisi, terutama termasuk bahan perutean, lebar perutean, ketebalan perutean, jarak antara bidang perutean dan bidang lainnya, dan konstanta dielektrik dari bahan yang berdekatan. Ketika sinyal sedang ditransmisikan di sepanjang jaringan tunggal, perubahan impedansi transien dari saluran interkoneksi akan dihasilkan. Jika impedansi interkoneksi yang dirasakan oleh sinyal tetap tidak berubah, non-distorsi akan dipertahankan. Jika impedansi interkoneksi yang dirasakan oleh sinyal terus berubah, distorsi akan dihasilkan dengan refleksi yang dihasilkan pada titik perubahan. Sinyal pantulan akan ditransmisikan kembali ke ujung emisi sinyal dan akan dipantulkan kembali hingga menyusut dengan berkurangnya energi. Akhirnya, tegangan dan arus sinyal akan menjadi stabil.

• Perhitungan refleksi

Ketika sinyal ditransmisikan ke depan sepanjang saluran transmisi, impedansi transien akan dirasakan setiap saat. Jika impedansi yang dirasakan oleh sinyal konstan, maka akan diteruskan secara normal. Selama impedansi yang dirasakan berubah, refleksi akan selalu terjadi apa pun penyebabnya. Indeks signifikan yang mengukur jumlah refleksi adalah koefisien refleksi yang menunjukkan rasio antara tegangan refleksi dan tegangan sinyal asli. Koefisien refleksi dapat didefinisikan menurut rumus  .

.

Dalam rumus ini, Z1 mengacu pada impedansi setelah perubahan sementara Z0 impedansi sebelum perubahan. Misalkan impedansi karakteristik dari perutean PCB adalah 50Ω. Dalam proses transmisi, resistor 150Ω ditemui dan kemudian koefisien refleksi adalah (150-50)/(150+50)=1/2 (Dalam keadaan ini, pengaruh kapasitansi dan induktansi parasit tidak dipertimbangkan dengan resistor sebagai resistor murni yang ideal). Hasil ini menunjukkan bahwa setengah dari energi sinyal asli ditransmisikan kembali ke terminal sumber. Jika tegangan sinyal transmisi adalah 5V, tegangan refleksi adalah 2.5V.

• Pengaruh refleksi

1). Distorsi sinyal yang disebabkan oleh refleksi

Jika kabel tidak diputus dengan benar, pulsa sinyal dari ujung penggerak akan dipantulkan di terminal penerima. Ketika sinyal yang dipantulkan cukup kuat, bentuk gelombang yang ditumpuk mungkin akan mengubah kondisi logika yang mengarah ke efek yang tidak terduga, menyebabkan distorsi garis besar sinyal. Ketika distorsi menjadi begitu jelas, banyak kesalahan mungkin akan disebabkan oleh kegagalan desain. Sementara itu, sinyal dengan distorsi lebih sensitif terhadap noise, yang juga akan menyebabkan kegagalan desain.

2). Overshooting dan undershooting disebabkan oleh refleksi

Overshooting mengacu pada fakta bahwa nilai puncak pertama atau nilai lembah melebihi tegangan. Untuk tepi naik, mengacu pada fakta bahwa nilai puncak pertama melebihi tegangan tertinggi sedangkan untuk tepi jatuh, mengacu pada fakta bahwa nilai lembah pertama melebihi tegangan terendah. Overshooting yang berlebihan mungkin akan merusak dioda proteksi, yang menyebabkan kegagalan dini. Undershooting mengacu pada fakta bahwa nilai lembah atau nilai puncak berikutnya mungkin akan menghasilkan sinyal clock yang salah, yang menyebabkan kesalahan pembacaan dan pengoperasian sistem yang salah.

3). Osilasi

Osilasi juga merupakan gejala yang disebabkan oleh refleksi. Dengan sifat yang sama dengan overshooting, pengulangan overshooting dan undershooting disebut osilasi dalam lingkaran jam. Ini adalah hasil dari fakta bahwa energi redundan yang dihasilkan dari refleksi gagal diserap dalam waktu di sirkuit.

Metode Penekanan Refleksi

Elemen utama yang menyebabkan refleksi termasuk bentuk geometris dari perutean (lebar, panjang, sudut belokan), konversi bidang perutean jaringan yang sama, transmisi melalui konektor, diskontinuitas antara daya dan ground, struktur topologi yang salah dan ketidakcocokan ujung jaringan. Metode penekanan utama akan diperkenalkan di bagian berikut.

• Peningkatan frekuensi sistem

Laju transformasi tepi sinyal berkurang dalam situasi yang memungkinkan sehingga pantulan saluran transmisi akan mencapai keadaan stabil sebelum koneksi antara sinyal dan saluran transmisi. Di satu sisi, peraturan desain harus dipenuhi; di sisi lain, komponen dengan kecepatan lambat harus diambil untuk menghindari campuran antara berbagai jenis sinyal.

• Optimalisasi pemrosesan sinyal

Karena tuntutan yang ketat dalam hal urutan waktu, komponen dan node yang dapat menyebabkan masalah kecepatan tinggi harus ditentukan terlebih dahulu. Semua jenis persyaratan mengenai tata letak komponen dan perutean harus disesuaikan dan indeks desain integritas sinyal akhirnya akan dikendalikan. Metode pemrosesan utama meliputi:

1). Papan PCB yang relatif tipis diterapkan untuk mengurangi parameter parasit melalui lubang.

2). Jumlah lapisan harus diatur sesuai. Lapisan tengah harus digunakan sepenuhnya untuk mengatur perisai agar dapat menerapkan pembumian yang berdekatan dengan lebih baik, yang secara efektif akan mengurangi induktansi parasit, memperpendek panjang transmisi sinyal dan sangat meningkatkan crosstalk antar sinyal.

3). Bentuk geometris garis sinyal pada PCB harus dikontrol dengan pengurangan belokan dan titik diskontinuitas impedansi perutean diminimalkan. Khusus untuk perutean di sirkuit frekuensi tinggi, garis lurus penuh harus diterapkan. Saat belokan diperlukan, garis putus-putus atau busur 45° dapat diterapkan, yang akan mengurangi radiasi eksternal dari sinyal frekuensi tinggi dan sambungan antara sinyal frekuensi tinggi.

4). Perutean jalur sinyal penting harus diatur dalam bidang yang sama untuk mengurangi lubang yang tidak perlu.

5). Integritas bidang harus dipastikan untuk menyediakan jalur reflow dengan impedansi rendah untuk saluran sinyal. Hal ini bertujuan untuk mengurangi kopling impedansi mode umum dan kebisingan sakelar mode umum untuk mengurangi atau menghilangkan masalah integritas sinyal yang berkaitan dengan sistem catu daya.

6). Penerapan struktur topologi perutean yang benar.

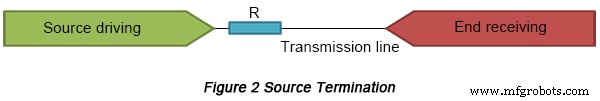

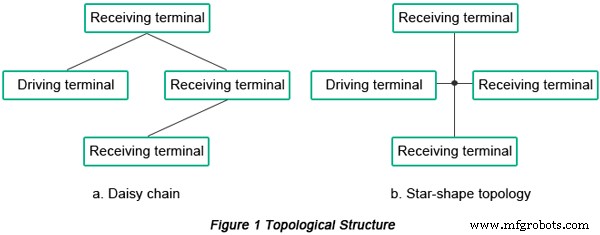

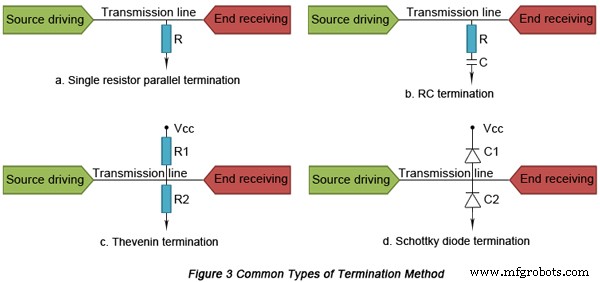

Struktur topologi perutean mengacu pada urutan perutean dan struktur garis sinyal. Dalam rangkaian praktis, selalu ada situasi di mana satu sumber penggerak menggerakkan banyak beban dan sumber penggerak dan beban sesuai dengan topologi struktur. Struktur topologi yang berbeda memiliki pengaruh yang berbeda pada sinyal. Biasanya, dua jenis struktur topologi dasar diterapkan dalam perutean PCB, yaitu rantai daisy dan topologi bentuk awal, yang ditunjukkan pada Gambar 1 di bawah ini.

sebuah. Rantai Daisy

Perutean dimulai dari terminal penggerak dan tiba di setiap terminal penerima secara berurutan. Jika resistor seri diterapkan untuk mengubah sifat sinyal, posisi resistor seri harus dekat dengan terminal penggerak. Dalam hal kontrol interferensi harmonik yang lebih tinggi, rantai daisy memiliki efek perutean terbaik. Namun, jenis perutean ini memiliki perutean paling rendah, kurang dari 100%. Dalam desain praktis, panjang cabang dalam rantai daisy harus sesingkat mungkin. Ruang perutean struktur topologi ini kecil dan resistor tunggal dapat diterapkan untuk kompatibilitas dengan terminasi. Selain itu, jenis struktur perutean ini membuat penerimaan sinyal tidak selaras pada terminal penerima sinyal yang berbeda.

b. Topologi bentuk bintang

Jenis perutean ini mampu secara efektif menghindari nonsinkronisasi sinyal clock tetapi memiliki kelemahan bahwa resistor terminal diperlukan oleh setiap cabang. Nilai resistansi resistor terminal harus sesuai dengan impedansi karakteristik in-line. Untuk sistem yang sinyal berbedanya memiliki persyaratan simultan di terminal penerima, topologi bentuk bintang adalah yang paling cocok.

• Metode penghentian

Impedansi karakteristik pada jalur transmisi sinyal harus dijaga konstan, yaitu koefisien refleksi adalah 0, yang berarti tidak ada refleksi pada jalur transmisi. Situasi ini disebut kompatibilitas impedansi. Pada saat ini, sinyal mengirimkan ground ide ke terminal. Umumnya, panjang saluran transmisi harus sesuai dengan kondisi  .

.

Dalam persamaan ini, L mengacu pada panjang saluran transmisi; tr mengacu pada waktu naik sinyal terminal sumber; tpd1 mengacu pada penundaan transmisi beban pada setiap satuan panjang pada saluran transmisi. Ketika transfer level terintegrasi terjadi sebelum refleksi tiba di terminal jauh, teknologi pencocokan terminal diperlukan untuk diterapkan. Prinsip koneksi terminal saluran transmisi meliputi:jika koefisien refleksi beban atau koefisien refleksi sumber nol, refleksi akan dihilangkan. Umumnya, dua strategi diterapkan:impedansi sumber dibuat kompatibel dengan impedansi saluran transmisi, yaitu pemutusan sumber sementara impedansi beban dibuat agar kompatibel dengan impedansi saluran transmisi, yaitu pemutusan akhir.

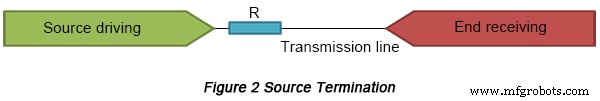

1). Penghentian sumber

Terminasi sumber terutama merupakan metode terminasi seri yang diterapkan dengan memasang resistor seri di saluran transmisi pada posisi yang berdekatan dengan ujung dekat sumber. Jumlah nilai resistansi resistor seri dan terminal penggerak harus sama dengan nilai resistansi saluran transmisi. Prinsip terminasi seri adalah menghilangkan tegangan pantul dari terminal beban dengan menghentikan refleksi kedua saluran transmisi, yang ditunjukkan pada Gambar 2.

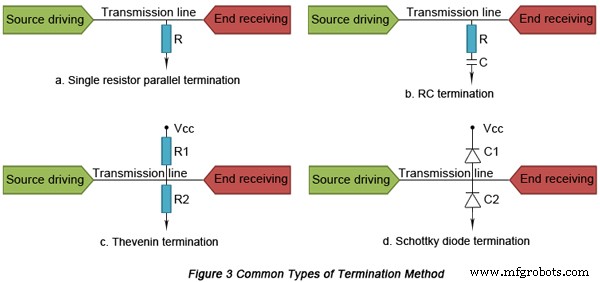

2). Akhiri penghentian

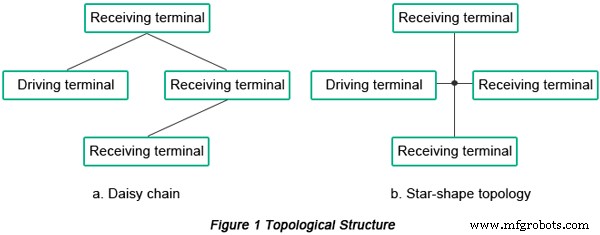

Prinsip utama terminasi ujung terletak pada resistor pull-up atau pull-down yang menambah posisi terminal beban yang berdekatan untuk menerapkan pencocokan impedansi. Terminasi ujung umumnya dapat dibagi menjadi terminasi paralel resistor tunggal, terminasi RC, terminasi Thevenin dan terminasi dioda Schottky, seperti yang ditunjukkan pada Gambar 3.

Nilai resistansi pada terminasi paralel resistor tunggal sama dengan impedansi saluran transmisi. Nilai dua resistor dalam pemutusan Thevenin harus mengikuti rumus:Z0 =R1 R2 /(R1 +R2 ). Nilai kapasitansi dalam terminasi RC mengikuti rumus:C=3T/Z0 di mana T mengacu pada waktu naik sinyal sementara Z0 mengacu pada impedansi saluran transmisi.

Dari perspektif desain sistem, terminasi paralel harus diambil terlebih dahulu karena paling mampu mengurangi noise, EMI dan RFI dibandingkan dengan tiga metode terminasi lainnya. Menurut keadaan praktis, metode penghentian yang sesuai diambil dan bila perlu, desain simulasi harus diterapkan.

Kesimpulan

Dalam desain PCB berkecepatan tinggi, prasyarat yang berhasil mencakup tata letak dan perutean yang wajar, penghindaran belokan yang tidak perlu dan melalui vias, kontinuitas impedansi, bidang referensi sinyal terintegrasi, dan landasan yang sangat baik. Untuk mengoptimalkan desain &integritas sinyal dan mendapatkan kompatibilitas elektromagnetik yang lebih tinggi, verifikasi simulasi desain harus diterapkan. Ini membantu desainer menangani cacat desain tepat waktu dan menutupi kekurangan dalam desain PCB.

Sumber Daya Bermanfaat

• Kiat Tata Letak Berkecepatan Tinggi

• Tantangan Desain PCB Berkecepatan Tinggi pada Integritas Sinyal dan Solusinya

• Analisis Integritas Sinyal dan Desain PCB pada Sirkuit Campuran Digital-Analog Berkecepatan Tinggi

• Layanan Pembuatan PCB Fitur Lengkap dari PCBCart - Beberapa opsi Nilai tambah

• Layanan Perakitan PCB Tingkat Lanjut dari PCBCart - Mulai dari 1 buah

.

.

.

.