Pemrosesan Isometrik Diferensial dan Verifikasi Simulasi Desain PCB Berkecepatan Tinggi

Pengaruh Penundaan Relatif pada Sinyal

Sinyal yang ditransmisikan dalam jalur sinyal diferensial mengandung komponen mode diferensial dan komponen mode umum dari sinyal.

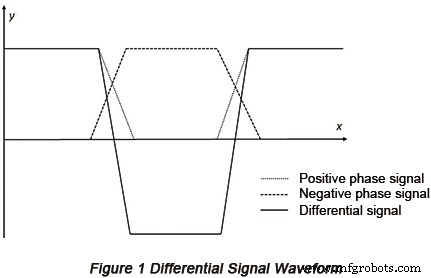

Jumlah sinyal diferensial mengacu pada perbedaan antara dua sinyal berikut rumus Vdiff =V1 - V2 . Jumlah sinyal mode umum mengacu pada setengah dari jumlah dua sinyal berikut rumus: . Oleh karena itu, perubahan tegangan satu saluran pasti mengarah pada pengaruh simultan pada sinyal mode diferensial dan sinyal mode umum. Selanjutnya, perangkat lunak grafik diterapkan untuk menggambar diagram fungsi matematika untuk mempelajari pengaruhnya pada sinyal mode diferensial dan sinyal mode umum. Untuk kenyamanan penelitian, sinyal dapat dianalisis dengan mensimulasikannya menjadi bentuk gelombang trapesium dengan waktu atas dan waktu henti yang sama.

. Oleh karena itu, perubahan tegangan satu saluran pasti mengarah pada pengaruh simultan pada sinyal mode diferensial dan sinyal mode umum. Selanjutnya, perangkat lunak grafik diterapkan untuk menggambar diagram fungsi matematika untuk mempelajari pengaruhnya pada sinyal mode diferensial dan sinyal mode umum. Untuk kenyamanan penelitian, sinyal dapat dianalisis dengan mensimulasikannya menjadi bentuk gelombang trapesium dengan waktu atas dan waktu henti yang sama.

• Pengaruh pada sinyal diferensial

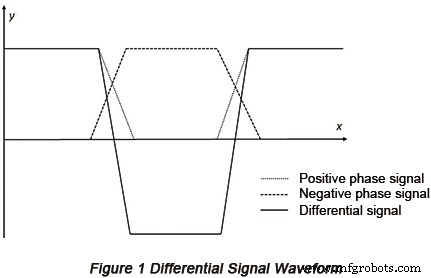

Sinyal terminal fase positif, sinyal terminal fase negatif dan sinyal diferensial dari pasangan garis diferensial ditampilkan pada Gambar 1 di bawah ini di mana garis penuh mewakili gelombang sinyal diferensial.

Jika penempatan fasa terjadi dari terminal fasa positif ke terminal fasa negatif, maka akan terjadi perubahan selisih antara sinyal terminal fasa positif dan sinyal terminal fasa negatif pada tepi atas atau bawah dan perubahan ini akan berubah seiring dengan perubahan fasa. Tr digunakan untuk berdiri untuk waktu yang lebih singkat antara waktu naik dan turun. Dapat diindikasikan bahwa ketika penempatan fase kurang dari titik dua Tr , distorsi sinyal relatif kecil dan peningkatan penempatan fase menyebabkan distorsi yang kuat dari bentuk gelombang diferensial. Saat penempatan fase melebihi Tr , daerah non-monotonik akan terjadi pada bentuk gelombang. Di sini area non-monotonik adalah garis lurus. Namun, untuk sinyal praktis, karena pantulan, kenaikan dan penurunan besar dapat terjadi di area non-monotonik dengan pulsa interferensi terbentuk yang mengarah ke pemicu palsu, yang harus dihindari. Selain itu, tepi atas bentuk gelombang diferensial menjadi lambat dengan meningkatnya penempatan fase, yang dapat menyebabkan waktu pembentukan yang tidak mencukupi untuk sinyal data dan dapat menyebabkan waktu penahanan yang tidak memadai untuk sinyal clock.

• Pengaruh pada sinyal mode umum

Penempatan fase sinyal terminal tunggal tidak akan mempengaruhi bentuk gelombang diferensial tetapi mengubah bentuk gelombang sinyal mode umum. Ketika penempatan fase terjadi pada sinyal terminal positif, perubahan gelombang akan terjadi pada sinyal mode umum. Dapat diindikasikan bahwa rentang fluktuasi berhubungan dengan jumlah penempatan fasa. Ketika jumlah penempatan fase masing-masing 0,05Tr , 0,1Tr , 0,2Tr dan 0,5Tr , rentang fluktuasi mode umum masing-masing 5%, 10%, 20% dan 50% dari rentang fluktuasi asli. Ketika fase meningkat menjadi Tr atau lebih, fluktuasi akan meningkat menjadi sekitar 100% yang merupakan kisaran fluktuasi tertinggi. Perubahan sinyal mode umum dapat menyebabkan masalah EMI dan karena sinyal kode umum tidak diterima di terminal dalam banyak kondisi, pantulan akan terbentuk di terminal penerima, yang menyebabkan sinyal berdering. Oleh karena itu, rentang fluktuasi sinyal mode umum harus dikurangi sebanyak mungkin.

Kesimpulannya, penundaan relatif yang terlalu besar antara pasangan diferensial dapat menyebabkan pemicu sinyal yang salah, pantulan sinyal, EMI, dan masalah urutan waktu. Namun, tingkat pengaruh sinyal penundaan relatif tergantung pada faktor skala yang kompatibel dengan sinyal Tr . Ketika faktor skala adalah 0,05, distorsi sinyal diferensial hampir dapat diabaikan. Namun, untuk sinyal mode umum, ketika faktor skala adalah 0,05, fluktuasi tegangan sinyal mode umum dapat dikontrol pada sekitar 5%. Kemudian, bahkan dalam situasi pemantulan penuh, tegangan pemantulan yang ditumpuk pada saluran sinyal hanya 10% dari fluktuasi asli, yang biasanya merupakan nilai yang dapat diterima. Oleh karena itu, dalam proses desain PCB berkecepatan tinggi, penundaan relatif jalur sinyal diferensial dalam aturan regulasi perutean dapat diatur menjadi 0,05 Tr yang mampu memenuhi persyaratan integritas sinyal.

Penentuan Kategori Keterlambatan Relatif

Berdasarkan analisis di atas, kunci penentuan kategori isometrik diferensial, yaitu penentuan tundaan relatif pasangan diferensial, terletak pada penentuan Tr mengacu pada nilai terkecil di antara waktu atas dan bawah dari sinyal diferensial. Output dari rise time dan fall time sebenarnya merupakan output dari kombinasi impedansi dan kapasitansi. Oleh karena itu, waktu naik/turun tanpa pembebanan sebenarnya adalah waktu naik/turun yang melekat.

Tiga metode berikut dapat diterapkan untuk mendapatkan nilai Tr :

• Waktu naik/turun dapat langsung diperoleh dari manual komponen. Namun, dalam kebanyakan situasi, parameter ini tidak tersedia.

• Nilai Tr dapat diperoleh dari kata kunci Ramp dari model komponen IBIS (Input/Output Buffer Informational Specification). Parameter waktu naik/turun di bawah kata kunci Ramp umumnya diukur pada port keluaran yang terhubung dengan resistor 50Ω, yang biasanya 20% hingga 80% dari waktu tegangan akhir. Karena parameter diperoleh tanpa mempertimbangkan pengaruh paket, sangat ketat bagi kita untuk menggunakan waktu naik/turun sebagai nilai Tr .

• Nilai Tr dapat diperkirakan sesuai dengan frekuensi clock minimum atau frekuensi clock maksimum dari sinyal output. Karena tepi naik distributif kira-kira 10% dari frekuensi clock di sebagian besar sistem digital berkecepatan tinggi, nilai Tr dapat diperkirakan dengan periode clock minimum Tclk yang diberikan berdasarkan rumus:Tr =Tklk x 10%.

Nilai perkiraan yang diperoleh melalui periode clock biasanya ketat karena parameter parasit paket atau pemuatan komponen akan membuat waktu naik/turun yang melekat pada transistor sangat lambat.

Dalam kerja praktek, dalam kebanyakan situasi, perancang sirkuit tidak memberikan informasi Tr untuk insinyur tata letak PCB yang hanya menerima beberapa tuntutan ambigu dalam hal kontrol isometrik diferensial. Metode ketiga tidak diragukan lagi menyediakan skema sederhana untuk insinyur tata letak PCB selama frekuensi clock tertinggi pada jalur sinyal diperoleh. Frekuensi clock tertinggi dianggap sebagai parameter desain yang paling dapat diandalkan untuk perancang sirkuit dan biasanya diberikan kepada insinyur tata letak PCB di awal desain PCB.

Metode ketiga biasanya mengarah ke daftar nilai referensi dalam kategori kontrol penundaan relatif antara pasangan diferensial, seperti yang ditunjukkan pada tabel di bawah ini.

| Frekuensi Jam/ns | Frekuensi Jam/MHz | Kategori Penundaan Relatif/ps | Panjang Jalur Transmisi/mil |

| 3.75 | 266 | 18.8 | 105 |

| 3 | 333 | 15 | 84 |

| 2.5 | 400 | 12.5 | 70 |

| 1.87 | 533 | 9.4 | 52 |

| 1.5 | 667 | 7.5 | 42 |

| 1,25 | 800 | 6.3 | 35 |

Verifikasi Simulasi

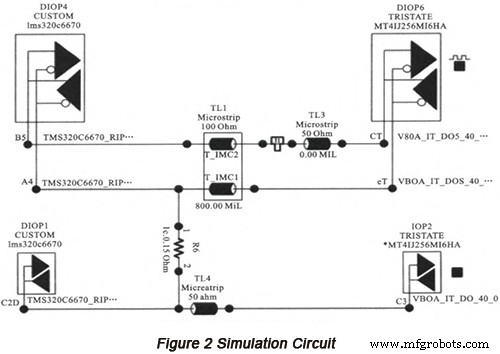

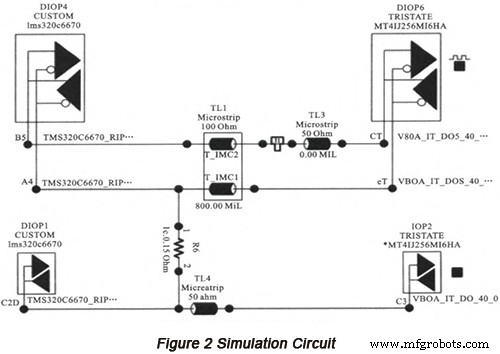

Ambil sinyal diferensial DQS (Data Strobe) antara TSM320 dan MT41J256M16 sebagai contoh, perangkat lunak simulasi irama diterapkan untuk mengirimkan sinyal DOS ke memori DRR3 untuk mensimulasikan chip kontrol memori, menganalisis pengaruhnya terhadap waktu penahanan pembentukan sinyal data dan memverifikasi analisis di atas. Rangkaian simulasi ditunjukkan pada Gambar 2 di bawah ini.

Berdasarkan Gambar 2, tegangan referensi pin keluaran adalah 1.5V; chip kontrol memori terhubung langsung dengan chip memori melalui mode ODT (On-Die Termination) dengan saluran transmisi 800mil; impedansi diferensial adalah 100Ω dan frekuensi clock simulasi 800MHz. Saluran transmisi 50Ω dihubungkan secara serial dengan terminal fase positif DQS untuk mensimulasikan fenomena perbedaan pasangan diferensial. Dalam situasi perbedaan isometrik, panjang saluran transmisi terminal tunggal 50Ω adalah 0mil.

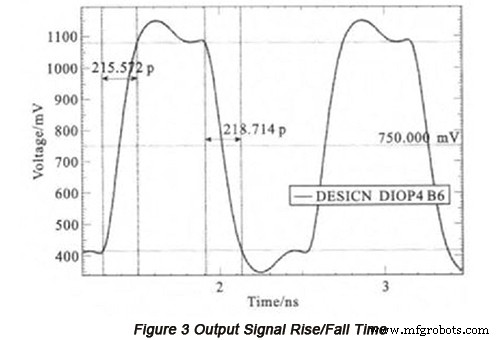

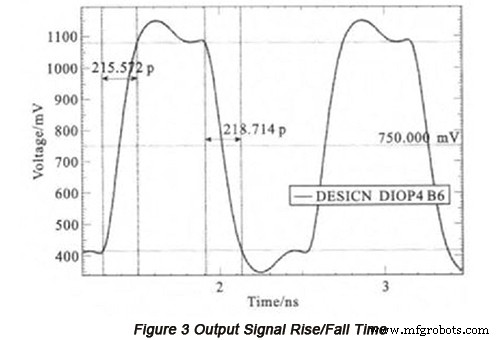

Simulasi dilakukan pada rangkaian isometrik diferensial. Gambar 3 mengilustrasikan sinyal keluaran pada terminal fase positif dari sinyal diferensial. Melalui pengukuran, waktu naik sekitar 216 ps sedangkan waktu jatuh 219 ps sehingga waktu naik/turun minimum Tr harus 216 ps.

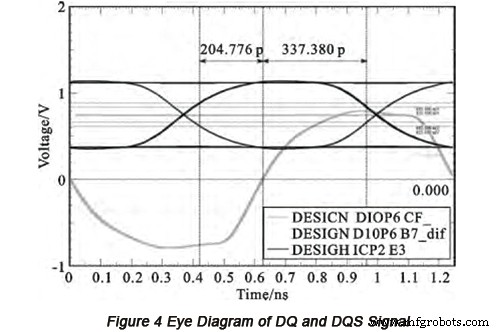

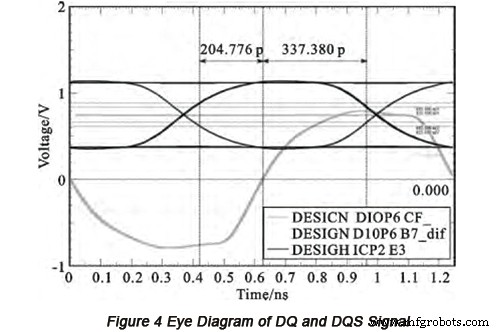

Gambar 4 adalah diagram mata sinyal data DQ dan sinyal gating DQS melalui simulasi dengan waktu pembentukan 205ps dan waktu penahanan 337ps. Menurut tingkat pergantian sinyal DQS dan DQ melalui simulasi dan berdasarkan manual data, waktu pembentukan minimum sinyal data oleh terminal penerima harus 85ps dan waktu penahanan minimum adalah 95ps. Oleh karena itu, overmeasure dari waktu pembentukan minimum adalah 120ps dan waktu penahanan 242ps.

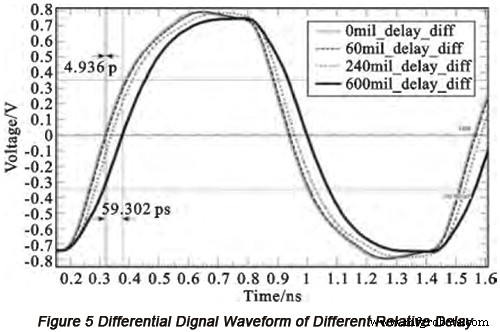

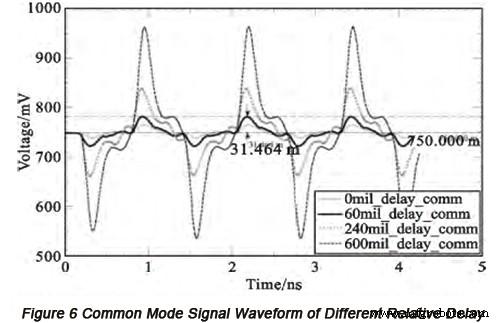

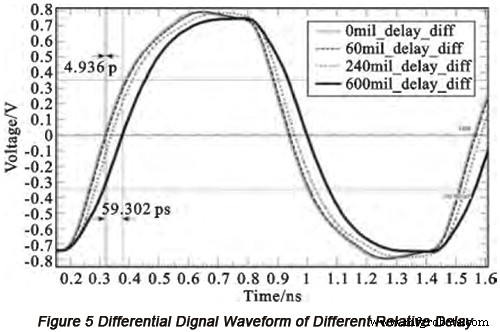

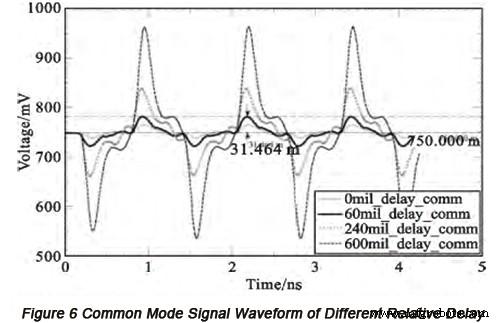

Situasi keberadaan 0,05Tr penempatan fase, 0.2Tr penempatan fase dan 0,5Tr penempatan fase di terminal fase positif harus dipertimbangkan. Sirkuit dapat disimulasikan dengan panjang saluran transmisi terminal tunggal yang masing-masing diatur menjadi 60mil, 240mil dan 600mil. Bentuk gelombang sinyal diferensial dan bentuk gelombang sinyal mode umum melalui simulasi selama 4 kali diilustrasikan pada Gambar 5 dan 6.

Berdasarkan Gambar 5, distorsi adalah minimum ketika penundaan relatif 0,05Tr dan 0.2Tr terjadi. Terutama ketika penundaan relatif adalah 0,05Tr , hanya penempatan sekitar 5 ps dari sinyal diferensial ke bentuk gelombang sinyal diferensial tanpa penundaan relatif sehingga pengukuran berlebih pembentukan sinyal data meningkat sekitar 5 ps dengan waktu penahanan berlebih berkurang sebesar 5 ps. Meskipun holding over-measure time berkurang, jumlah penempatan ini sangat sedikit untuk holding time 242ps. Urutan waktu dapat dihindari. Untuk situasi saat penundaan relatif 0,5Tr , penempatan bentuk gelombang sinyal DQS telah mencapai sekitar 60ps. Meskipun penempatan ini masih dalam kategori over-measure, namun perhatian yang cukup harus diberikan.

Berdasarkan Gambar 6, peningkatan penempatan fase menyebabkan fluktuasi periodik yang jelas pada gelombang dan peningkatan jangkauan secara bertahap. Ketika penundaan relatif masing-masing 0,05Tr , 0,2Tr dan 0,5Tr , nilai puncak terukur dari sinyal mode umum masing-masing adalah 61mV, 176mV, dan 430mV, di antaranya nilai tertinggi adalah tujuh kali nilai terendah. Kisaran fluktuasi terbesar masing-masing adalah 4,3%, 12%, dan 29%.

Kesimpulannya, hasil simulasi sesuai dengan hasil yang diperoleh melalui analisis diagram fungsi matematika. Ketika penundaan relatif antara pasangan diferensial kurang dari 0,05Tr , pengaruhnya terhadap sinyal cukup kecil.

Periode jam minimum dari sinyal keluaran pada terminal keluaran diterapkan untuk memperkirakan kategori kendali penundaan relatif. Berdasarkan manual komponen, periode clock minimum komponen adalah 1,25ns dengan frekuensi clock 800MHz. Menurut Tabel 1, penundaan relatif harus dikontrol dalam 6.3ps dengan panjang saluran transmisi 35mil. Rupanya, nilai ini jauh lebih kecil dari kategori kontrol penundaan relatif 0,05Tr melalui simulasi. Oleh karena itu, kategori kontrol penundaan relatif yang diperkirakan relatif konservatif, yang lebih spesifik daripada hasil simulasi.

Sumber Daya Bermanfaat

• Penelitian tentang Desain PCB Berkecepatan Tinggi dalam Sistem Aplikasi Tertanam

• Bagaimana Mendesain Bidang Gambar untuk PCB Berkecepatan Tinggi

• Desain PCB Berkecepatan Tinggi Tantangan pada Integritas Sinyal dan Solusinya

• Simulasi PCB Menggunakan OrCAD PSpice

• Layanan Pembuatan PCB Fitur Lengkap dari PCBCart - Beberapa Opsi Nilai Tambah

• Layanan Perakitan PCB Tingkat Lanjut dari PCBCart - Mulai dari 1 buah

. Oleh karena itu, perubahan tegangan satu saluran pasti mengarah pada pengaruh simultan pada sinyal mode diferensial dan sinyal mode umum. Selanjutnya, perangkat lunak grafik diterapkan untuk menggambar diagram fungsi matematika untuk mempelajari pengaruhnya pada sinyal mode diferensial dan sinyal mode umum. Untuk kenyamanan penelitian, sinyal dapat dianalisis dengan mensimulasikannya menjadi bentuk gelombang trapesium dengan waktu atas dan waktu henti yang sama.

. Oleh karena itu, perubahan tegangan satu saluran pasti mengarah pada pengaruh simultan pada sinyal mode diferensial dan sinyal mode umum. Selanjutnya, perangkat lunak grafik diterapkan untuk menggambar diagram fungsi matematika untuk mempelajari pengaruhnya pada sinyal mode diferensial dan sinyal mode umum. Untuk kenyamanan penelitian, sinyal dapat dianalisis dengan mensimulasikannya menjadi bentuk gelombang trapesium dengan waktu atas dan waktu henti yang sama.