Array dan Memori Verilog

Sebuah array deklarasi jaring atau variabel dapat berupa skalar atau vektor. Sejumlah dimensi dapat dibuat dengan menentukan rentang alamat setelah nama pengenal dan disebut array multi-dimensi. Array diperbolehkan di Verilog untuk reg , wire , integer dan real tipe data.

reg y1 [11:0]; // y is an scalar reg array of depth=12, each 1-bit wide

wire [0:7] y2 [3:0] // y is an 8-bit vector net with a depth of 4

reg [7:0] y3 [0:1][0:3]; // y is a 2D array rows=2,cols=4 each 8-bit wide

Indeks untuk setiap dimensi harus ditentukan untuk mengakses elemen tertentu dari array dan dapat menjadi ekspresi dari variabel lain. Sebuah array dapat dibentuk untuk setiap tipe data berbeda yang didukung di Verilog.

Perhatikan bahwa memori n 1-bit reg tidak sama dengan n-bit vector reg.

Tugas

y1 = 0; // Illegal - All elements can't be assigned in a single go

y2[0] = 8'ha2; // Assign 0xa2 to index=0

y2[2] = 8'h1c; // Assign 0x1c to index=2

y3[1][2] = 8'hdd; // Assign 0xdd to rows=1 cols=2

y3[0][0] = 8'haa; // Assign 0xaa to rows=0 cols=0

Contoh

Kode yang ditunjukkan di bawah ini hanya menunjukkan bagaimana array yang berbeda dapat dimodelkan, ditetapkan dan diakses. mem1 adalah vektor 8-bit, mem2 adalah array 8-bit dengan kedalaman 4 (ditentukan oleh rentang [0:3]) dan mem3 adalah array 2D vektor 16-bit dengan 4 baris dan 2 kolom. Variabel ini diberi nilai yang berbeda dan dicetak.

module des ();

reg [7:0] mem1; // reg vector 8-bit wide

reg [7:0] mem2 [0:3]; // 8-bit wide vector array with depth=4

reg [15:0] mem3 [0:3][0:1]; // 16-bit wide vector 2D array with rows=4,cols=2

initial begin

int i;

mem1 = 8'ha9;

$display ("mem1 = 0x%0h", mem1);

mem2[0] = 8'haa;

mem2[1] = 8'hbb;

mem2[2] = 8'hcc;

mem2[3] = 8'hdd;

for(i = 0; i < 4; i = i+1) begin

$display("mem2[%0d] = 0x%0h", i, mem2[i]);

end

for(int i = 0; i < 4; i += 1) begin

for(int j = 0; j < 2; j += 1) begin

mem3[i][j] = i + j;

$display("mem3[%0d][%0d] = 0x%0h", i, j, mem3[i][j]);

end

end

end

endmodule

Log Simulasi

ncsim> run

mem1 = 0xa9

mem2[0] = 0xaa

mem2[1] = 0xbb

mem2[2] = 0xcc

mem2[3] = 0xdd

mem3[0][0] = 0x0

mem3[0][1] = 0x1

mem3[1][0] = 0x1

mem3[1][1] = 0x2

mem3[2][0] = 0x2

mem3[2][1] = 0x3

mem3[3][0] = 0x3

mem3[3][1] = 0x4

ncsim: *W,RNQUIE: Simulation is complete.

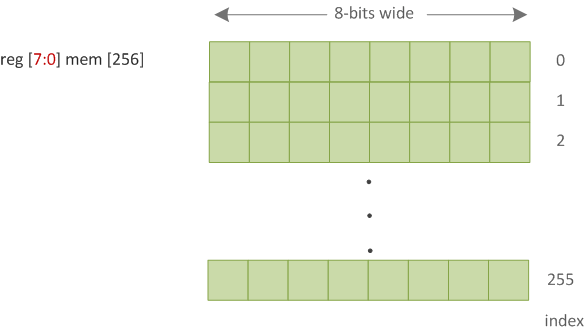

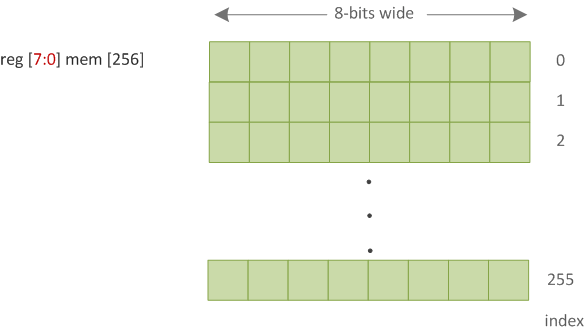

Kenangan

Memori adalah elemen penyimpanan digital yang membantu menyimpan data dan informasi dalam sirkuit digital. RAM dan ROM adalah contoh yang baik dari elemen memori tersebut. Elemen penyimpanan dapat dimodelkan menggunakan array satu dimensi dengan tipe reg dan disebut memori . Setiap elemen dalam memori dapat mewakili sebuah kata dan direferensikan menggunakan indeks array tunggal.

Daftar Vektor

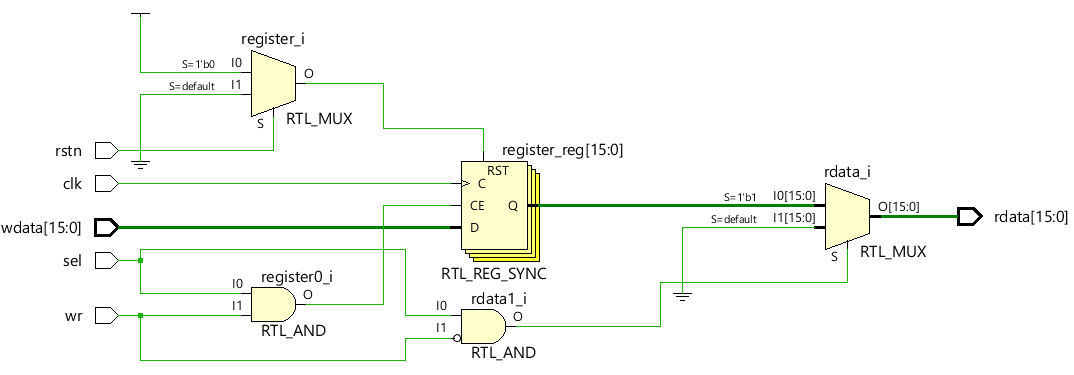

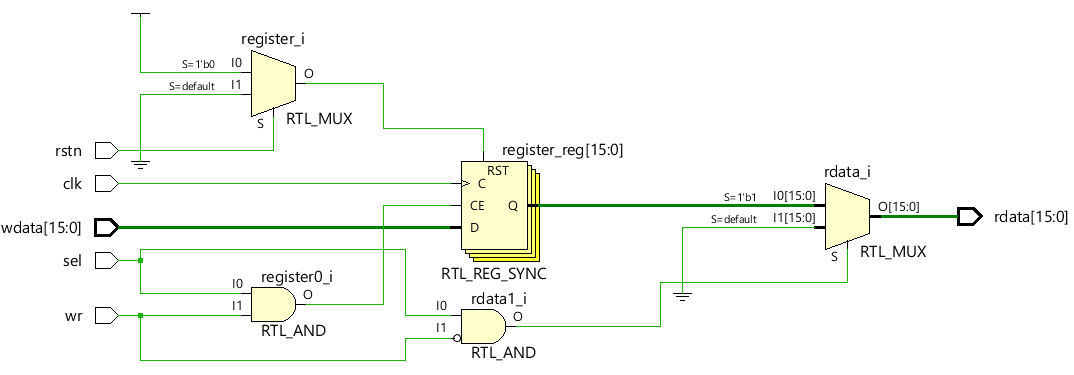

Vektor Verilog dideklarasikan menggunakan rentang ukuran di sisi kiri nama variabel dan ini diwujudkan menjadi jepit yang sesuai dengan ukuran variabel. Dalam kode yang ditunjukkan di bawah ini, modul desain menerima jam, reset dan beberapa sinyal kontrol untuk membaca dan menulis ke dalam blok.

Ini berisi elemen penyimpanan 16-bit yang disebut register yang hanya diperbarui selama menulis dan mengembalikan nilai saat ini selama membaca. Register ditulis ketika sel dan wr tinggi pada tepi jam yang sama. Ini mengembalikan data saat ini ketika sel tinggi dan wr rendah.

module des ( input clk,

input rstn,

input wr,

input sel,

input [15:0] wdata,

output [15:0] rdata);

reg [15:0] register;

always @ (posedge clk) begin

if (!rstn)

register <= 0;

else begin

if (sel & wr)

register <= wdata;

else

register <= register;

end

end

assign rdata = (sel & ~wr) ? register : 0;

endmodule

Skema perangkat keras menunjukkan bahwa kegagalan 16-bit diperbarui ketika logika kontrol untuk penulisan aktif dan nilai saat ini dikembalikan ketika logika kontrol dikonfigurasi untuk pembacaan.

Array

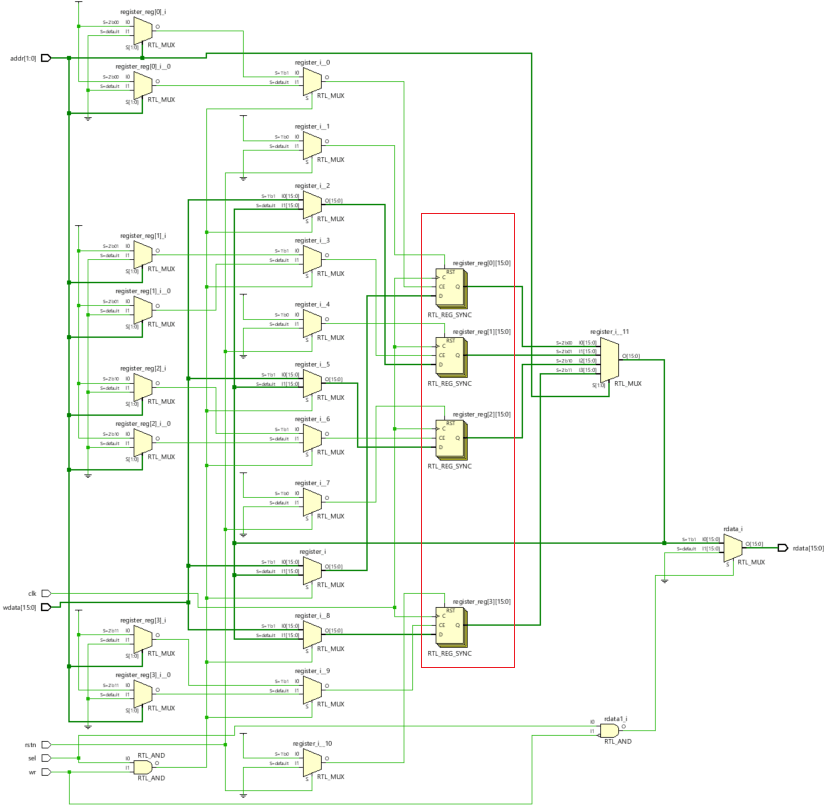

Dalam contoh ini, register adalah array yang memiliki empat lokasi dengan masing-masing memiliki lebar 16-bit. Modul desain menerima sinyal input tambahan yang disebut addr untuk mengakses indeks tertentu dalam larik.

module des ( input clk,

input rstn,

input [1:0] addr,

input wr,

input sel,

input [15:0] wdata,

output [15:0] rdata);

reg [15:0] register [0:3];

integer i;

always @ (posedge clk) begin

if (!rstn) begin

for (i = 0; i < 4; i = i+1) begin

register[i] <= 0;

end

end else begin

if (sel & wr)

register[addr] <= wdata;

else

register[addr] <= register[addr];

end

end

assign rdata = (sel & ~wr) ? register[addr] : 0;

endmodule

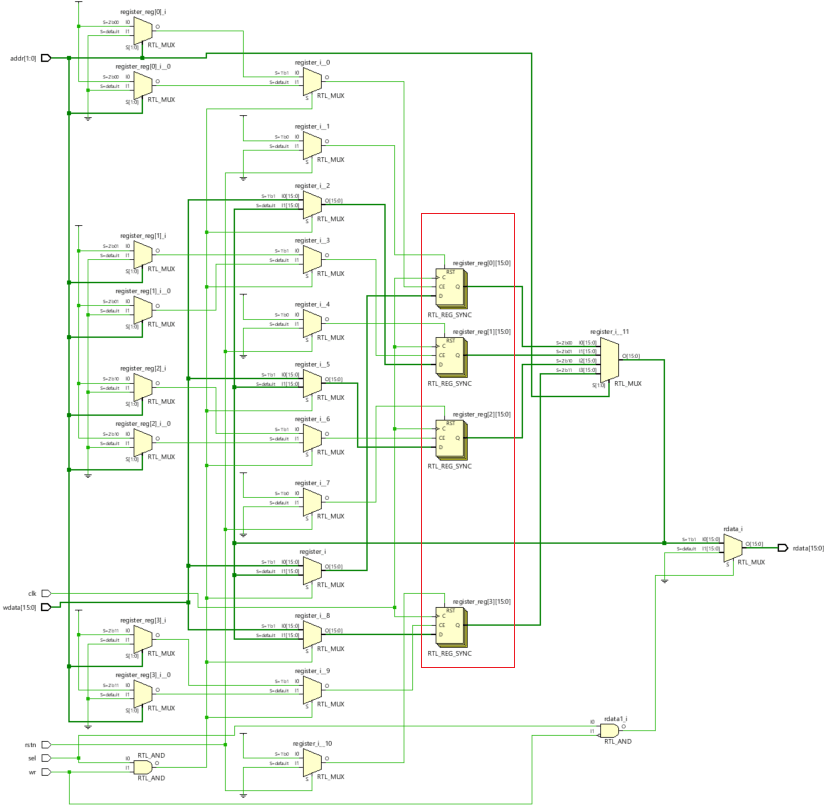

Dapat dilihat dalam skema perangkat keras bahwa setiap indeks array adalah kegagalan 16-bit dan alamat input digunakan untuk mengakses kumpulan kegagalan tertentu.