Verilog

Sebuah module adalah blok kode Verilog yang mengimplementasikan fungsi tertentu. Modul dapat disematkan di dalam modul lain dan modul tingkat yang lebih tinggi dapat berkomunikasi dengan modul tingkat yang lebih rendah menggunakan port input dan outputnya.

Sebuah modul harus diapit dalam module dan endmodule kata kunci. Nama modul harus diberikan tepat setelah module kata kunci dan daftar port opsional dapat dideklarasikan juga. Perhatikan bahwa port yang dideklarasikan dalam daftar deklarasi port tidak dapat dideklarasikan ulang di dalam isi modul.

module <name> ([port_list]);

// Contents of the module

endmodule

// A module can have an empty portlist

module name;

// Contents of the module

endmodule

Semua deklarasi variabel, pernyataan aliran data, fungsi atau tugas, dan instance modul yang lebih rendah jika ada, harus didefinisikan dalam module dan endmodule kata kunci. Mungkin ada beberapa modul dengan nama berbeda dalam file yang sama dan dapat ditentukan dalam urutan apa pun.

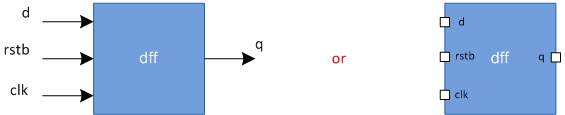

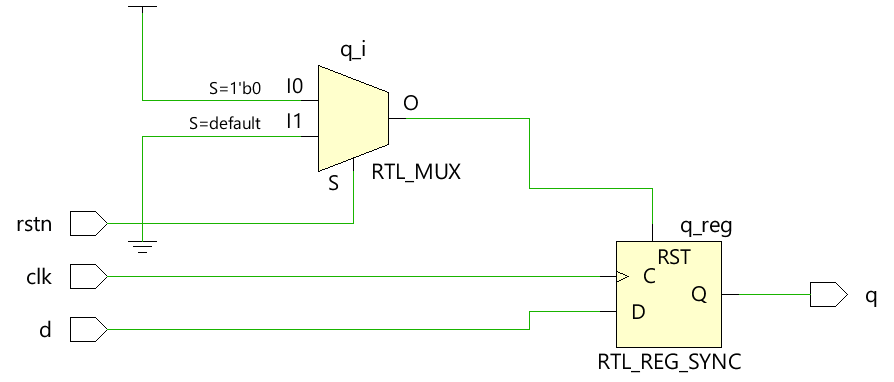

Modul dff mewakili flip flop D yang memiliki tiga port input d, clk, rstn dan satu port output q. Isi modul menjelaskan bagaimana sebuah flip flop D harus berperilaku untuk kombinasi input yang berbeda. Di sini, input d selalu ditetapkan ke output q pada tepi positif jam jika rstn tinggi karena merupakan reset rendah aktif.

// Module called "dff" has 3 inputs and 1 output port

module dff ( input d,

input clk,

input rstn,

output reg q);

// Contents of the module

always @ (posedge clk) begin

if (!rstn)

q <= 0;

else

q <= d;

end

endmodule

Modul ini akan diubah menjadi rangkaian digital berikut selama sintesis.

Perhatikan bahwa Anda tidak boleh memiliki kode apa pun yang ditulis di luar modul !

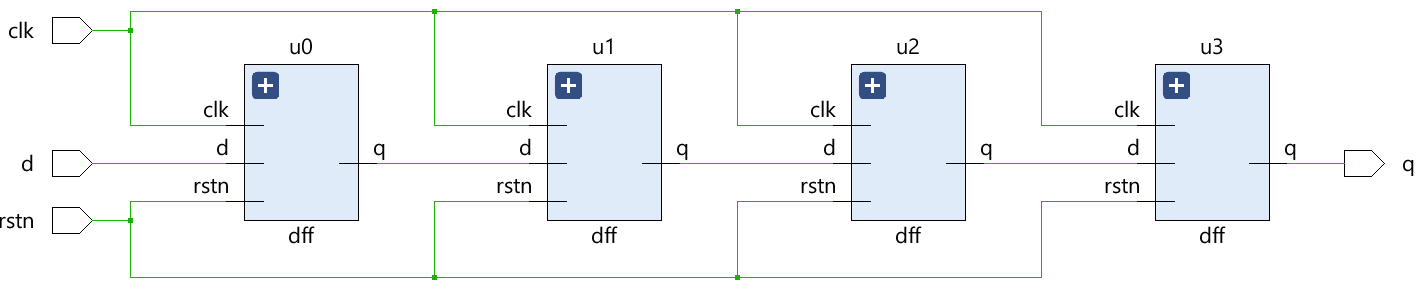

Modul mewakili unit desain yang menerapkan karakteristik perilaku tertentu dan akan diubah menjadi sirkuit digital selama sintesis. Kombinasi input apa pun dapat diberikan ke modul dan itu akan memberikan output yang sesuai. Ini memungkinkan modul yang sama untuk digunakan kembali untuk membentuk modul yang lebih besar yang mengimplementasikan perangkat keras yang lebih kompleks.

Misalnya, DFF yang ditunjukkan di atas dapat dirantai untuk membentuk register geser.

module shift_reg ( input d,

input clk,

input rstn,

output q);

wire [2:0] q_net;

dff u0 (.d(d), .clk(clk), .rstn(rstn), .q(q_net[0]));

dff u1 (.d(q_net[0]), .clk(clk), .rstn(rstn), .q(q_net[1]));

dff u2 (.d(q_net[1]), .clk(clk), .rstn(rstn), .q(q_net[2]));

dff u3 (.d(q_net[2]), .clk(clk), .rstn(rstn), .q(q));

endmodule

Perhatikan bahwa instans dff terhubung bersama dengan kabel seperti yang dijelaskan oleh modul Verilog RTL.

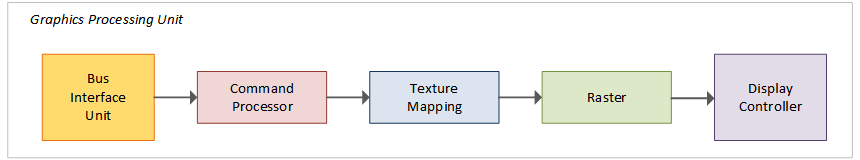

Alih-alih membangun dari blok yang lebih kecil untuk membentuk blok desain yang lebih besar, kebalikannya juga bisa dilakukan. Pertimbangkan pemecahan mesin GPU sederhana menjadi komponen yang lebih kecil sehingga masing-masing dapat direpresentasikan sebagai modul yang mengimplementasikan fitur tertentu. Mesin GPU yang ditunjukkan di bawah ini dapat dibagi menjadi lima sub-blok yang berbeda di mana masing-masing melakukan fungsi tertentu. Unit antarmuka bus mendapatkan data dari luar ke dalam desain, yang diproses oleh unit lain untuk mengekstrak instruksi. Unit lain memproses data yang disediakan oleh unit sebelumnya.

Setiap sub-blok dapat direpresentasikan sebagai module dengan serangkaian sinyal input dan output tertentu untuk komunikasi dengan modul lain dan setiap sub-blok dapat dibagi lagi menjadi blok yang lebih halus sesuai kebutuhan.

Sebuah tingkat atas modul adalah salah satu yang berisi semua modul lainnya. Modul tingkat atas tidak dipakai dalam modul lain.

Misalnya, modul desain biasanya dipakai dalam modul testbench tingkat atas sehingga simulasi dapat dijalankan dengan memberikan stimulus input. Tapi, testbench tidak dipakai dalam modul lain karena merupakan blok yang merangkum segala sesuatu yang lain dan karenanya adalah modul tingkat atas .

Kode desain yang ditunjukkan di bawah ini memiliki modul tingkat atas yang disebut desain. Ini karena berisi semua sub-modul lain yang diperlukan untuk membuat desain lengkap. Submodul dapat memiliki lebih banyak sub-modul bersarang seperti mod3 di dalam mod1 dan mod4 di dalam mod2. Bagaimanapun, semua ini termasuk ke dalam modul tingkat atas ketika mod1 dan mod2 dipakai. Jadi ini membuat desain lengkap dan merupakan modul tingkat atas untuk desain.

//---------------------------------

// Design code

//---------------------------------

module mod3 ( [port_list] );

reg c;

// Design code

endmodule

module mod4 ( [port_list] );

wire a;

// Design code

endmodule

module mod1 ( [port_list] ); // This module called "mod1" contains two instances

wire y;

mod3 mod_inst1 ( ... ); // First instance is of module called "mod3" with name "mod_inst1"

mod3 mod_inst2 ( ... ); // Second instance is also of module "mod3" with name "mod_inst2"

endmodule

module mod2 ( [port_list] ); // This module called "mod2" contains two instances

mod4 mod_inst1 ( ... ); // First instance is of module called "mod4" with name "mod_inst1"

mod4 mod_inst2 ( ... ); // Second instance is also of module "mod4" with name "mod_inst2"

endmodule

// Top-level module

module design ( [port_list]); // From design perspective, this is the top-level module

wire _net;

mod1 mod_inst1 ( ... ); // since it contains all other modules and sub-modules

mod2 mod_inst2 ( ... );

endmodule

Modul testbench berisi stimulus untuk memeriksa fungsionalitas desain dan terutama digunakan untuk verifikasi fungsional menggunakan alat simulasi. Oleh karena itu desain dipakai dan disebut d0 di dalam modul testbench. Dari perspektif simulator, testbench adalah modul tingkat atas.

//-----------------------------------------------------------

// Testbench code

// From simulation perspective, this is the top-level module

// because 'design' is instantiated within this module

//-----------------------------------------------------------

module testbench;

design d0 ( [port_list_connections] );

// Rest of the testbench code

endmodule

Struktur hierarkis terbentuk ketika modul dapat dipakai di dalam satu sama lain, dan karenanya modul tingkat atas disebut root . Karena setiap instansiasi modul yang lebih rendah dalam modul yang diberikan diharuskan memiliki nama pengenal yang berbeda, tidak akan ada ambiguitas dalam mengakses sinyal. Nama hierarki dibuat oleh daftar pengidentifikasi ini yang dipisahkan oleh titik . untuk setiap tingkat hierarki. Sinyal apa pun dapat diakses dalam modul apa pun menggunakan jalur hierarkis ke sinyal tertentu.

// Take the example shown above in top level modules

design.mod_inst1 // Access to module instance mod_inst1

design.mod_inst1.y // Access signal "y" inside mod_inst1

design.mod_inst2.mod_inst2.a // Access signal "a" within mod4 module

testbench.d0._net; // Top level signal _net within design module accessed from testbench

Verilog

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan? Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang

riak pencacah adalah pencacah asinkron di mana semua flop kecuali yang pertama di-clock oleh output dari flop sebelumnya. Desain module dff ( input d, input clk, input rstn, output reg q, output qn); always @ (posedge clk or neg

Desain module ring_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= out[0]; for (int i = 0; i < WIDTH-1; i=i+1) b

Desain module johnson_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= ~out[0]; for (int i = 0; i < WIDTH-1; i=i+1