Verilog

Verilog perlu mewakili bit individu serta kelompok bit. Misalnya, elemen sekuensial bit tunggal adalah flip-flop. Namun elemen sekuensial 16-bit adalah register yang dapat menampung 16 bit. Untuk tujuan ini, Verilog memiliki skalar dan vektor jaring dan variabel.

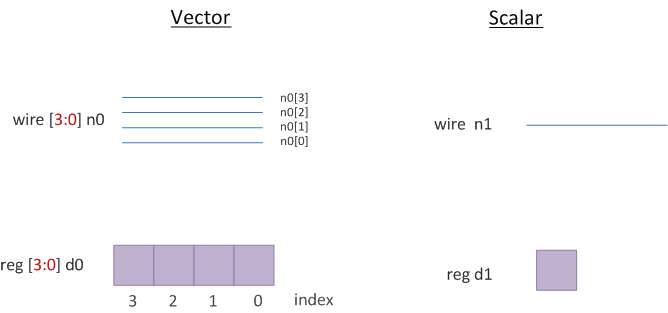

Jaring atau reg deklarasi tanpa spesifikasi rentang dianggap lebar 1-bit dan merupakan skalar . Jika rentang ditentukan, maka net atau reg menjadi entitas multibit yang dikenal sebagai vektor .

wire o_nor; // single bit scalar net

wire [7:0] o_flop; // 8-bit vector net

reg parity; // single bit scalar variable

reg [31:0] addr; // 32 bit vector variable to store address

Rentang memberikan kemampuan untuk menangani bit individu dalam vektor. Bit paling signifikan dari vektor harus ditentukan sebagai nilai tangan kiri dalam rentang sementara bit paling signifikan dari vektor harus ditentukan di sebelah kanan.

wire [msb:lsb] name;

integer my_msb;

wire [15:0] priority; // msb = 15, lsb = 0

wire [my_msb: 2] prior; // illegal

Jaring lebar 16 bit yang disebut prioritas akan dibuat dalam contoh di atas. Perhatikan bahwa msb dan lsb harus berupa ekspresi konstan dan tidak dapat diganti dengan variabel. Tetapi mereka dapat berupa nilai bilangan bulat apa saja - positif, negatif, atau nol; dan lsb nilai bisa lebih besar dari, sama dengan atau kurang dari nilai msb.

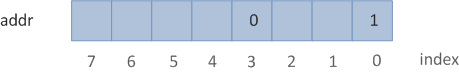

Setiap bit dalam variabel vektor dapat dipilih secara individual dan diberi nilai baru seperti yang ditunjukkan di bawah ini. Ini disebut sebagai pilihan bit . Jika bit-select di luar batas atau bit-select x atau z , maka nilai yang dikembalikan akan menjadi x .

reg [7:0] addr; // 8-bit reg variable [7, 6, 5, 4, 3, 2, 1, 0]

addr [0] = 1; // assign 1 to bit 0 of addr

addr [3] = 0; // assign 0 to bit 3 of addr

addr [8] = 1; // illegal : bit8 does not exist in addr

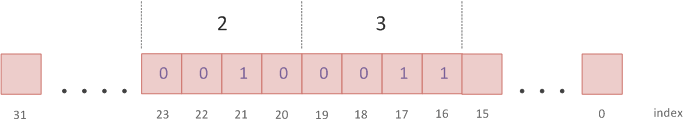

Rentang bit yang berdekatan dapat dipilih dan dikenal sebagai pilihan bagian . Ada dua jenis pemilihan bagian, satu dengan pemilihan bagian yang konstan dan yang lainnya dengan pemilihan bagian yang diindeks.

reg [31:0] addr;

addr [23:16] = 8'h23; // bits 23 to 16 will be replaced by the new value 'h23 -> constant part-select

Memiliki pemilihan bagian variabel memungkinkannya digunakan secara efektif dalam loop untuk memilih bagian vektor. Meskipun bit awal dapat bervariasi, lebarnya harus konstan.

[<start_bit> +: <width>] // part-select increments from start-bit [<start_bit> -: <width>] // part-select decrements from start-bit

module des;

reg [31:0] data;

int i;

initial begin

data = 32'hFACE_CAFE;

for (i = 0; i < 4; i++) begin

$display ("data[8*%0d +: 8] = 0x%0h", i, data[8*i +: 8]);

end

$display ("data[7:0] = 0x%0h", data[7:0]);

$display ("data[15:8] = 0x%0h", data[15:8]);

$display ("data[23:16] = 0x%0h", data[23:16]);

$display ("data[31:24] = 0x%0h", data[31:24]);

end

endmodule

Log Simulasi ncsim> run data[8*0 +: 8] = 0xfe // ~ data [8*0+8 : 8*0] data[8*1 +: 8] = 0xca // ~ data [8*1+8 : 8*1] data[8*2 +: 8] = 0xce // ~ data [8*2+8 : 8*2] data[8*3 +: 8] = 0xfa // ~ data [8*3+8 : 8*3] data[7:0] = 0xfe data[15:8] = 0xca data[23:16] = 0xce data[31:24] = 0xfa ncsim: *W,RNQUIE: Simulation is complete.

module tb;

reg [15:0] data;

initial begin

$display ("data[0:9] = 0x%0h", data[0:9]); // Error : Reversed part-select index expression ordering

end

endmodule

Verilog

Sebuah for loop adalah loop yang paling banyak digunakan dalam perangkat lunak, tetapi terutama digunakan untuk mereplikasi logika perangkat keras di Verilog. Ide di balik for loop adalah untuk mengulangi satu set pernyataan yang diberikan dalam loop selama kondisi yang diberikan benar. Ini sangat m

case pernyataan memeriksa apakah ekspresi yang diberikan cocok dengan salah satu ekspresi lain dalam daftar dan bercabang sesuai. Biasanya digunakan untuk mengimplementasikan multiplexer. Konstruksi if-else mungkin tidak cocok jika ada banyak kondisi yang harus diperiksa dan akan disintesis menjadi

Parameter adalah konstruksi Verilog yang memungkinkan modul untuk digunakan kembali dengan spesifikasi yang berbeda. Misalnya, penambah 4-bit dapat diparameterisasi untuk menerima nilai jumlah bit dan nilai parameter baru dapat diteruskan selama pembuatan modul. Jadi, penambah N-bit bisa menjadi pen

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan? Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang