Pengenalan singkat tentang Bahasa Verilog dan HDL

Pengantar:

Dalam artikel ini, kami akan memperkenalkan Anda ke VHDL dan Verilog. Kami juga akan mempelajari struktur dasar modul Verilog dan mengenal tipe data 'kawat' Verilog dan bentuk vektornya. Kami juga akan memberi tahu Anda perbedaan mendasar antara Verilog dan VHDL.

Apa itu Verilog?

Verilog adalah jenis Bahasa Deskripsi Perangkat Keras (HDL), distandarisasi sebagai IEEE 1364. Verilog paling sering digunakan dalam menggambarkan sirkuit dan sistem elektronik, digunakan dalam desain dan verifikasi sirkuit digital.

Apa itu VHDL?

VHDL juga merupakan jenis Bahasa Deskripsi Perangkat Keras (HDL) yang digunakan dalam otomatisasi desain elektronik untuk menggambarkan perilaku dan struktur sistem elektronik dan sangat cocok sebagai bahasa untuk menggambarkan struktur dan perilaku desain perangkat keras elektronik digital serta sirkuit digital konvensional.

Apakah Saya Membutuhkan Verilog dan VHDL?

Sebelum kita melanjutkan, mari kita bahas apakah kita memerlukan kedua bahasa tersebut? Keduanya adalah alat canggih yang digunakan dalam merancang sirkuit digital yang kompleks, tetapi Anda bebas untuk menguasai salah satu yang ingin Anda gunakan. Namun, Anda harus memiliki pemahaman dasar tentang kedua bahasa tersebut.

Evolusi Verilog

Verilog dirancang pada tahun 1984 di Gateway Design Automation. Pada tahun 1987, VHDL menjadi standar IEEE sementara Verilog berhasil mencapainya pada tahun 1995. Saat ini keduanya merupakan HDL (Hardware Description Languages) yang kuat. Kata 'Verilog' berasal dari kata 'verifikasi' dan 'logika'. Hal ini karena bahasa tersebut pertama kali digunakan sebagai alat simulasi dan verifikasi.

Sekarang kita akan membahas beberapa konsep Verilog.

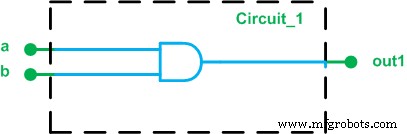

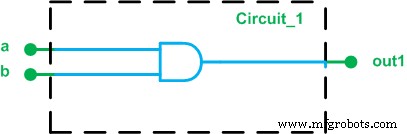

Contoh 1:

Dalam contoh ini, mari kita tulis kode Verilog untuk rangkaian yang ditunjukkan di bawah ini.

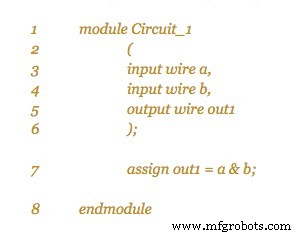

Ada dua input dan satu output ditampilkan dan port berukuran satu bit. Rangkaian menunjukkan fungsi AND dari dua input yang menghasilkan output pada port out1. Deskripsi Verilog dapat ditampilkan sebagai:

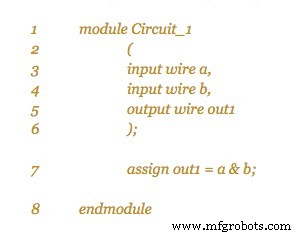

Baris 1 dan 8:

Kata kunci 'modul' dan 'endmodule' digunakan untuk menentukan garis di antara keduanya yang menggambarkan Circuit_1.

Baris 2 hingga 6:

Baris ini menentukan antarmuka 'Circuit_1' dengan lingkungannya. Kata kunci 'input' dan 'output' menunjukkan port input dan output. Setelah ini kata kunci 'kawat' menentukan tipe data Verilog yang mewakili kabel fisik dalam desain. Ada tiga kabel a, b dan out1 di modul kami.

Baris 7:

Baris menggambarkan fungsionalitas AND dari rangkaian dengan operator AND bitwise '&'. Kata kunci ‘menetapkan; digunakan untuk menempatkan a &b pada port output. Ini juga dikenal sebagai penugasan berkelanjutan karena selalu aktif setiap kali ekspresi berubah di sisi kanan, sisi kiri dievaluasi ulang, yaitu outputnya terus diperbarui.

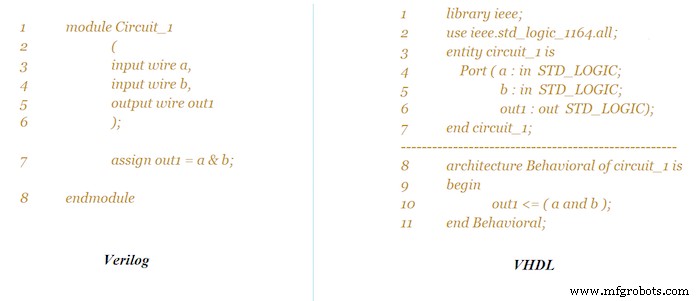

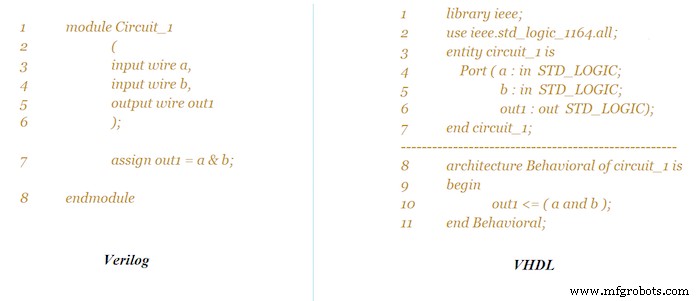

Membandingkan Contoh 1 dengan Kode VHDL:

Gambar di bawah menunjukkan deskripsi Verilog dan VHDL untuk modul Circuit_1.

Dalam VHDL kita harus menyertakan beberapa library yang mendefinisikan tipe data dan operator. Oleh karena itu kode VHDL lebih deskriptif. Namun, dalam beberapa kasus ini menguntungkan seperti dalam pemodelan sistem tingkat yang lebih tinggi.

Sistem Empat Nilai Verilog:

Ada empat nilai yang digunakan dalam tipe data Verilog:

- 0:logika rendah/salah

- 1:logika tinggi/benar

- z:untuk status impedansi tinggi (juga digunakan untuk menjelaskan output buffer tri-status)

- x:nilai tidak diketahui

Jenis data std_logic VHDL dapat mengambil sembilan nilai berbeda, tetapi nilai yang umum digunakan adalah '0', '1', 'Z', dan '-' ('-' menunjukkan nilai yang tidak diketahui).

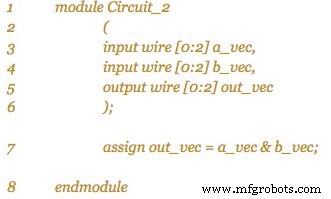

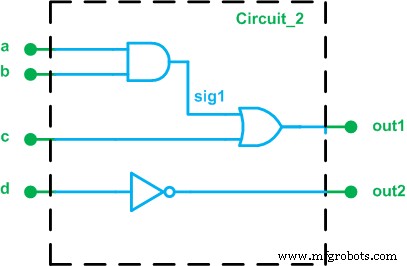

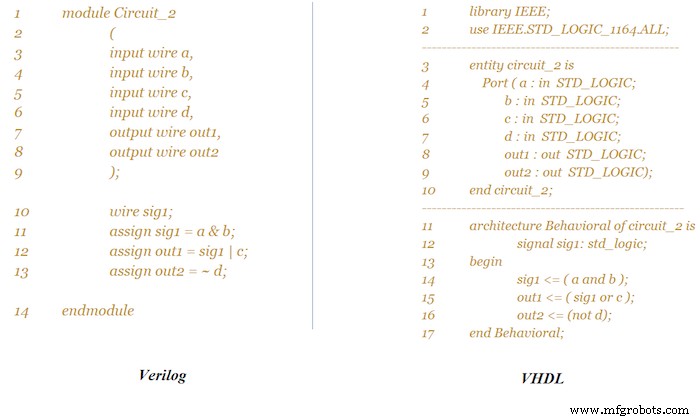

Contoh 2:

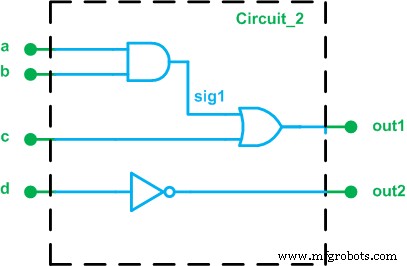

Pada contoh berikutnya, mari kita tulis kode Verilog untuk rangkaian (Circuit_2) yang ditunjukkan pada Gambar di bawah.

Kode Verilog berikut menjelaskan rangkaian yang ditampilkan:

Elemen yang digunakan mirip dengan contoh sebelumnya, namun, sinyal internal didefinisikan pada baris 10. Kata kunci 'kawat' menentukan tipe data koneksi ini. Operator bitwise '~' digunakan untuk NOT dan '|' untuk operasi OR. Operator bitwise '^' digunakan untuk operasi XOR.

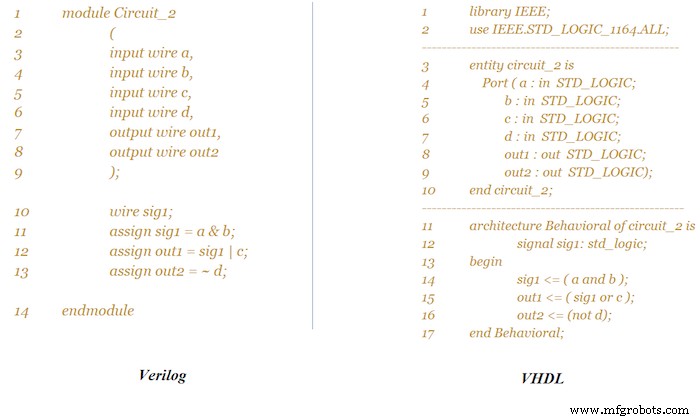

Gambar berikut akan menunjukkan deskripsi Verilog dan VHDL untuk modul Circuit_2 sehingga Anda dapat mengamati perbedaannya.

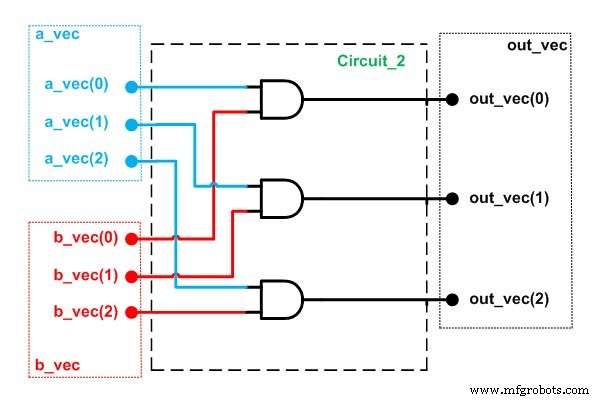

Contoh 3:

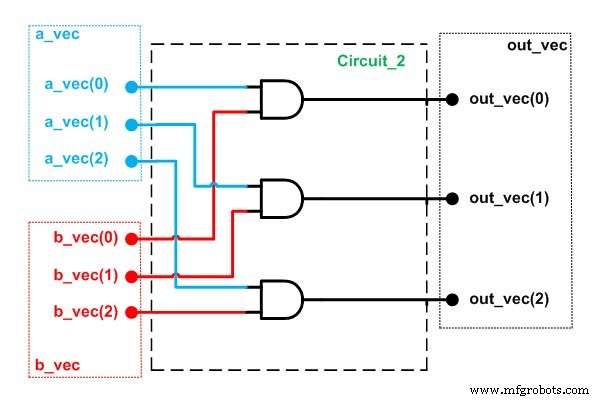

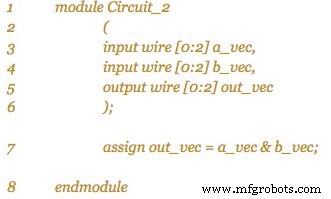

Untuk contoh ketiga dan terakhir, kami akan memberikan kode Verilog untuk skema yang ditunjukkan pada gambar berikut: Anda akan melihat port input merah dan biru digabungkan dengan operator AND. Hasilnya ditunjukkan oleh port output. Kita dapat mengelompokkan sinyal dan memperlakukannya sebagai vektor yang akan membuat kode kita ringkas dan mudah dibaca. Kita dapat menggambarkan rangkaian di atas dengan menggunakan kode Verilog. Kami juga dapat dengan mudah memperluas kode dari Daftar 1 untuk menggambarkan rangkaian ini.

Anda akan melihat port input merah dan biru digabungkan dengan operator AND. Hasilnya ditunjukkan oleh port output. Kita dapat mengelompokkan sinyal dan memperlakukannya sebagai vektor yang akan membuat kode kita ringkas dan mudah dibaca. Kita dapat menggambarkan rangkaian di atas dengan menggunakan kode Verilog. Kami juga dapat dengan mudah memperluas kode dari Daftar 1 untuk menggambarkan rangkaian ini.

Perlu diingat bahwa rentang indeks vektor dapat naik seperti yang ditunjukkan ([0:2]) atau turun ([2:0]). Format menurun biasanya kurang rentan terhadap kesalahan dan dapat digunakan sebagai gantinya.

Anda akan melihat port input merah dan biru digabungkan dengan operator AND. Hasilnya ditunjukkan oleh port output. Kita dapat mengelompokkan sinyal dan memperlakukannya sebagai vektor yang akan membuat kode kita ringkas dan mudah dibaca. Kita dapat menggambarkan rangkaian di atas dengan menggunakan kode Verilog. Kami juga dapat dengan mudah memperluas kode dari Daftar 1 untuk menggambarkan rangkaian ini.

Anda akan melihat port input merah dan biru digabungkan dengan operator AND. Hasilnya ditunjukkan oleh port output. Kita dapat mengelompokkan sinyal dan memperlakukannya sebagai vektor yang akan membuat kode kita ringkas dan mudah dibaca. Kita dapat menggambarkan rangkaian di atas dengan menggunakan kode Verilog. Kami juga dapat dengan mudah memperluas kode dari Daftar 1 untuk menggambarkan rangkaian ini.