VHDL

VHDL adalah akronim yang mengerikan. Itu singkatan dari V HSIC H perangkat keras D deskripsi L bahasa. Akronim di dalam akronim, luar biasa! VHSIC adalah singkatan dari V ery H tinggi S pipis Saya C . terintegrasi irit. Oleh karena itu, VHDL yang diperluas adalah V Sirkuit Terpadu Kecepatan Tinggi H perangkat keras D deskripsi L bahasa. Fiuh itu seteguk. VHDL adalah salah satu dari dua bahasa yang digunakan oleh pendidikan dan bisnis untuk merancang FPGA dan ASIC. Pertama-tama Anda mungkin mendapat manfaat dari pengenalan FPGA dan ASIC jika Anda tidak terbiasa dengan bagian sirkuit yang menarik ini. VHDL dan Verilog adalah dua bahasa yang digunakan desainer digital untuk menggambarkan sirkuit mereka, dan keduanya berbeda dalam desain dibandingkan bahasa perangkat lunak tradisional Anda seperti C dan Java.

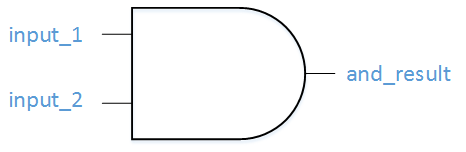

Untuk contoh di bawah ini, kita akan membuat file VHDL yang deskripsikan sebuah Dan Gerbang. Sebagai penyegaran, And Gate yang sederhana memiliki dua input dan satu output. Outputnya sama dengan 1 hanya jika kedua inputnya sama dengan 1. Di bawah ini adalah gambar Gerbang And yang akan kita gambarkan dengan VHDL.

An Dan Gerbang

An Dan Gerbang Mari kita lakukan! Unit dasar VHDL disebut sinyal . Untuk saat ini mari kita asumsikan bahwa sinyal dapat berupa 0 atau 1 (sebenarnya ada kemungkinan lain, tetapi kita akan membahasnya). Berikut adalah beberapa logika dasar VHDL:

signal and_gate : std_logic; and_gate <= input_1 and input_2;

Baris pertama kode mendefinisikan sinyal tipe std_logic dan disebut and_gate. Std_logic adalah tipe yang paling umum digunakan untuk mendefinisikan sinyal, tetapi ada yang lain yang akan Anda pelajari. Kode ini akan menghasilkan sebuah gerbang AND dengan satu output (and_gate) dan 2 input (input_1 dan input_2). Kata kunci "dan" dicadangkan di VHDL. Operator <=dikenal sebagai operator penugasan. Saat Anda menguraikan kode di atas secara lisan, Anda dapat mengucapkan dengan lantang, “Sinyal dan_gerbang MENDAPAT input_1 dan-ed dengan input_2.”

Sekarang Anda mungkin bertanya pada diri sendiri dari mana input_1 dan input_2 berasal. Seperti namanya, mereka adalah input ke file ini, jadi Anda perlu memberi tahu alat tentang mereka. Input dan output ke file didefinisikan dalam entitas . Entitas berisi port yang mendefinisikan semua input dan output ke file. Mari kita buat entitas sederhana:

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

Ini adalah entitas dasar Anda. Ini mendefinisikan entitas yang disebut example_and dan 3 sinyal, 2 input dan 1 output, yang semuanya bertipe std_logic. Satu kata kunci VHDL lain diperlukan untuk melengkapi ini dan itu adalah arsitektur . Arsitektur digunakan untuk menggambarkan fungsionalitas entitas tertentu. Anggap saja makalah tesis:entitas adalah daftar isi dan arsitektur adalah kontennya. Mari kita buat arsitektur untuk entitas ini:

architecture rtl of example_and is signal and_gate : std_logic; begin and_gate <= input_1 and input_2; and_result <= and_gate; end rtl;

Kode di atas mendefinisikan arsitektur yang disebut rtl dari entitas example_and. Semua sinyal yang digunakan oleh arsitektur harus didefinisikan antara kata kunci "adalah" dan "mulai". Logika arsitektur sebenarnya berada di antara kata kunci "mulai" dan "akhir". Anda hampir selesai dengan file ini. Satu hal terakhir yang perlu Anda beri tahu alat adalah perpustakaan mana yang akan digunakan. Pustaka menentukan bagaimana kata kunci tertentu berperilaku dalam file Anda. Untuk saat ini, anggap saja Anda perlu memiliki 2 baris ini di bagian atas file Anda:

library ieee; use ieee.std_logic_1164.all;

Selamat! Anda telah membuat file VHDL pertama Anda. Anda dapat melihat file lengkap di sini:

library ieee;

use ieee.std_logic_1164.all;

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

architecture rtl of example_and is

signal and_gate : std_logic;

begin

and_gate <= input_1 and input_2;

and_result <= and_gate;

end rtl;

Apakah sepertinya Anda harus menulis banyak kode hanya untuk membuat gerbang dan gerbang yang bodoh? Pertama-tama, dan gerbang tidak bodoh. Kedua, Anda benar; VHDL adalah bahasa yang sangat verbose. Biasakan diri Anda dengan kenyataan bahwa melakukan sesuatu yang sangat mudah dalam perangkat lunak akan membawa Anda lebih lama secara signifikan dalam HDL seperti Verilog atau VHDL. Tapi minta saja beberapa perangkat lunak untuk mencoba menghasilkan gambar ke monitor VGA yang menampilkan Game of Life Conway dan lihat kepala mereka berputar dengan takjub! Omong-omong, video itu dibuat dengan VHDL dan FPGA. Anda akan dapat melakukannya segera!

VHDL

Singkatnya, VHDL adalah bahasa komputer yang digunakan untuk merancang sirkuit digital. Saya menggunakan istilah bahasa komputer untuk membedakan VHDL dari bahasa pemrograman lain yang lebih umum seperti Java atau C++. Tetapi apakah VHDL adalah bahasa pemrograman? Ya itu. Ini adalah bahasa pemro

Dipercaya secara luas bahwa plastik tidak terurai, tetapi kenyataannya tidak demikian. Konsep plastik dan polimer biodegradable pertama kali diperkenalkan pada 1980-an. Bakteri Bakteri yang dapat memecah plastik dikembangkan pada awal tahun 1975, ketika tim ilmuwan Jepang menemukan strain Flavobac

Selamat datang di Tutorial Arduino ketujuh dari Seri Tutorial Arduino kami. Dalam tutorial ini kita akan belajar bagaimana menghubungkan Arduino ke Matlab dan bagaimana mereka berkomunikasi menggunakan Port Serial. Kami juga akan membuat contoh di mana kami akan menggunakan Matlab untuk mengontrol A

Pengantar Halo semuanya, saya akan berbicara tentang runtime straton dan lingkungan pemrogramannya di sekitar standar IEC61850. Waktu proses ini mengikuti standar Edisi 2, sebuah protokol yang sedang berevolusi penuh di bidang energi. Di masa lalu, Phoenix Contact telah mengembangkan tump