Verilog

Sinyal tipe wire atau kabel serupa seperti tipe data memerlukan penetapan nilai yang berkelanjutan. Misalnya, pertimbangkan kabel listrik yang digunakan untuk menghubungkan potongan-potongan pada papan tempat memotong roti. Selama baterai +5V diterapkan ke salah satu ujung kabel, komponen yang terhubung ke ujung kabel lainnya akan mendapatkan tegangan yang dibutuhkan.

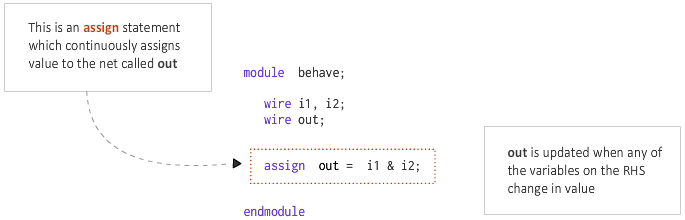

Di Verilog, konsep ini diwujudkan dengan assign pernyataan di mana ada wire atau kabel serupa lainnya seperti tipe data dapat didorong terus menerus dengan nilai. Nilainya bisa berupa konstanta atau ekspresi yang terdiri dari sekelompok sinyal.

Sintaks penugasan dimulai dengan kata kunci assign diikuti dengan nama sinyal yang dapat berupa sinyal tunggal atau gabungan dari jaring sinyal yang berbeda. kekuatan penggerak dan menunda adalah opsional dan sebagian besar digunakan untuk pemodelan aliran data daripada mensintesis menjadi perangkat keras nyata. Ekspresi atau sinyal di sisi kanan dievaluasi dan ditetapkan ke jaring atau ekspresi jaring di sisi kiri.

assign <net_expression> = [drive_strength] [delay] <expression of different signals or constant value>

Nilai penundaan berguna untuk menentukan penundaan untuk gerbang dan digunakan untuk memodelkan perilaku pengaturan waktu dalam perangkat keras nyata karena nilainya menentukan kapan jaring harus ditetapkan dengan nilai yang dievaluasi.

Ada beberapa aturan yang harus diikuti saat menggunakan assign pernyataan:

assign pernyataan juga disebut penugasan berkelanjutan dan selalu aktif

Dalam contoh berikut, jaring yang dipanggil didorong terus menerus oleh ekspresi sinyal. i1 dan i2 dengan logika AND & bentuk ekspresi.

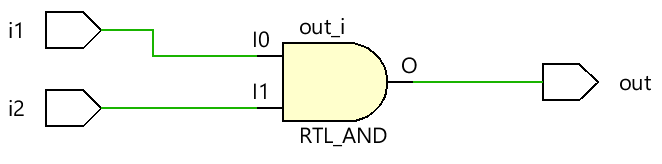

Jika kabel diubah menjadi port dan disintesis, kita akan mendapatkan skema RTL seperti yang ditunjukkan di bawah ini setelah sintesis.

Pernyataan penugasan berkelanjutan dapat digunakan untuk mewakili gerbang kombinasional di Verilog.

Modul yang ditunjukkan di bawah ini mengambil dua input dan menggunakan assign pernyataan untuk menggerakkan output z menggunakan rangkaian part-select dan multiple bit. Perlakukan setiap kasus sebagai satu-satunya kode dalam modul, jika tidak banyak assign pernyataan pada sinyal yang sama pasti akan membuat output menjadi X.

module xyz (input [3:0] x, // x is a 4-bit vector net

input y, // y is a scalar net (1-bit)

output [4:0] z ); // z is a 5-bit vector net

wire [1:0] a;

wire b;

// Assume one of the following assignments are chosen in real design

// If x='hC and y='h1 let us see the value of z

// Case #1: 4-bits of x and 1 bit of y is concatenated to get a 5-bit net

// and is assigned to the 5-bit nets of z. So value of z='b11001 or z='h19

assign z = {x, y};

// Case #2: 4-bits of x and 1 bit of y is concatenated to get a 5-bit net

// and is assigned to selected 3-bits of net z. Remaining 2 bits of z remains

// undriven and will be high-imp. So value of z='bZ001Z

assign z[3:1] = {x, y};

// Case #3: The same statement is used but now bit4 of z is driven with a constant

// value of 1. Now z = 'b1001Z because only bit0 remains undriven

assign z[3:1] = {x, y};

assign z[4] = 1;

// Case #4: Assume bit3 is driven instead, but now there are two drivers for bit3,

// and both are driving the same value of 0. So there should be no contention and

// value of z = 'bZ001Z

assign z[3:1] = {x, y};

assign z[3] = 0;

// Case #5: Assume bit3 is instead driven with value 1, so now there are two drivers

// with different values, where the first line is driven with the value of X which

// at the time is 0 and the second assignment where it is driven with value 1, so

// now it becomes unknown which will win. So z='bZX01Z

assign z[3:1] = {x, y};

assign z[3] = 1;

// Case #6: Partial selection of operands on RHS is also possible and say only 2-bits

// are chosen from x, then z = 'b00001 because z[4:3] will be driven with 0

assign z = {x[1:0], y};

// Case #7: Say we explicitly assign only 3-bits of z and leave remaining unconnected

// then z = 'bZZ001

assign z[2:0] = {x[1:0], y};

// Case #8: Same variable can be used multiple times as well and z = 'b00111

// 3{y} is the same as {y, y, y}

assign z = {3{y}};

// Case #9: LHS can also be concatenated: a is 2-bit vector and b is scalar

// RHS is evaluated to 11001 and LHS is 3-bit wide so first 3 bits from LSB of RHS

// will be assigned to LHS. So a = 'b00 and b ='b1

assign {a, b} = {x, y};

// Case #10: If we reverse order on LHS keeping RHS same, we get a = 'b01 and b='b0

assign {a, b} = {x, y};

endmodule

Adalah ilegal untuk mengemudi atau menetapkan reg ketik variabel dengan assign penyataan. Ini karena reg variabel mampu menyimpan data dan tidak perlu didorong terus menerus. reg sinyal hanya dapat digerakkan dalam blok prosedural seperti initial dan always .

Saat assign pernyataan digunakan untuk menetapkan jaring yang diberikan dengan beberapa nilai, itu disebut eksplisit penugasan. Verilog juga mengizinkan penugasan dilakukan ketika net dideklarasikan dan disebut implisit tugas.

wire [1:0] a;

assign a = x & y; // Explicit assignment

wire [1:0] a = x & y; // Implicit assignment

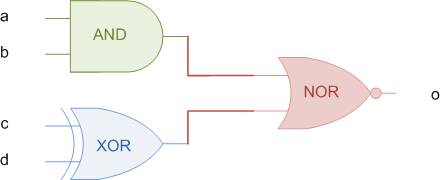

Perhatikan rangkaian digital berikut yang dibuat dari gerbang kombinasional dan kode Verilog yang sesuai.

Logika kombinasional membutuhkan input untuk terus didorong untuk mempertahankan output tidak seperti elemen berurutan seperti sandal jepit di mana nilainya ditangkap dan disimpan di tepi jam. Jadi assign pernyataan sesuai dengan tujuan dengan baik karena output o diperbarui setiap kali salah satu input di sisi kanan berubah.

// This module takes four inputs and performs a boolean

// operation and assigns output to o. The combinational

// logic is realized using assign statement.

module combo ( input a, b, c, d,

output o);

assign o = ~((a & b) | c ^ d);

endmodule

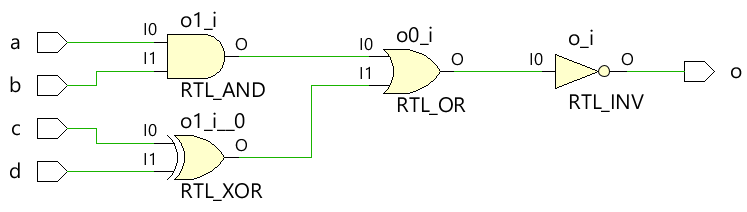

Setelah elaborasi dan sintesis desain, kita dapat melihat rangkaian kombinasional yang akan berperilaku dengan cara yang sama seperti yang dimodelkan oleh assign pernyataan.

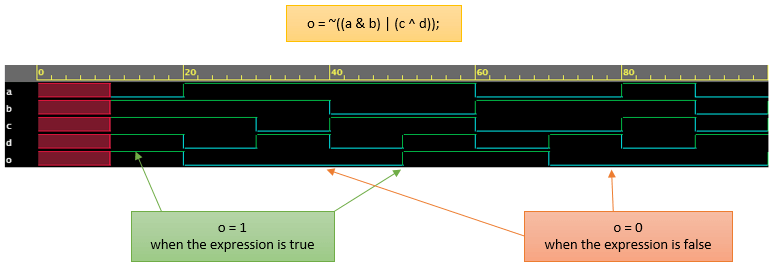

Lihat bahwa sinyal o menjadi 1 setiap kali ekspresi kombinasional pada RHS menjadi benar. Demikian pula o menjadi 0 ketika RHS salah. Output o adalah X dari 0ns hingga 10ns karena inputnya adalah X pada waktu yang sama.

Klik di sini untuk slideshow dengan contoh simulasi !

Verilog

Sebuah for loop adalah loop yang paling banyak digunakan dalam perangkat lunak, tetapi terutama digunakan untuk mereplikasi logika perangkat keras di Verilog. Ide di balik for loop adalah untuk mengulangi satu set pernyataan yang diberikan dalam loop selama kondisi yang diberikan benar. Ini sangat m

case pernyataan memeriksa apakah ekspresi yang diberikan cocok dengan salah satu ekspresi lain dalam daftar dan bercabang sesuai. Biasanya digunakan untuk mengimplementasikan multiplexer. Konstruksi if-else mungkin tidak cocok jika ada banyak kondisi yang harus diperiksa dan akan disintesis menjadi

Parameter adalah konstruksi Verilog yang memungkinkan modul untuk digunakan kembali dengan spesifikasi yang berbeda. Misalnya, penambah 4-bit dapat diparameterisasi untuk menerima nilai jumlah bit dan nilai parameter baru dapat diteruskan selama pembuatan modul. Jadi, penambah N-bit bisa menjadi pen

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan? Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang