Verilog

Jam sangat penting untuk membangun sirkuit digital karena memungkinkan blok yang berbeda sinkron satu sama lain.

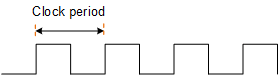

Properti utama dari jam digital adalah frekuensi yang menentukan periode jam , siklus tugasnya dan fase jam dalam kaitannya dengan jam lainnya.

Frekuensi menunjukkan berapa banyak siklus yang dapat ditemukan dalam periode waktu tertentu. Dan karenanya periode jam adalah waktu yang dibutuhkan untuk menyelesaikan 1 siklus.

Jumlah waktu jam tinggi dibandingkan dengan periode waktunya menentukan siklus tugas.

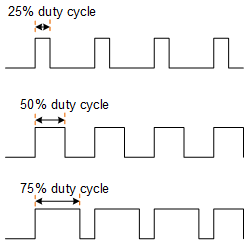

Jika satu siklus jam dapat dilihat sebagai satu lingkaran penuh dengan 360 derajat, jam lain dapat ditempatkan secara relatif di tempat yang berbeda dalam lingkaran yang menempati fase yang berbeda. Misalnya, jam lain dari periode waktu yang sama yang digeser ke kanan sebesar 1/4 periodenya dapat dikatakan memiliki perbedaan fase 90 derajat.

Simulasi diperlukan untuk beroperasi pada skala waktu tertentu yang memiliki presisi terbatas seperti yang ditentukan oleh arahan skala waktu. Oleh karena itu penting bahwa ketepatan skala waktu cukup baik untuk mewakili periode jam. Misalnya, jika frekuensi jam diatur ke 640000 kHz, maka periode jamnya akan menjadi 1,5625 ns di mana ketepatan skala waktu 1ps tidak akan cukup karena ada titik tambahan yang harus diwakili. Oleh karena itu simulasi akan membulatkan digit terakhir agar sesuai dengan presisi skala waktu 3 titik. Ini akan menaikkan periode clock menjadi 1,563 yang sebenarnya mewakili 639795 kHz!

Modul generator jam Verilog berikut memiliki tiga parameter untuk mengubah tiga properti berbeda seperti yang dibahas di atas. Modul memiliki pengaktifan input yang memungkinkan jam dinonaktifkan dan diaktifkan sesuai kebutuhan. Ketika beberapa jam dikendalikan oleh sinyal pengaktifan umum, mereka dapat secara relatif bertahap dengan mudah.

`timescale 1ns/1ps

module clock_gen ( input enable,

output reg clk);

parameter FREQ = 100000; // in kHZ

parameter PHASE = 0; // in degrees

parameter DUTY = 50; // in percentage

real clk_pd = 1.0/(FREQ * 1e3) * 1e9; // convert to ns

real clk_on = DUTY/100.0 * clk_pd;

real clk_off = (100.0 - DUTY)/100.0 * clk_pd;

real quarter = clk_pd/4;

real start_dly = quarter * PHASE/90;

reg start_clk;

initial begin

$display("FREQ = %0d kHz", FREQ);

$display("PHASE = %0d deg", PHASE);

$display("DUTY = %0d %%", DUTY);

$display("PERIOD = %0.3f ns", clk_pd);

$display("CLK_ON = %0.3f ns", clk_on);

$display("CLK_OFF = %0.3f ns", clk_off);

$display("QUARTER = %0.3f ns", quarter);

$display("START_DLY = %0.3f ns", start_dly);

end

// Initialize variables to zero

initial begin

clk <= 0;

start_clk <= 0;

end

// When clock is enabled, delay driving the clock to one in order

// to achieve the phase effect. start_dly is configured to the

// correct delay for the configured phase. When enable is 0,

// allow enough time to complete the current clock period

always @ (posedge enable or negedge enable) begin

if (enable) begin

#(start_dly) start_clk = 1;

end else begin

#(start_dly) start_clk = 0;

end

end

// Achieve duty cycle by a skewed clock on/off time and let this

// run as long as the clocks are turned on.

always @(posedge start_clk) begin

if (start_clk) begin

clk = 1;

while (start_clk) begin

#(clk_on) clk = 0;

#(clk_off) clk = 1;

end

clk = 0;

end

end

endmodule

module tb;

wire clk1;

wire clk2;

wire clk3;

wire clk4;

reg enable;

reg [7:0] dly;

clock_gen u0(enable, clk1);

clock_gen #(.FREQ(200000)) u1(enable, clk2);

clock_gen #(.FREQ(400000)) u2(enable, clk3);

clock_gen #(.FREQ(800000)) u3(enable, clk4);

initial begin

enable <= 0;

for (int i = 0; i < 10; i= i+1) begin

dly = $random;

#(dly) enable <= ~enable;

$display("i=%0d dly=%0d", i, dly);

#50;

end

#50 $finish;

end

endmodule

Log Simulasi

Log Simulasi xcelium> run FREQ = 100000 kHz PHASE = 0 deg DUTY = 50 % PERIOD = 10.000 ns CLK_ON = 5.000 ns CLK_OFF = 5.000 ns QUARTER = 2.500 ns START_DLY = 0.000 ns FREQ = 200000 kHz PHASE = 0 deg DUTY = 50 % PERIOD = 5.000 ns CLK_ON = 2.500 ns CLK_OFF = 2.500 ns QUARTER = 1.250 ns START_DLY = 0.000 ns FREQ = 400000 kHz PHASE = 0 deg DUTY = 50 % PERIOD = 2.500 ns CLK_ON = 1.250 ns CLK_OFF = 1.250 ns QUARTER = 0.625 ns START_DLY = 0.000 ns FREQ = 800000 kHz PHASE = 0 deg DUTY = 50 % PERIOD = 1.250 ns CLK_ON = 0.625 ns CLK_OFF = 0.625 ns QUARTER = 0.312 ns START_DLY = 0.000 ns i=0 dly=36 i=1 dly=129 i=2 dly=9 i=3 dly=99 i=4 dly=13 i=5 dly=141 i=6 dly=101 i=7 dly=18 i=8 dly=1 i=9 dly=13 Simulation complete via $finish(1) at time 1110 NS + 0

module tb;

wire clk1;

wire clk2;

reg enable;

reg [7:0] dly;

clock_gen u0(enable, clk1);

clock_gen #(.FREQ(50000), .PHASE(90)) u1(enable, clk2);

initial begin

enable <= 0;

for (int i = 0; i < 10; i=i+1) begin

dly = $random;

#(dly) enable <= ~enable;

$display("i=%0d dly=%0d", i, dly);

end

#50 $finish;

end

endmodule

Log Simulasi

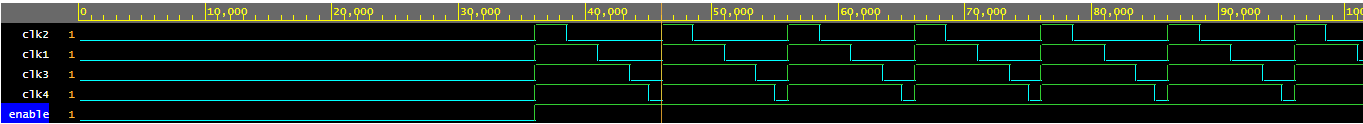

Log Simulasi xcelium> run FREQ = 100000 kHz PHASE = 0 deg DUTY = 50 % PERIOD = 10.000 ns CLK_ON = 5.000 ns CLK_OFF = 5.000 ns QUARTER = 2.500 ns START_DLY = 0.000 ns FREQ = 100000 kHz PHASE = 90 deg DUTY = 50 % PERIOD = 10.000 ns CLK_ON = 5.000 ns CLK_OFF = 5.000 ns QUARTER = 2.500 ns START_DLY = 2.500 ns FREQ = 100000 kHz PHASE = 180 deg DUTY = 50 % PERIOD = 10.000 ns CLK_ON = 5.000 ns CLK_OFF = 5.000 ns QUARTER = 2.500 ns START_DLY = 5.000 ns FREQ = 100000 kHz PHASE = 270 deg DUTY = 50 % PERIOD = 10.000 ns CLK_ON = 5.000 ns CLK_OFF = 5.000 ns QUARTER = 2.500 ns START_DLY = 7.500 ns i=0 dly=36 i=1 dly=129 i=2 dly=9 i=3 dly=99 i=4 dly=13 i=5 dly=141 i=6 dly=101 i=7 dly=18 i=8 dly=1 i=9 dly=13 Simulation complete via $finish(1) at time 1110 NS + 0

module tb;

wire clk1;

wire clk2;

wire clk3;

wire clk4;

reg enable;

reg [7:0] dly;

clock_gen u0(enable, clk1);

clock_gen #(.DUTY(25)) u1(enable, clk2);

clock_gen #(.DUTY(75)) u2(enable, clk3);

clock_gen #(.DUTY(90)) u3(enable, clk4);

initial begin

enable <= 0;

for (int i = 0; i < 10; i= i+1) begin

dly = $random;

#(dly) enable <= ~enable;

$display("i=%0d dly=%0d", i, dly);

#50;

end

#50 $finish;

end

endmodule

Log Simulasi

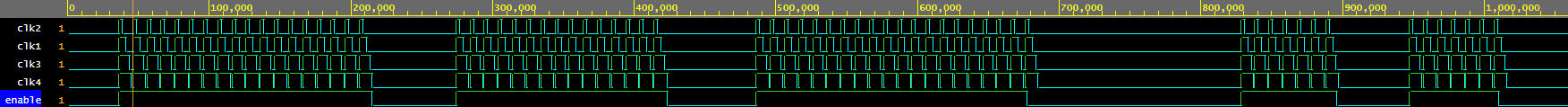

Log Simulasi xcelium> run FREQ = 100000 kHz PHASE = 0 deg DUTY = 50 % PERIOD = 10.000 ns CLK_ON = 5.000 ns CLK_OFF = 5.000 ns QUARTER = 2.500 ns START_DLY = 0.000 ns FREQ = 100000 kHz PHASE = 0 deg DUTY = 25 % PERIOD = 10.000 ns CLK_ON = 2.500 ns CLK_OFF = 7.500 ns QUARTER = 2.500 ns START_DLY = 0.000 ns FREQ = 100000 kHz PHASE = 0 deg DUTY = 75 % PERIOD = 10.000 ns CLK_ON = 7.500 ns CLK_OFF = 2.500 ns QUARTER = 2.500 ns START_DLY = 0.000 ns FREQ = 100000 kHz PHASE = 0 deg DUTY = 90 % PERIOD = 10.000 ns CLK_ON = 9.000 ns CLK_OFF = 1.000 ns QUARTER = 2.500 ns START_DLY = 0.000 ns i=0 dly=36 i=1 dly=129 i=2 dly=9 i=3 dly=99 i=4 dly=13 i=5 dly=141 i=6 dly=101 i=7 dly=18 i=8 dly=1 i=9 dly=13 Simulation complete via $finish(1) at time 1110 NS + 0

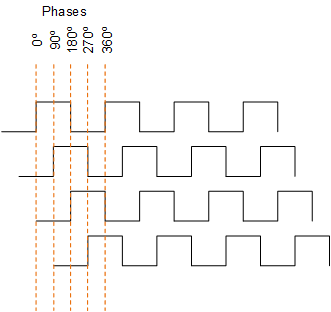

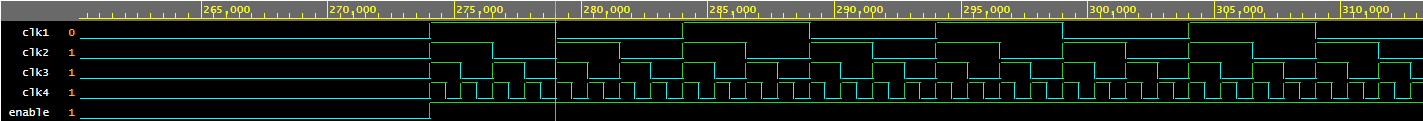

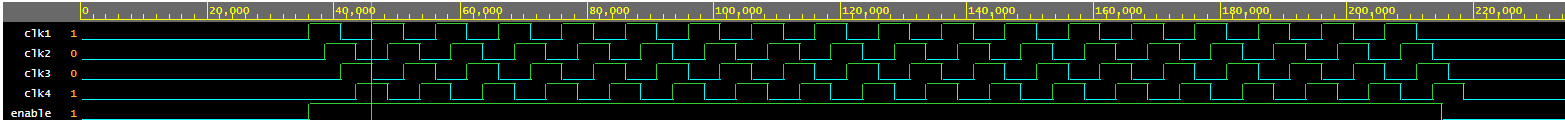

Bentuk gelombang di bawah ini menunjukkan bahwa jam dihentikan saat pengaktifan rendah dan jam dimulai saat pengaktifan disetel tinggi.

Verilog

case pernyataan memeriksa apakah ekspresi yang diberikan cocok dengan salah satu ekspresi lain dalam daftar dan bercabang sesuai. Biasanya digunakan untuk mengimplementasikan multiplexer. Konstruksi if-else mungkin tidak cocok jika ada banyak kondisi yang harus diperiksa dan akan disintesis menjadi

Parameter adalah konstruksi Verilog yang memungkinkan modul untuk digunakan kembali dengan spesifikasi yang berbeda. Misalnya, penambah 4-bit dapat diparameterisasi untuk menerima nilai jumlah bit dan nilai parameter baru dapat diteruskan selama pembuatan modul. Jadi, penambah N-bit bisa menjadi pen

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan? Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang

Desain module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; else