Verilog

Primitif Verilog standar seperti nand dan not mungkin tidak selalu mudah atau cukup untuk mewakili logika yang kompleks. Elemen primitif baru yang disebut UDP atau primitif yang ditentukan pengguna dapat didefinisikan untuk memodelkan logika kombinasional atau sekuensial.

Semua UDP memiliki tepat satu output yang dapat berupa 0, 1 atau X dan tidak pernah Z (tidak didukung). Setiap input yang memiliki nilai Z akan diperlakukan sebagai X.

Primitif yang ditentukan pengguna Verilog dapat ditulis pada level yang sama dengan modul definisi, tetapi tidak pernah di antara module dan endmodule . Mereka dapat memiliki banyak port input tetapi selalu satu port output, dan port dua arah tidak valid. Semua sinyal port harus skalar yang berarti lebarnya harus 1-bit.

Perilaku perangkat keras digambarkan sebagai primitif tabel keadaan yang mencantumkan kemungkinan kombinasi input yang berbeda dan output yang sesuai dalam table dan endtable . Nilai sinyal input dan output ditunjukkan dengan menggunakan simbol berikut.

// Output should always be the first signal in port list

primitive mux (out, sel, a, b);

output out;

input sel, a, b;

table

// sel a b out

0 1 ? : 1;

0 0 ? : 0;

1 ? 0 : 0;

1 ? 1 : 1;

x 0 0 : 0;

x 1 1 : 1;

endtable

endprimitive

Sebuah ? menunjukkan bahwa sinyal dapat berupa 0, 1 atau x dan tidak masalah dalam menentukan keluaran akhir.

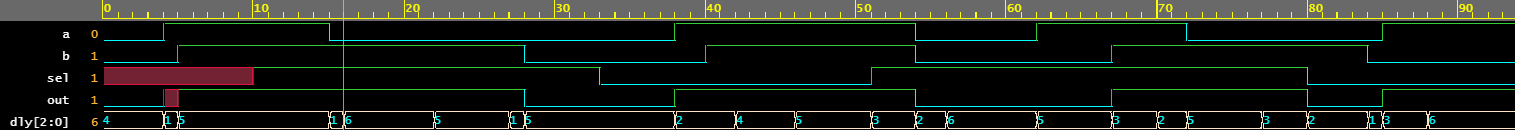

Ditampilkan di bawah ini adalah modul testbench yang memberi contoh UDP dan menerapkan rangsangan input ke dalamnya.

module tb;

reg sel, a, b;

reg [2:0] dly;

wire out;

integer i;

// Instantiate the UDP - note that UDPs cannot

// be instantiated with port name connection

mux u_mux ( out, sel, a, b);

initial begin

a <= 0;

b <= 0;

$monitor("[T=%0t] a=%0b b=%0b sel=%0b out=%0b", $time, a, b, sel, out);

// Drive a, b, and sel after different random delays

for (i = 0; i < 10; i = i + 1) begin

dly = $random;

#(dly) a <= $random;

dly = $random;

#(dly) b <= $random;

dly = $random;

#(dly) sel <= $random;

end

end

endmodule

Log Simulasi

Log Simulasi xcelium> run [T=0] a=0 b=0 sel=x out=0 [T=4] a=1 b=0 sel=x out=x [T=5] a=1 b=1 sel=x out=1 [T=10] a=1 b=1 sel=1 out=1 [T=15] a=0 b=1 sel=1 out=1 [T=28] a=0 b=0 sel=1 out=0 [T=33] a=0 b=0 sel=0 out=0 [T=38] a=1 b=0 sel=0 out=1 [T=40] a=1 b=1 sel=0 out=1 [T=51] a=1 b=1 sel=1 out=1 [T=54] a=0 b=0 sel=1 out=0 [T=62] a=1 b=0 sel=1 out=0 [T=67] a=1 b=1 sel=1 out=1 [T=72] a=0 b=1 sel=1 out=1 [T=80] a=0 b=1 sel=0 out=0 [T=84] a=0 b=0 sel=0 out=0 [T=85] a=1 b=0 sel=0 out=1 xmsim: *W,RNQUIE: Simulation is complete.

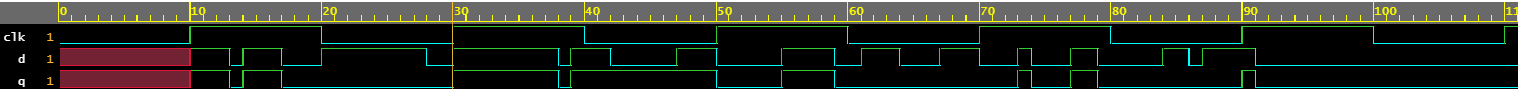

Logika sekuensial dapat berupa level-sensitif atau tepi-sensitif dan karenanya ada dua jenis UDP sekuensial. Port keluaran juga harus dideklarasikan sebagai reg ketik dalam definisi UDP dan dapat diinisialisasi secara opsional dalam initial pernyataan.

UDP berurutan memiliki bidang tambahan di antara bidang input dan output yang dibatasi oleh : yang mewakili keadaan saat ini.

primitive d_latch (q, clk, d);

output q;

input clk, d;

reg q;

table

// clk d q q+

1 1 : ? : 1;

1 0 : ? : 0;

0 ? : ? : -;

endtable

endprimitive

Pada tabel di atas, tanda hubung - pada baris terakhir tabel menunjukkan tidak ada perubahan nilai untuk q+.

module tb;

reg clk, d;

reg [1:0] dly;

wire q;

integer i;

d_latch u_latch (q, clk, d);

always #10 clk = ~clk;

initial begin

clk = 0;

$monitor ("[T=%0t] clk=%0b d=%0b q=%0b", $time, clk, d, q);

#10; // To see the effect of X

for (i = 0; i < 50; i = i+1) begin

dly = $random;

#(dly) d <= $random;

end

#20 $finish;

end

endmodule

Log Simulasi

Log Simulasi xcelium> run [T=0] clk=0 d=x q=x [T=10] clk=1 d=1 q=1 [T=13] clk=1 d=0 q=0 [T=14] clk=1 d=1 q=1 [T=17] clk=1 d=0 q=0 [T=20] clk=0 d=1 q=0 [T=28] clk=0 d=0 q=0 [T=30] clk=1 d=1 q=1 [T=38] clk=1 d=0 q=0 [T=39] clk=1 d=1 q=1 [T=40] clk=0 d=1 q=1 [T=42] clk=0 d=0 q=1 [T=47] clk=0 d=1 q=1 [T=50] clk=1 d=0 q=0 [T=55] clk=1 d=1 q=1 [T=59] clk=1 d=0 q=0 [T=60] clk=0 d=0 q=0 [T=61] clk=0 d=1 q=0 [T=64] clk=0 d=0 q=0 [T=67] clk=0 d=1 q=0 [T=70] clk=1 d=0 q=0 [T=73] clk=1 d=1 q=1 [T=74] clk=1 d=0 q=0 [T=77] clk=1 d=1 q=1 [T=79] clk=1 d=0 q=0 [T=80] clk=0 d=0 q=0 [T=84] clk=0 d=1 q=0 [T=86] clk=0 d=0 q=0 [T=87] clk=0 d=1 q=0 [T=90] clk=1 d=1 q=1 [T=91] clk=1 d=0 q=0 [T=100] clk=0 d=0 q=0 [T=110] clk=1 d=0 q=0 Simulation complete via $finish(1) at time 111 NS + 0

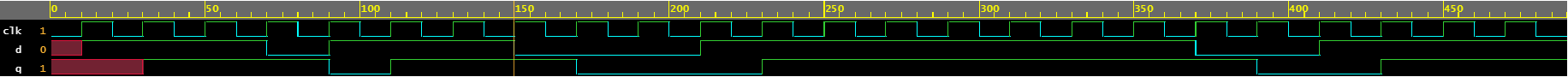

Flip-flop D dimodelkan sebagai primitif yang ditentukan pengguna Verilog dalam contoh yang ditunjukkan di bawah ini. Perhatikan bahwa tepi naik jam ditentukan oleh 01 atau 0?

primitive d_flop (q, clk, d);

output q;

input clk, d;

reg q;

table

// clk d q q+

// obtain output on rising edge of clk

(01) 0 : ? : 0;

(01) 1 : ? : 1;

(0?) 1 : 1 : 1;

(0?) 0 : 0 : 0;

// ignore negative edge of clk

(?0) ? : ? : -;

// ignore data changes on steady clk

? (??): ? : -;

endtable

endprimitive

Di testbench, UDP diinstansiasi dan digerakkan dengan nilai input d acak setelah jumlah jam acak.

module tb;

reg clk, d;

reg [1:0] dly;

wire q;

integer i;

d_flop u_flop (q, clk, d);

always #10 clk = ~clk;

initial begin

clk = 0;

$monitor ("[T=%0t] clk=%0b d=%0b q=%0b", $time, clk, d, q);

#10; // To see the effect of X

for (i = 0; i < 20; i = i+1) begin

dly = $random;

repeat(dly) @(posedge clk);

d <= $random;

end

#20 $finish;

end

endmodule

Dapat dilihat dari gambar bahwa keluaran q mengikuti masukan d setelah penundaan 1 jam yang merupakan perilaku yang diinginkan untuk flip-flop D.

Log Simulasi

Log Simulasi xcelium> run [T=0] clk=0 d=x q=x [T=10] clk=1 d=1 q=x [T=20] clk=0 d=1 q=x [T=30] clk=1 d=1 q=1 [T=40] clk=0 d=1 q=1 [T=50] clk=1 d=1 q=1 [T=60] clk=0 d=1 q=1 [T=70] clk=1 d=0 q=1 [T=80] clk=0 d=0 q=1 [T=90] clk=1 d=1 q=0 [T=100] clk=0 d=1 q=0 [T=110] clk=1 d=1 q=1 [T=120] clk=0 d=1 q=1 [T=130] clk=1 d=1 q=1 [T=140] clk=0 d=1 q=1 [T=150] clk=1 d=0 q=1 [T=160] clk=0 d=0 q=1 [T=170] clk=1 d=0 q=0 [T=180] clk=0 d=0 q=0 [T=190] clk=1 d=0 q=0 [T=200] clk=0 d=0 q=0 [T=210] clk=1 d=1 q=0 [T=220] clk=0 d=1 q=0 [T=230] clk=1 d=1 q=1 [T=240] clk=0 d=1 q=1 [T=250] clk=1 d=1 q=1 [T=260] clk=0 d=1 q=1 [T=270] clk=1 d=1 q=1 [T=280] clk=0 d=1 q=1 [T=290] clk=1 d=1 q=1 [T=300] clk=0 d=1 q=1 [T=310] clk=1 d=1 q=1 [T=320] clk=0 d=1 q=1 [T=330] clk=1 d=1 q=1 [T=340] clk=0 d=1 q=1 [T=350] clk=1 d=1 q=1 [T=360] clk=0 d=1 q=1 [T=370] clk=1 d=0 q=1 [T=380] clk=0 d=0 q=1 [T=390] clk=1 d=0 q=0 [T=400] clk=0 d=0 q=0 [T=410] clk=1 d=1 q=0 [T=420] clk=0 d=1 q=0 [T=430] clk=1 d=1 q=1 [T=440] clk=0 d=1 q=1 [T=450] clk=1 d=1 q=1 [T=460] clk=0 d=1 q=1 [T=470] clk=1 d=1 q=1 [T=480] clk=0 d=1 q=1 Simulation complete via $finish(1) at time 490 NS + 0

Verilog

Sebuah for loop adalah loop yang paling banyak digunakan dalam perangkat lunak, tetapi terutama digunakan untuk mereplikasi logika perangkat keras di Verilog. Ide di balik for loop adalah untuk mengulangi satu set pernyataan yang diberikan dalam loop selama kondisi yang diberikan benar. Ini sangat m

case pernyataan memeriksa apakah ekspresi yang diberikan cocok dengan salah satu ekspresi lain dalam daftar dan bercabang sesuai. Biasanya digunakan untuk mengimplementasikan multiplexer. Konstruksi if-else mungkin tidak cocok jika ada banyak kondisi yang harus diperiksa dan akan disintesis menjadi

Parameter adalah konstruksi Verilog yang memungkinkan modul untuk digunakan kembali dengan spesifikasi yang berbeda. Misalnya, penambah 4-bit dapat diparameterisasi untuk menerima nilai jumlah bit dan nilai parameter baru dapat diteruskan selama pembuatan modul. Jadi, penambah N-bit bisa menjadi pen

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan? Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang