Verilog

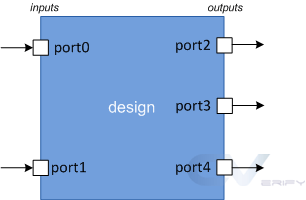

Port adalah seperangkat sinyal yang bertindak sebagai input dan output ke modul tertentu dan merupakan cara utama untuk berkomunikasi dengannya. Pikirkan modul sebagai chip buatan yang ditempatkan pada PCB dan menjadi sangat jelas bahwa satu-satunya cara untuk berkomunikasi dengan chip adalah melalui pinnya. Port seperti pin dan digunakan oleh desain untuk mengirim dan menerima sinyal dari dunia luar.

| Port | Deskripsi |

|---|---|

| Masukan | Modul desain hanya dapat menerima nilai dari luar menggunakan input port |

| Keluaran | Modul desain hanya dapat mengirim nilai ke luar menggunakan output port |

| Keluar | Modul desain dapat mengirim atau menerima nilai menggunakan inout port |

Port secara default dianggap sebagai jaring dengan tipe wire .

Port dideklarasikan sebagai inout dapat bertindak sebagai input dan output.

input [net_type] [range] list_of_names; // Input port

inout [net_type] [range] list_of_names; // Input & Output port

output [net_type] [range] list_of_names; // Output port driven by a wire

output [var_type] [range] list_of_names; // Output port driven by a variable

Pada kode di bawah ini, ada tiga input port, satu output port dan satu inout pelabuhan.

module my_design ( input wire clk,

input en,

input rw,

inout [15:0] data,

output int );

// Design behavior as Verilog code

endmodule

Adalah ilegal untuk menggunakan nama yang sama untuk beberapa port.

input aport; // First declaration - valid

input aport; // Error - already declared

output aport; // Error - already declared

signed atribut dapat dilampirkan ke deklarasi port atau deklarasi net/reg atau keduanya. Jaring implisit secara default tidak ditandatangani .

module ( input a,

b,

output c);

// ports a, b, and c are by default unsigned

endmodule

Jika deklarasi net/reg memiliki signed atribut, maka yang lain juga harus dianggap ditandatangani.

module ( input signed a, b,

output c);

wire a, b; // a, b are signed from port declaration

reg signed c; // c is signed from reg declaration

endmodule

Verilog telah mengalami beberapa revisi dan versi IEEE asli pada tahun 1995 memiliki cara berikut untuk deklarasi port. Di sini, deklarasi modul harus terlebih dahulu mencantumkan nama port di dalam tanda kurung dan kemudian arah port yang ditentukan kemudian di dalam badan modul.

module test (a, b, c);

input [7:0] a; // inputs "a" and "b" are wires

input [7:0] b;

output [7:0] c; // output "c" by default is a wire

// Still, you can declare them again as wires to avoid confusion

wire [7:0] a;

wire [7:0] b;

wire [7:0] c;

endmodule

module test (a, b, c);

input [7:0] a, b;

output [7:0] c; // By default c is of type wire

// port "c" is changed to a reg type

reg [7:0] c;

endmodule

Penamaan port gaya ANSI-C diperkenalkan pada tahun 2001 dan memungkinkan jenisnya ditentukan di dalam daftar port.

module test ( input [7:0] a,

b, // "b" is considered an 8-bit input

output [7:0] c);

// Design content

endmodule

module test ( input wire [7:0] a,

input wire [7:0] b,

output reg [7:0] c);

// Design content

endmodule

Jika deklarasi port menyertakan tipe net atau variabel, maka port tersebut dianggap sepenuhnya dideklarasikan. Adalah ilegal untuk mendeklarasikan ulang port yang sama dalam deklarasi tipe net atau variabel.

module test ( input [7:0] a, // a, e are implicitly declared of type wire

output reg [7:0] e );

wire signed [7:0] a; // illegal - declaration of a is already complete -> simulator dependent

wire [7:0] e; // illegal - declaration of e is already complete

// Rest of the design code

endmodule

Jika deklarasi port tidak menyertakan tipe net atau variabel, maka port dapat dideklarasikan kembali dalam deklarasi tipe net atau variabel.

module test ( input [7:0] a,

output [7:0] e);

reg [7:0] e; // Okay - net_type was not declared before

// Rest of the design code

endmodule

Verilog

Parameter adalah konstruksi Verilog yang memungkinkan modul untuk digunakan kembali dengan spesifikasi yang berbeda. Misalnya, penambah 4-bit dapat diparameterisasi untuk menerima nilai jumlah bit dan nilai parameter baru dapat diteruskan selama pembuatan modul. Jadi, penambah N-bit bisa menjadi pen

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan? Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang

Apa itu mux atau multiplexer? Multiplexer atau mux singkatnya, adalah elemen digital yang mentransfer data dari salah satu input N ke output berdasarkan sinyal pilih. Kasus yang ditunjukkan di bawah ini adalah ketika N sama dengan 4. Misalnya, multiplexer 4 bit akan memiliki N input masing-masing 4

Desain module single_port_sync_ram # (parameter ADDR_WIDTH = 4, parameter DATA_WIDTH = 32, parameter DEPTH = 16 ) ( input clk, input [ADDR_WIDTH-1:0] addr, inout [DATA_WIDTH-1:0] data, input cs, input we, input oe ); re