Verilog

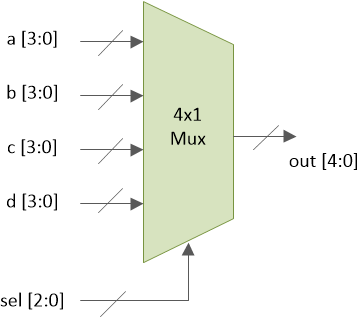

Multiplexer atau mux singkatnya, adalah elemen digital yang mentransfer data dari salah satu input N ke output berdasarkan sinyal pilih. Kasus yang ditunjukkan di bawah ini adalah ketika N sama dengan 4. Misalnya, multiplexer 4 bit akan memiliki N input masing-masing 4 bit di mana setiap input dapat ditransfer ke output dengan menggunakan sinyal pilih.

sel adalah input 2-bit dan dapat memiliki empat nilai. Setiap nilai pada baris pilih akan memungkinkan salah satu input dikirim ke pin output.

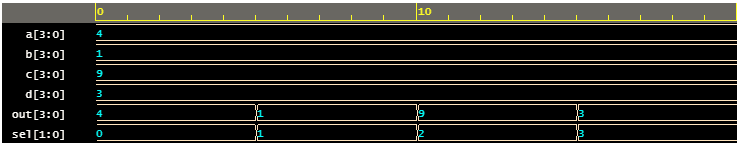

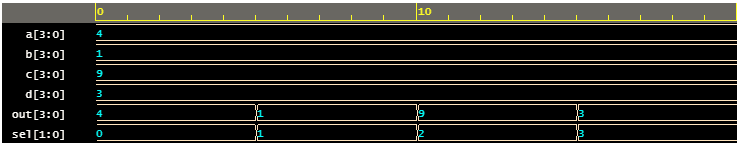

sel a b c d out 0 3 7 1 9 3 1 3 7 1 9 7 2 3 7 1 9 1 3 3 7 1 9 9

Multiplexer 4x1 dapat diimplementasikan dalam berbagai cara dan di sini Anda akan melihat dua cara yang paling umum:

assign pernyataancase pernyataanassign pernyataan

module mux_4to1_assign ( input [3:0] a, // 4-bit input called a

input [3:0] b, // 4-bit input called b

input [3:0] c, // 4-bit input called c

input [3:0] d, // 4-bit input called d

input [1:0] sel, // input sel used to select between a,b,c,d

output [3:0] out); // 4-bit output based on input sel

// When sel[1] is 0, (sel[0]? b:a) is selected and when sel[1] is 1, (sel[0] ? d:c) is taken

// When sel[0] is 0, a is sent to output, else b and when sel[0] is 0, c is sent to output, else d

assign out = sel[1] ? (sel[0] ? d : c) : (sel[0] ? b : a);

endmodule

Modul bernama mux_4x1_assign memiliki empat input data 4-bit, satu input pilih 2-bit dan satu output data 4-bit. Multiplexer akan memilih a , b, c, atau d berdasarkan sel sinyal yang dipilih menggunakan assign pernyataan.

case pernyataan

Perhatikan bahwa sinyal keluar dideklarasikan sebagai reg ketik karena digunakan dalam prosedur blokir seperti always .

module mux_4to1_case ( input [3:0] a, // 4-bit input called a

input [3:0] b, // 4-bit input called b

input [3:0] c, // 4-bit input called c

input [3:0] d, // 4-bit input called d

input [1:0] sel, // input sel used to select between a,b,c,d

output reg [3:0] out); // 4-bit output based on input sel

// This always block gets executed whenever a/b/c/d/sel changes value

// When that happens, based on value in sel, output is assigned to either a/b/c/d

always @ (a or b or c or d or sel) begin

case (sel)

2'b00 : out <= a;

2'b01 : out <= b;

2'b10 : out <= c;

2'b11 : out <= d;

endcase

end

endmodule

Modul bernama mux_4x1_case memiliki empat input data 4-bit, satu input pilih 2-bit dan satu output data 4-bit. Multiplexer akan memilih a , b, c, atau d berdasarkan sel sinyal yang dipilih menggunakan case pernyataan.

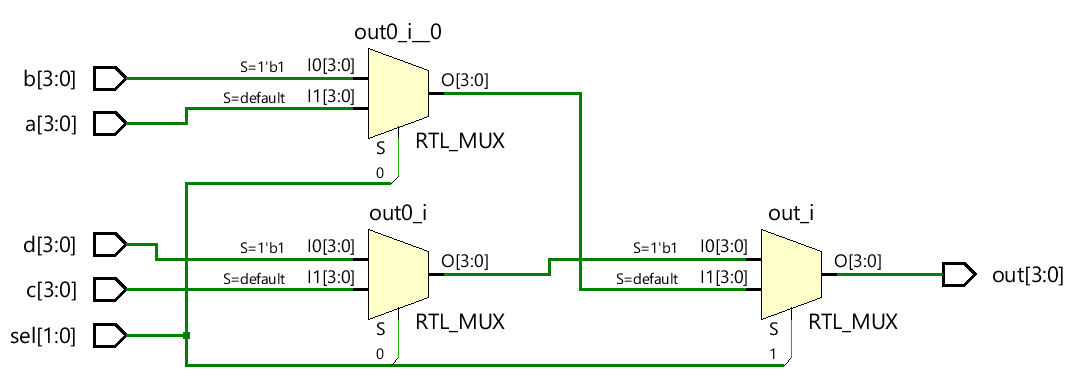

Kedua jenis model multiplexer disintesis ke dalam perangkat keras yang sama seperti yang ditunjukkan pada gambar di bawah ini.

module tb_4to1_mux;

// Declare internal reg variables to drive design inputs

// Declare wire signals to collect design output

// Declare other internal variables used in testbench

reg [3:0] a;

reg [3:0] b;

reg [3:0] c;

reg [3:0] d;

wire [3:0] out;

reg [1:0] sel;

integer i;

// Instantiate one of the designs, in this case, we have used the design with case statement

// Connect testbench variables declared above with those in the design

mux_4to1_case mux0 ( .a (a),

.b (b),

.c (c),

.d (d),

.sel (sel),

.out (out));

// This initial block is the stimulus

initial begin

// Launch a monitor in background to display values to log whenever a/b/c/d/sel/out changes

$monitor ("[%0t] sel=0x%0h a=0x%0h b=0x%0h c=0x%0h d=0x%0h out=0x%0h", $time, sel, a, b, c, d, out);

// 1. At time 0, drive random values to a/b/c/d and keep sel = 0

sel <= 0;

a <= $random;

b <= $random;

c <= $random;

d <= $random;

// 2. Change the value of sel after every 5ns

for (i = 1; i < 4; i=i+1) begin

#5 sel <= i;

end

// 3. After Step2 is over, wait for 5ns and finish simulation

#5 $finish;

end

endmodule

Log Simulasi ncsim> run [0] sel=0x0 a=0x4 b=0x1 c=0x9 d=0x3 out=0x4 [5] sel=0x1 a=0x4 b=0x1 c=0x9 d=0x3 out=0x1 [10] sel=0x2 a=0x4 b=0x1 c=0x9 d=0x3 out=0x9 [15] sel=0x3 a=0x4 b=0x1 c=0x9 d=0x3 out=0x3 Simulation complete via $finish(1) at time 20 NS + 0

Verilog

case pernyataan memeriksa apakah ekspresi yang diberikan cocok dengan salah satu ekspresi lain dalam daftar dan bercabang sesuai. Biasanya digunakan untuk mengimplementasikan multiplexer. Konstruksi if-else mungkin tidak cocok jika ada banyak kondisi yang harus diperiksa dan akan disintesis menjadi

Parameter adalah konstruksi Verilog yang memungkinkan modul untuk digunakan kembali dengan spesifikasi yang berbeda. Misalnya, penambah 4-bit dapat diparameterisasi untuk menerima nilai jumlah bit dan nilai parameter baru dapat diteruskan selama pembuatan modul. Jadi, penambah N-bit bisa menjadi pen

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan? Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang

Apa itu mux atau multiplexer? Multiplexer atau mux singkatnya, adalah elemen digital yang mentransfer data dari salah satu input N ke output berdasarkan sinyal pilih. Kasus yang ditunjukkan di bawah ini adalah ketika N sama dengan 4. Misalnya, multiplexer 4 bit akan memiliki N input masing-masing 4