Konektor dan Antarmuka JTAG

Pelajari tentang antarmuka dan konektor yang digunakan untuk mengimplementasikan JTAG.

Dalam artikel sebelumnya, kami telah melihat standar JTAG asli, IEEE 1149.1. Ini termasuk port akses uji JTAG (TAP), yang memungkinkan pengguna memanipulasi mesin status untuk mengakses internal perangkat dan menjalankan pengujian pemindaian batas.

Tapi sementara informasi ini penting untuk memahami JTAG, juga perlu untuk memahami sisi fisik, termasuk konektor dan pinout, dan antarmuka JTAG komersial yang tersedia di pasar. Dalam artikel ini, kita akan memperbaiki situasi, mengambil pendekatan yang kurang teoretis untuk JTAG secara keseluruhan.

Konektor JTAG

Tidak ada konektor standar untuk JTAG. Lebih sering daripada tidak, "konektor JTAG" adalah header pria standar, seperti header 0,1" atau header pitch yang lebih halus. Seperti yang telah kita lihat, hanya ada empat (atau lima) pin yang diperlukan untuk mengoperasikan JTAG TAP. Namun, perangkat yang digunakan untuk 'berkomunikasi' dengan TAP—disebut antarmuka JTAG— juga membutuhkan koneksi daya dan ground, dan desainer dapat menyertakan koneksi lain pada header JTAG jika diinginkan.

Jadi, jika diberi papan, bagaimana seharusnya seorang desainer menyediakan akses JTAG? Dan, mengingat papan baru, di mana Anda harus mencari untuk menemukan konektor JTAG?

Meskipun tidak ada satu header standar untuk antarmuka JTAG, beberapa jenis header telah menjadi lebih atau kurang standar di antara produsen. Ini termasuk ARM JTAG 20, ARM JTAG 14, TI JTAG 14, STDC14 dari STMicroelectronics, header 16-pin OCDS [pdf] dari Infineon, CoreSight 10, CoreSight 20, MIPI 34, dan Mictor 38 Segger mendefinisikan konektor J-Link dan J-Trace mereka hampir identik dengan ARM JTAG 20.

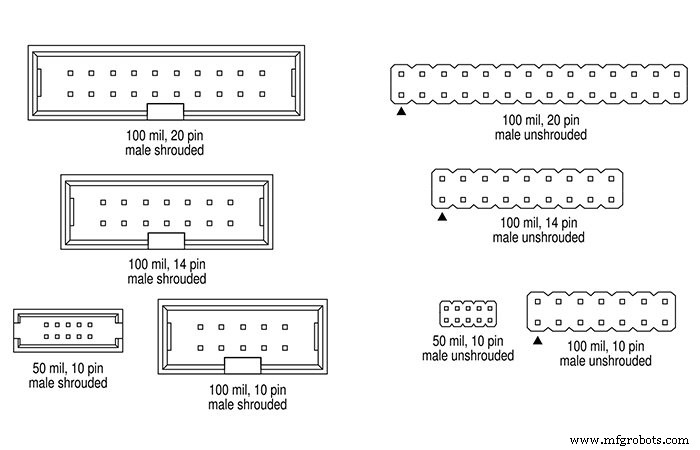

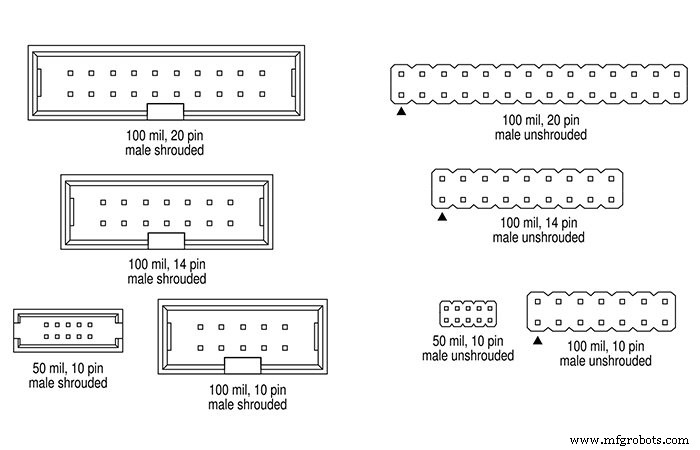

Sebagian besar header adalah header pria terselubung atau tidak tertutup, dengan 10, 14, atau 20 pin, dan pin pitch 0,1” atau 0,05”. Contohnya ditunjukkan pada Gambar 1.

Gambar 1. Header umum yang digunakan untuk menghubungkan ke antarmuka JTAG.

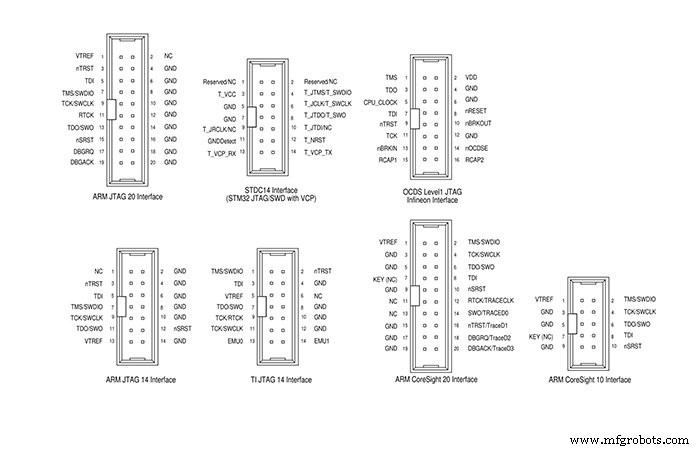

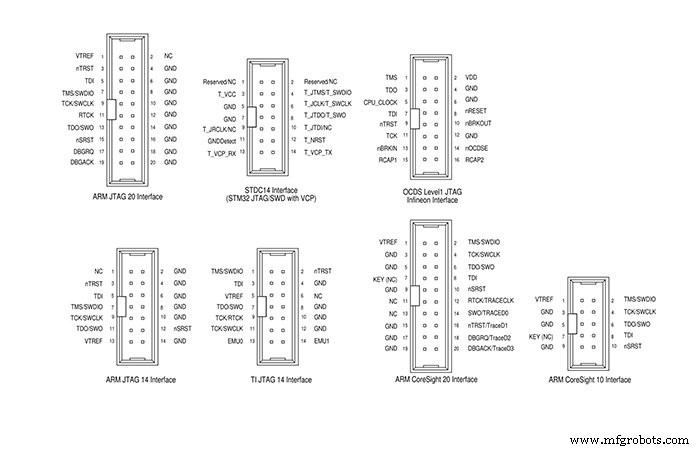

Pinout untuk berbagai antarmuka JTAG (tertaut di atas) ditunjukkan pada Gambar 2. Di sini Anda akan menemukan pin standar untuk JTAG (TDI, TDO, TCK, TMS, nTRST), serta debug kabel serial (SWDIO, SWCLK, SWO ), dan fungsi tambahan untuk debugging, seperti core tracing.

Gambar 2. Pinout dari berbagai antarmuka JTAG, ditampilkan pada header laki-laki terselubung 0,1” dalam kasus ini.

Khususnya yang menonjol di antara pin yang ditambahkan adalah nSRST (reset sistem penuh), yang memaksa target untuk disetel ulang sepenuhnya, dan VTREF (referensi target tegangan), yang terhubung ke rel suplai target untuk pemindahan level perangkat keras antarmuka JTAG.

Antarmuka JTAG

Beberapa antarmuka JTAG (juga disebut probe debug JTAG) tersedia di pasaran. Di arena perangkat keras open-source, ada Black Magic Probe atau BMP, yang dikembangkan oleh 1BitSquared dan Black Sphere Technologies, digunakan sebagai antarmuka ARM JTAG, yang memiliki komunitas besar dan aktif yang mendukungnya. Black Magic Probe juga dapat merujuk ke antarmuka JTAG mana pun yang firmwarenya telah diganti dengan firmware Black Magic Probe.

Probe debug komersial yang banyak digunakan dari Segger termasuk J-Link (ditunjukkan pada Gambar 3) dan J-Trace, probe debug yang jauh lebih maju dan mampu yang cocok untuk aplikasi industri. Di mana J-Link dapat ditemukan dengan harga di bawah $100 di bawah lisensi pendidikan, atau antara $400 - $1.000 untuk aplikasi komersial, J-Trace berharga antara $1.700 dan $2.500.

Gambar 3. Segger J-Link PRO debugging probe dan antarmuka JTAG

Vendor tertentu juga akan menjual antarmuka JTAG untuk produk mereka. STMicroelectronics menyediakan seri STLINK (termasuk STLINK/V2, dan STLINK-V3SET) untuk produk STM8 dan STM32 mereka, Atmel (sekarang Microchip) menyediakan Atmel-ICE, NXP memiliki S32 Debug Probe—daftarnya terus berlanjut.

FPGA juga menggunakan JTAG untuk mengunduh aliran bit ke perangkat/memori, tetapi antarmuka ini lebih sering disebut kabel unduhan. Contohnya termasuk Kabel Platform II Xilinx dan kabel unduhan FPGA Altera, yang sebelumnya dikenal sebagai USB-Blaster II, sekarang diganti namanya menjadi Kabel Unduhan Intel FPGA II.

Jadi apa sebenarnya yang terjadi di perangkat ini yang membuatnya begitu mahal? Fungsi apa yang mereka dukung, dan bagaimana desainer menggunakannya? Umumnya, jika Anda melihat ke dalam probe debug kelas bawah, Anda akan menemukan yang berikut:

- Sebuah mikrokontroler sebagai pengontrol JTAG utama

- Antarmuka USB, yang dapat disematkan di mikrokontroler atau mungkin disertakan secara terpisah, misalnya, chip FTDI

- Sirkuit pemindah level untuk kompatibilitas logika

- Mengalihkan sirkuit untuk mengaktifkan dan menonaktifkan berbagai jalur, pull-up, dll.

Dan itu saja. Sebagai contoh, lihat file perangkat keras Black Magic Probe, tersedia di Github. Sebagian besar pekerjaan (dan biaya) datang dari perangkat lunak, menyediakan alat debugging yang kuat (terkadang real-time) yang memungkinkan pengembang untuk memanfaatkan arsitektur Arm CoreSight secara maksimal.

Kesimpulan

Sampai saat ini, kami telah membahas standar JTAG, termasuk port akses uji (TAP) dan mesin statusnya. Dalam artikel ini, kami melihat sisi fisik JTAG, menyelidiki konektor dan antarmuka yang tersedia untuk desainer dari sumber terbuka hingga komersial kelas atas.

Dari sini, yang tersisa hanyalah melihat lebih dekat arsitektur Arm CoreSight dan antarmuka debug (ADI), yang akan menyertakan alternatif JTAG serial wire debug (SWD) yang semakin umum.