Memodelkan ADC Menggunakan Polinomial Intermodulasi dan Jumlah Bit Efektif

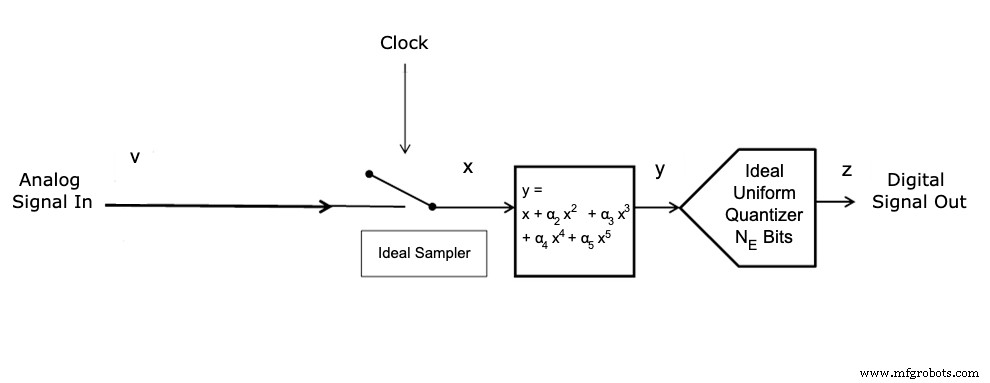

Pada artikel ini, kita membahas metodologi lain tentang bagaimana memodelkan ADC dalam simulasi sistem, kali ini dengan menggunakan jumlah bit yang efektif dan juga menyesuaikan ADC kita dengan memperkenalkan polinomial orde 5 ke input kuantizer yang ideal.

Sejauh ini dalam seri ini, kita telah membahas manfaat dari berbagai cara untuk memodelkan konverter data dalam simulasi sistem, terutama dengan menggunakan metode pemodelan menggunakan jumlah bit efektif atau ENOB.

Sekarang, kita akan melanjutkan diskusi ini dengan menambahkan elemen baru:menyesuaikan model ADC kita secara langsung dengan polinomial orde ke-5 yang ditambahkan ke input quantizer yang ideal.

Deskripsi Model ADC Baru Kami

Model yang disajikan dalam artikel kami sebelumnya tidak menghasilkan frekuensi palsu (taji) yang berbeda. Karena taji merupakan karakteristik penting dari kinerja ADC, diperlukan model yang lebih baik.

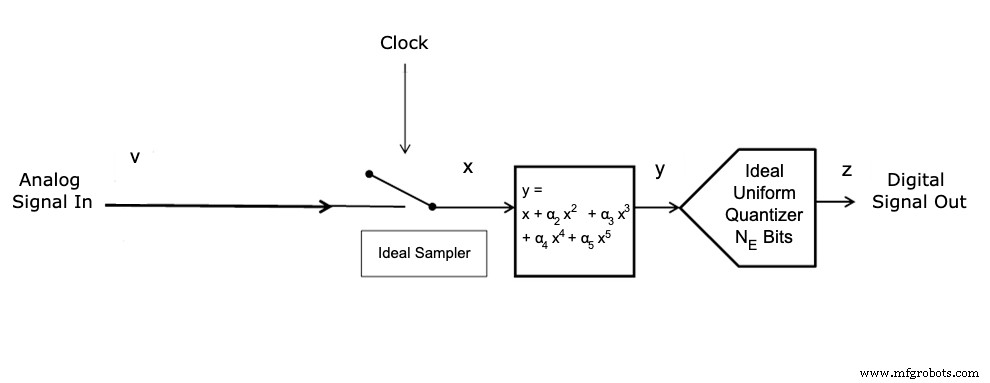

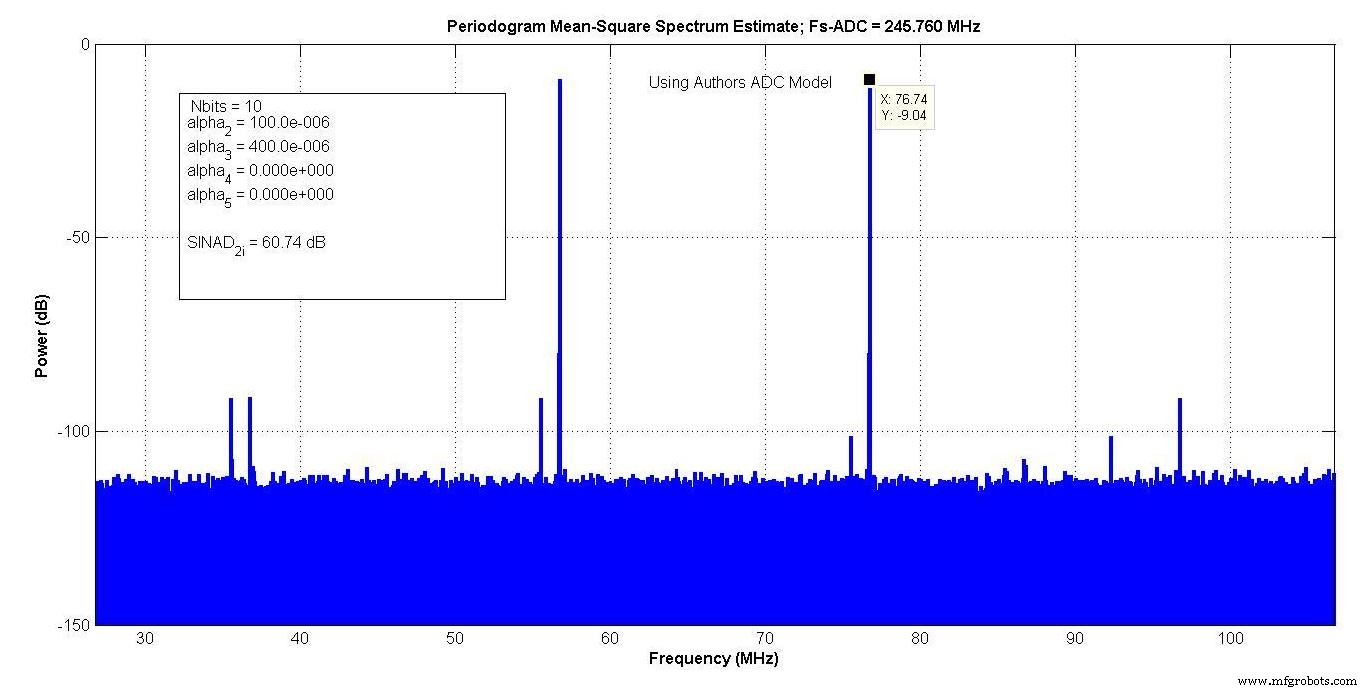

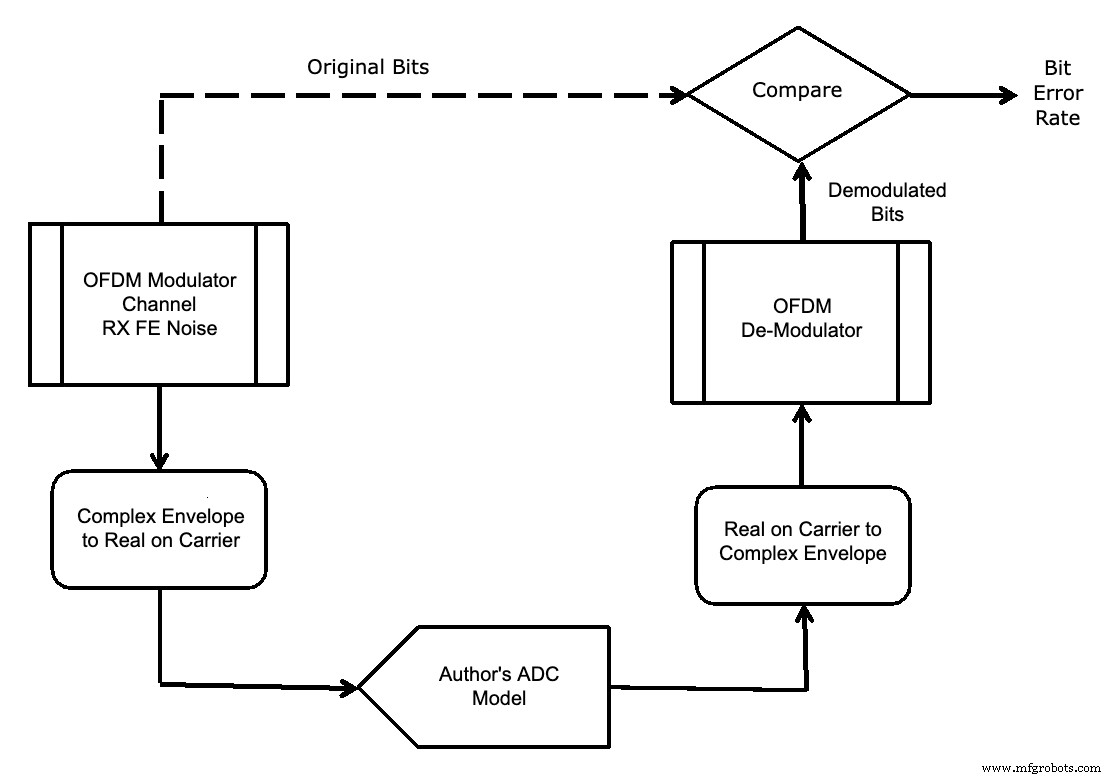

Ini ditunjukkan pada Gambar 1.

Gambar 1.

Ini menambahkan polinomial orde ke-5 ke input quantizer yang ideal.

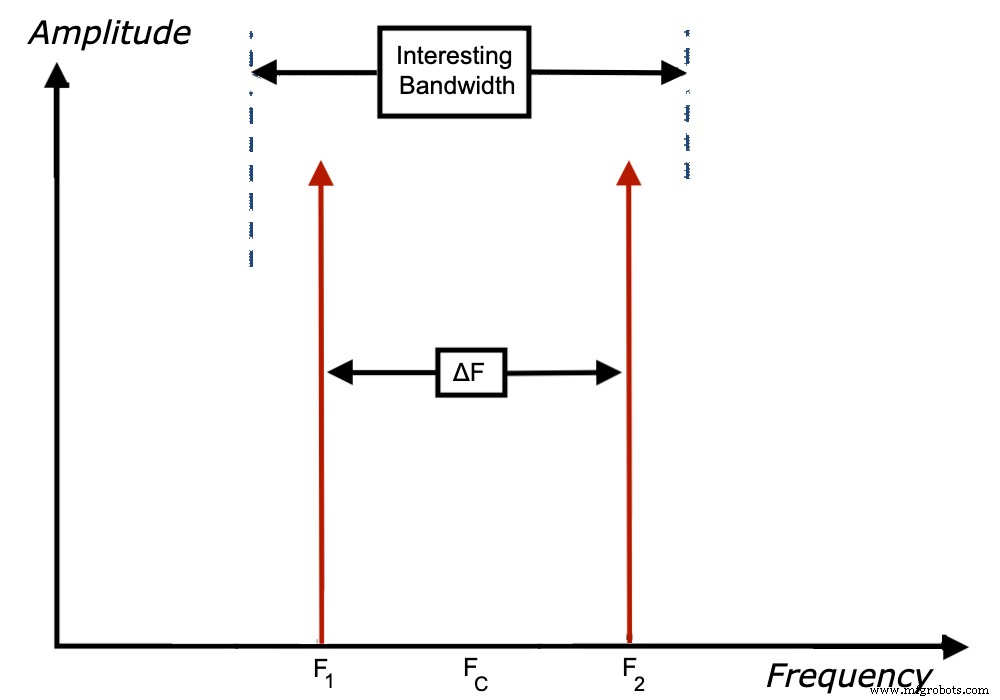

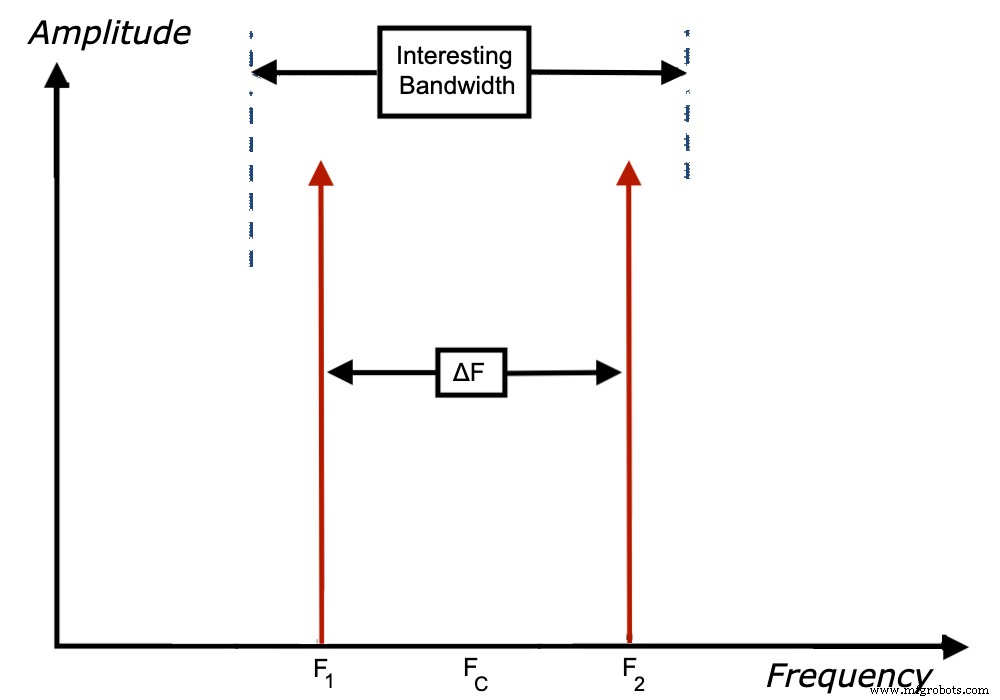

Input dua nada harus digunakan untuk menentukan parameter i (fc ) dan NE (fc ); di mana fc adalah frekuensi tengah antara nada, seperti yang ditunjukkan pada Gambar 2 (yang akan Anda kenali sebagai Gambar 4 dari artikel pertama kami).

Gambar 2.

Jika salah satu dari parameter ini juga merupakan fungsi dari f, pemisahan antara nada, mungkin ada non-linearitas dengan memori di ADC, dan model ini tidak akan berlaku.

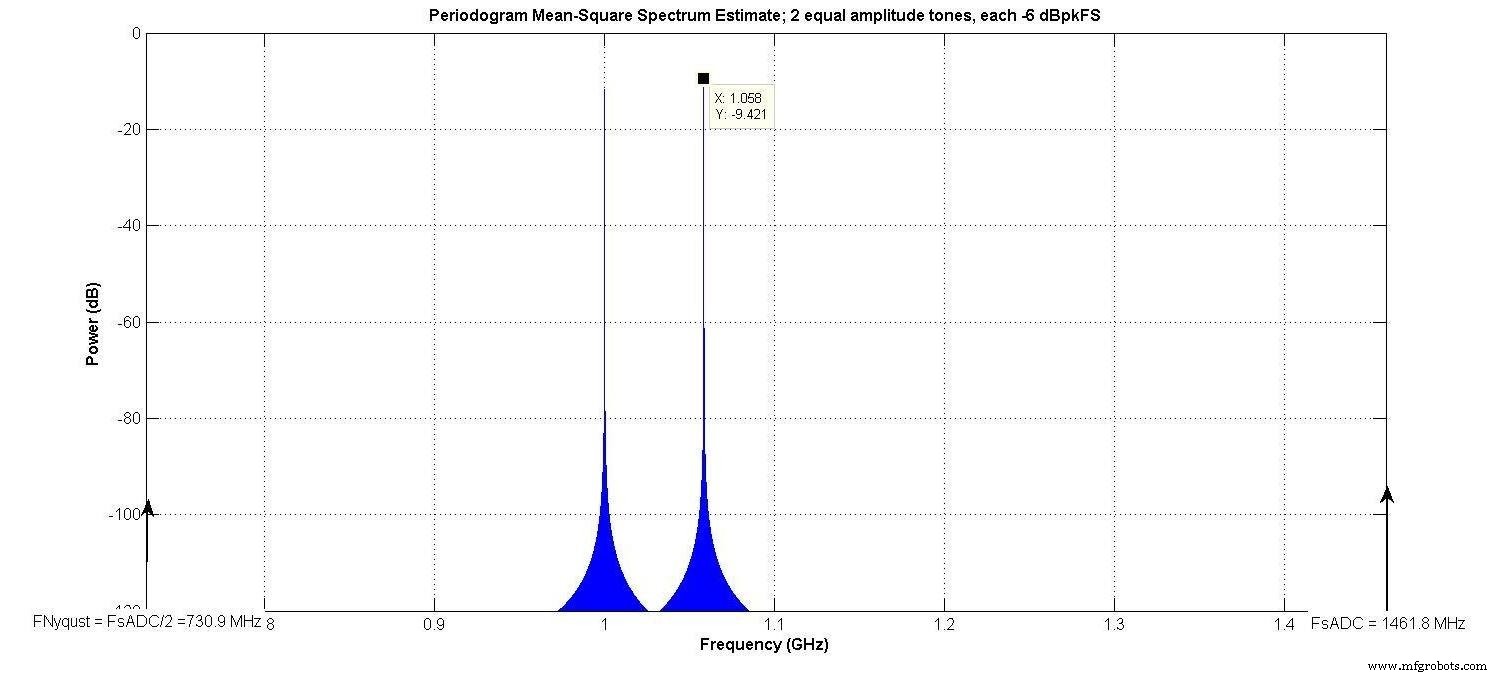

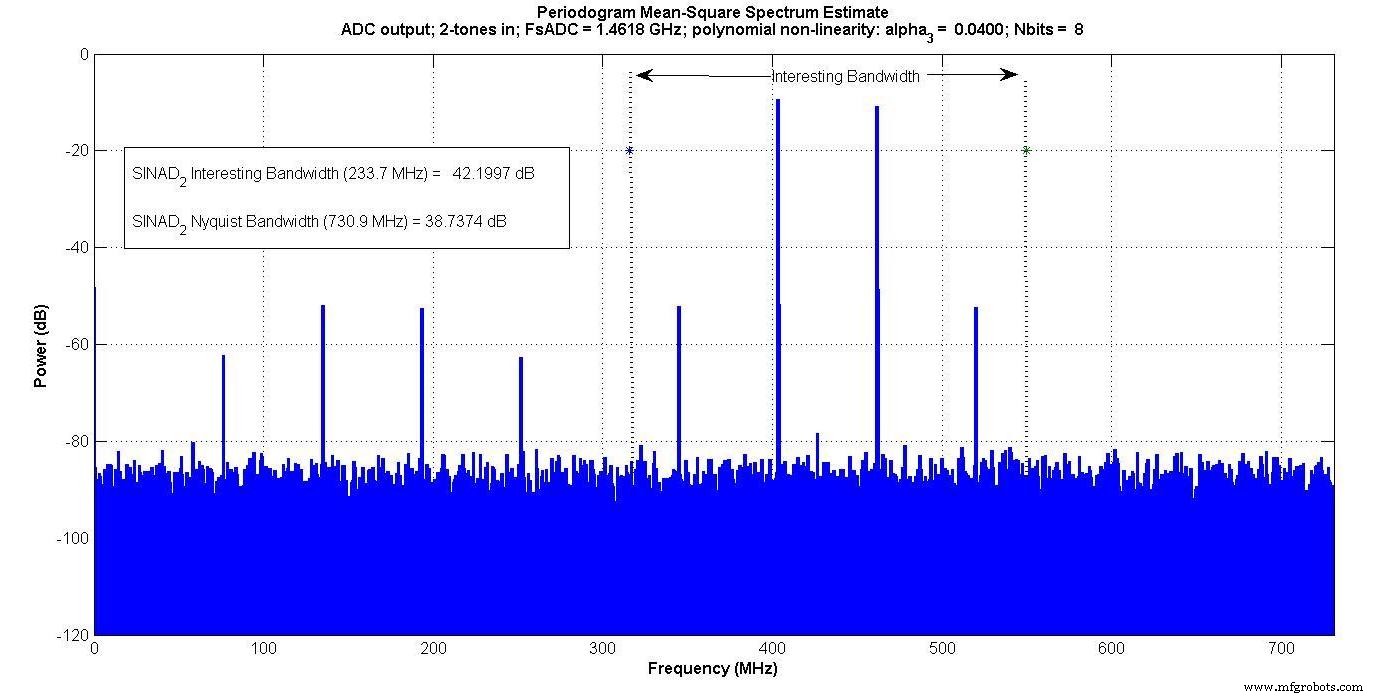

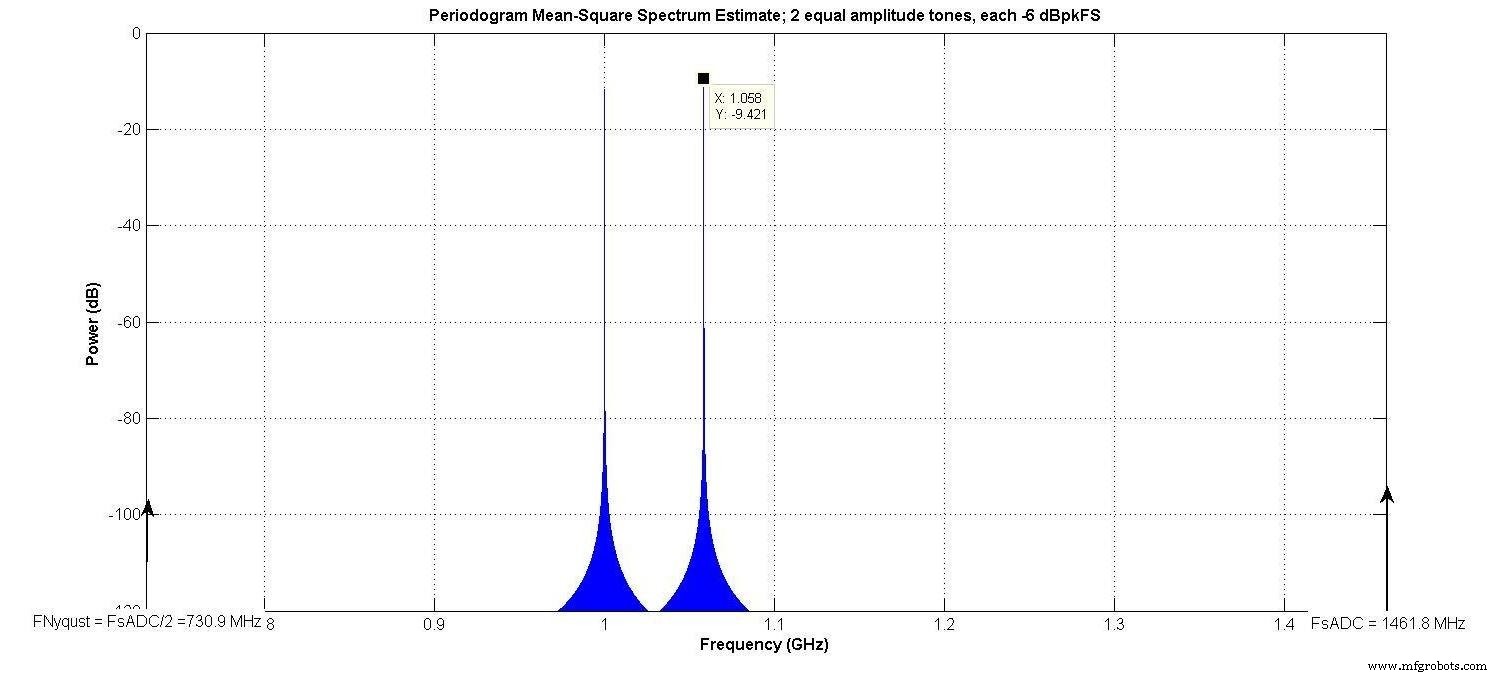

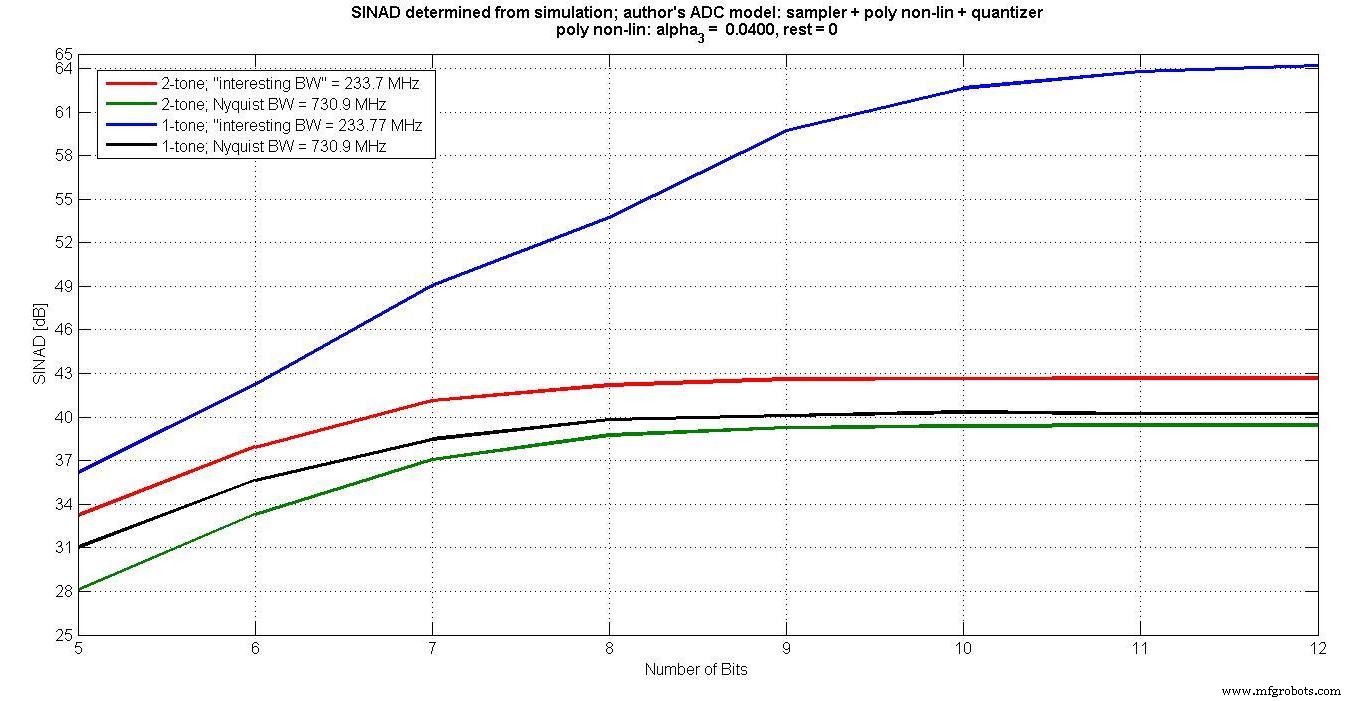

Sebagai contoh, input dua nada yang sama seperti yang ditunjukkan pada Gambar 3 (dibahas sebagai Gambar 3 dari artikel kami sebelumnya) digunakan, dengan NE =8 bit, 3 =0,04, dan yang lainnya i =0. Bandwidth Nyquist yang sama (730,9 MHz) dan “bandwidth menarik” (233,7 MHz) seperti pada artikel kami sebelumnya.

Gambar 3.

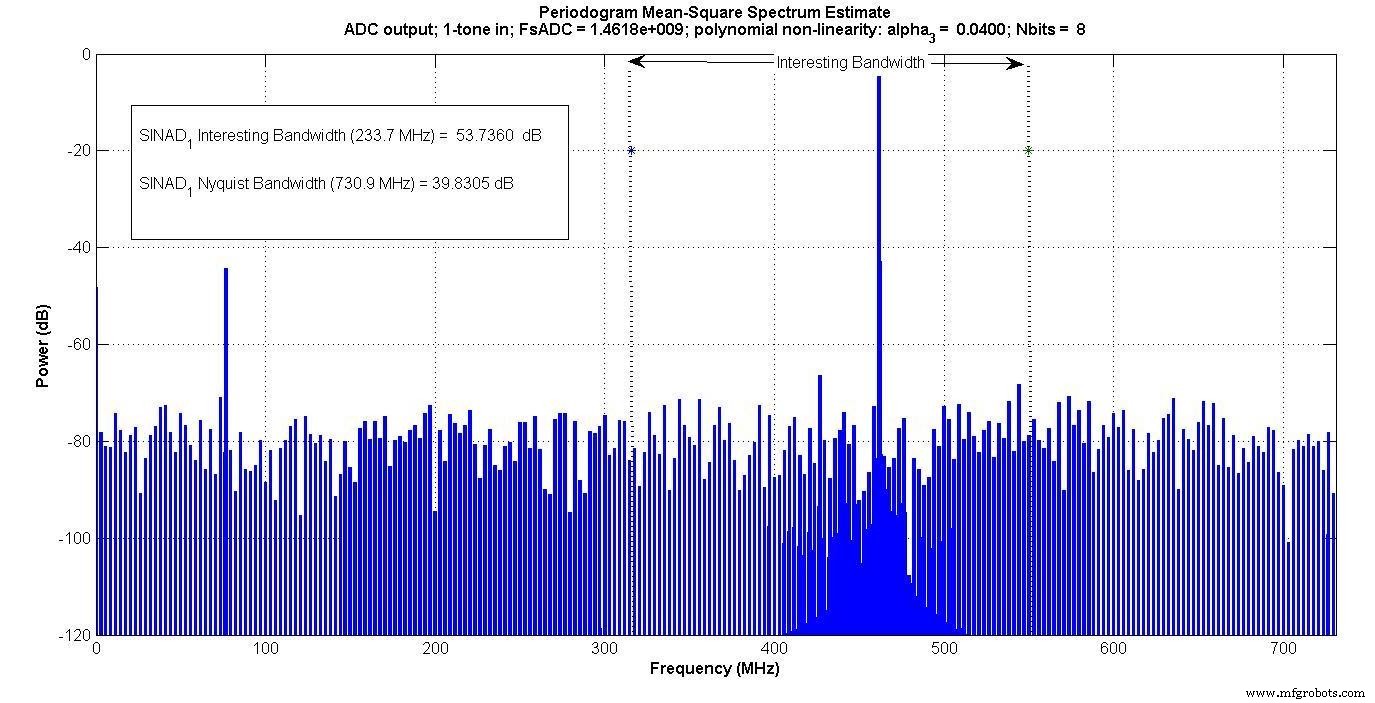

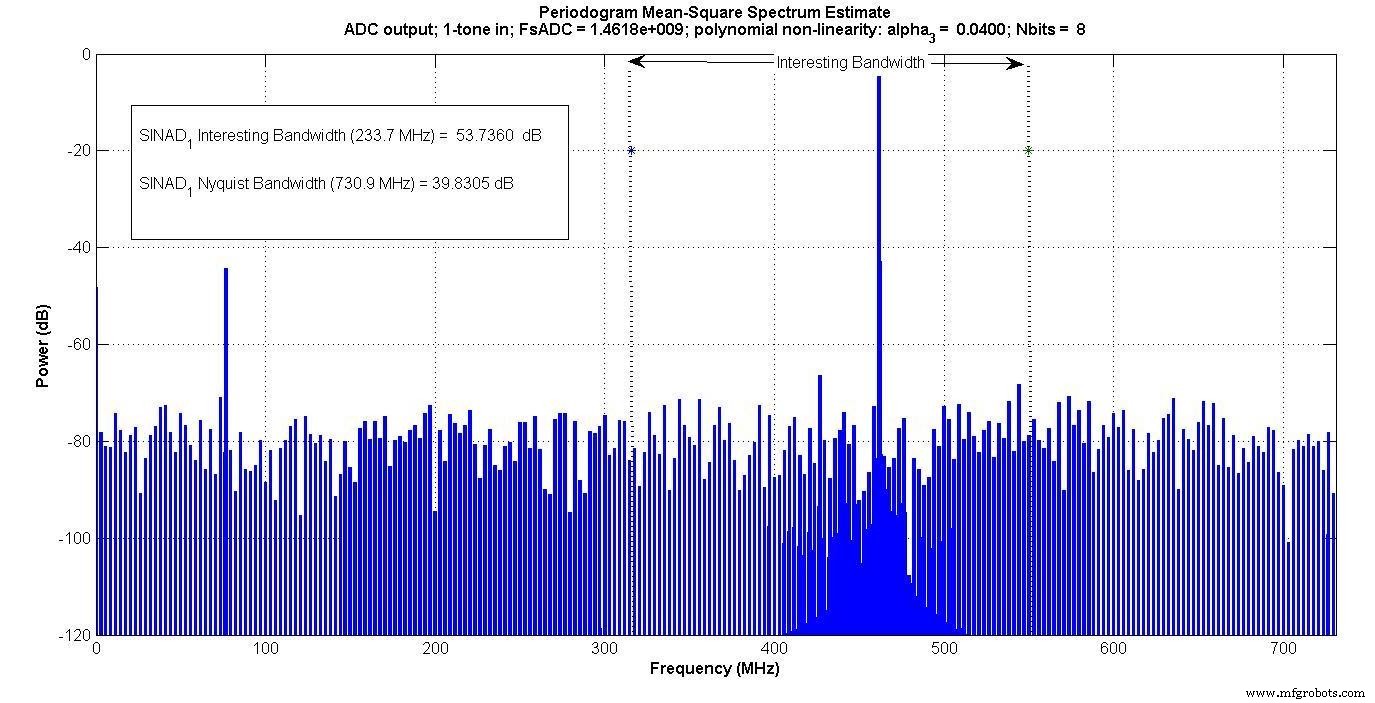

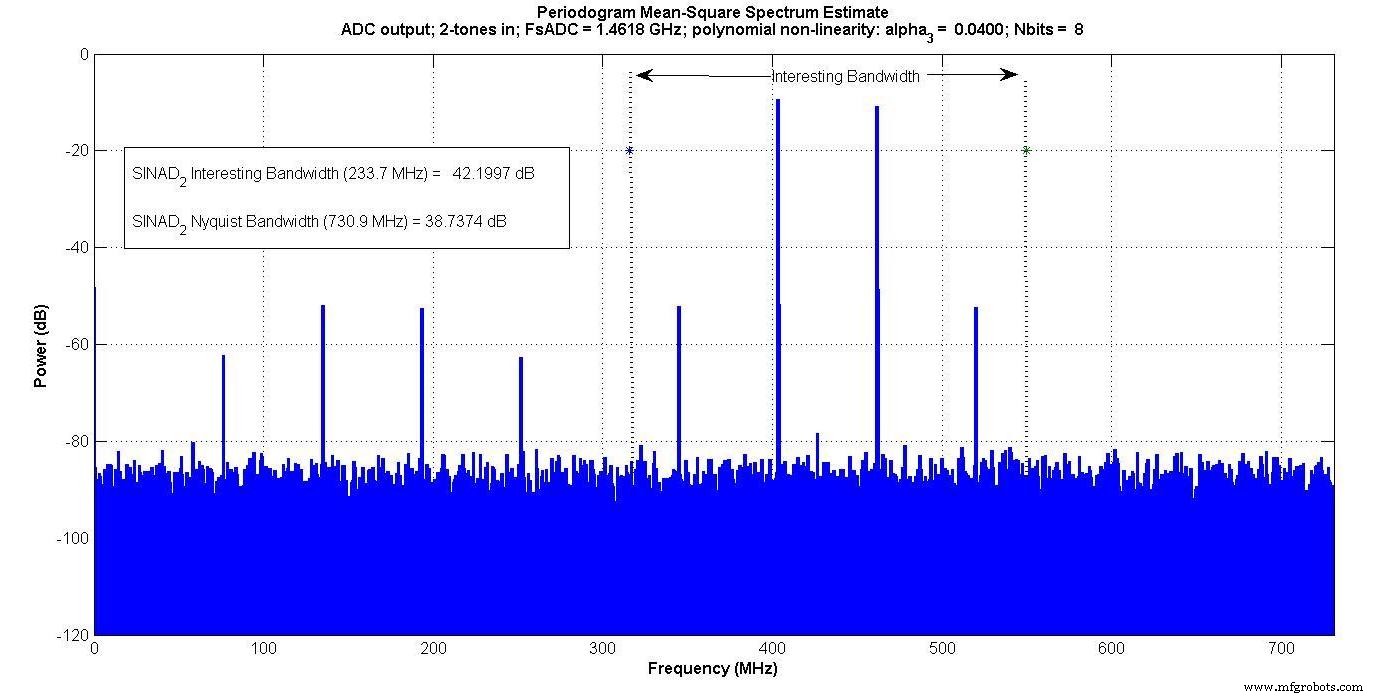

Gambar 4 menunjukkan output dengan input satu nada, dan Gambar 5 menunjukkan output dengan input dua nada.

Gambar 4.

Gambar 5.

Produk intermodulasi muncul di dalam "bandwidth menarik" untuk input dua nada, tetapi tidak untuk input satu nada.

Jika seseorang hanya mengukur di dalam "bandwidth yang menarik" ini—misalnya, jika ada filter bandpass digital yang hanya melewati pita itu—tes satu nada tidak akan menangkap efek intermodulasi, tetapi dua nada akan.

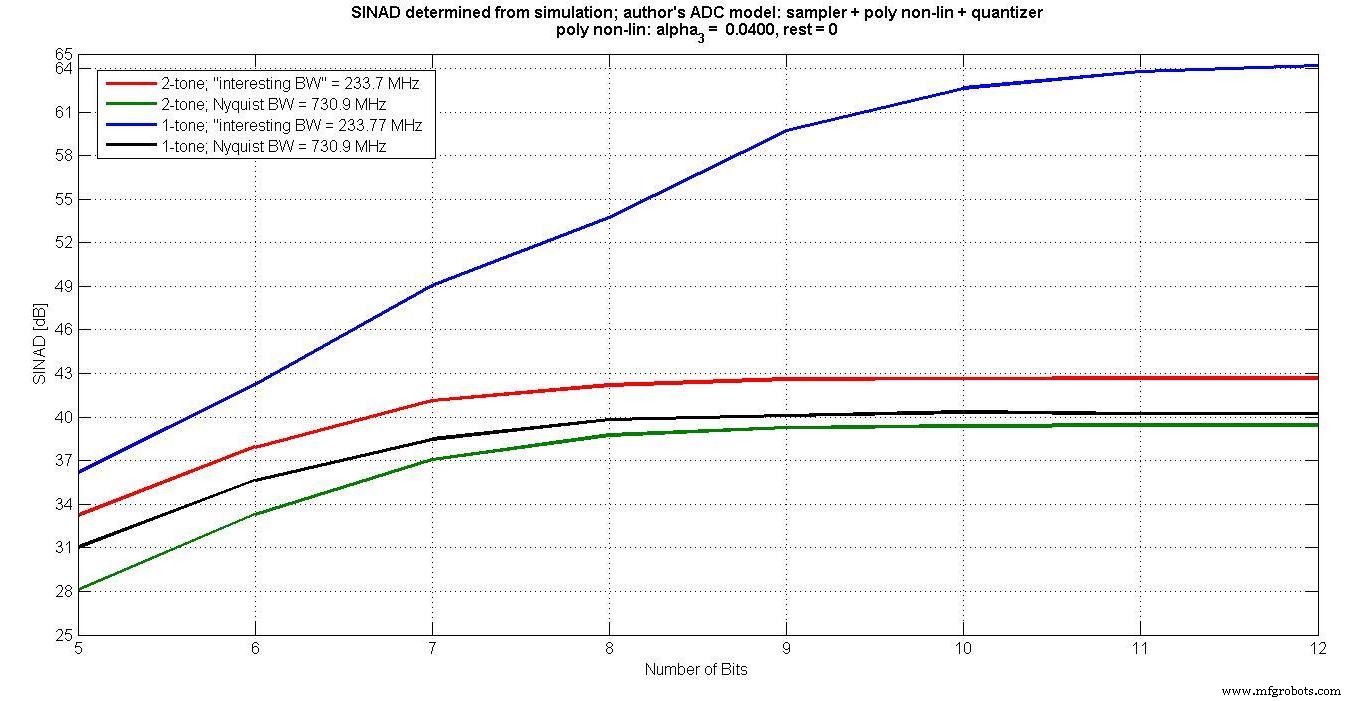

Gambar 6 memplot berbagai SINAD untuk 5 hingga 12 bit input. Jelas bahwa input satu nada, diukur dalam "bandwidth menarik", tidak menangkap efek intermodulasi lebih dari 7 bit.

Gambar 6.

Juga, untuk lebih dari 7 bit, karena derau kuantisasi berkurang dengan bertambahnya jumlah bit, tetapi distorsi intermodulasi tetap sama, SINAD tidak meningkat dengan lebih banyak bit.

Perbandingan dengan Model Pabrikan

Pembaca yang Terhormat:Anda sekarang mungkin bertanya-tanya; "Terus? Ini hanya beberapa model dan tanggapan mereka terhadap beberapa sinyal. Apa tujuannya?”

Tujuannya adalah agar pengukuran dua nada dapat dilakukan pada ADC, dan nilai parameter yang ditunjukkan pada Gambar 1 dipilih agar paling sesuai dengan keluaran ADC yang diukur. Ini sering dapat dilakukan dengan menyesuaikannya secara manual sampai diperoleh kecocokan yang baik. Kemudian, model yang disederhanakan dapat digunakan dalam simulasi tingkat kesalahan bit panjang (BER).

Pengukuran dapat dilakukan pada perangkat yang sebenarnya, pada model yang baik untuk perangkat tersebut, atau diperoleh dari lembar data produsen.

Untuk menjadi model yang baik, itu harus mendekati perangkat yang sebenarnya; seperti model SPICE lengkap. Model rumit seperti itu akan memakan waktu terlalu lama untuk dijalankan dalam simulasi BER.

Apa yang tersedia untuk penulis Anda dari produsen adalah apa yang mereka sebut model "perilaku", yang mereka klaim menangkap semua parameter penting dari model ADC tertentu. Model pabrikan juga memperhitungkan jitter jam internal dan eksternal. Ini digunakan untuk mengevaluasi metode.

Masukan Dua Nada

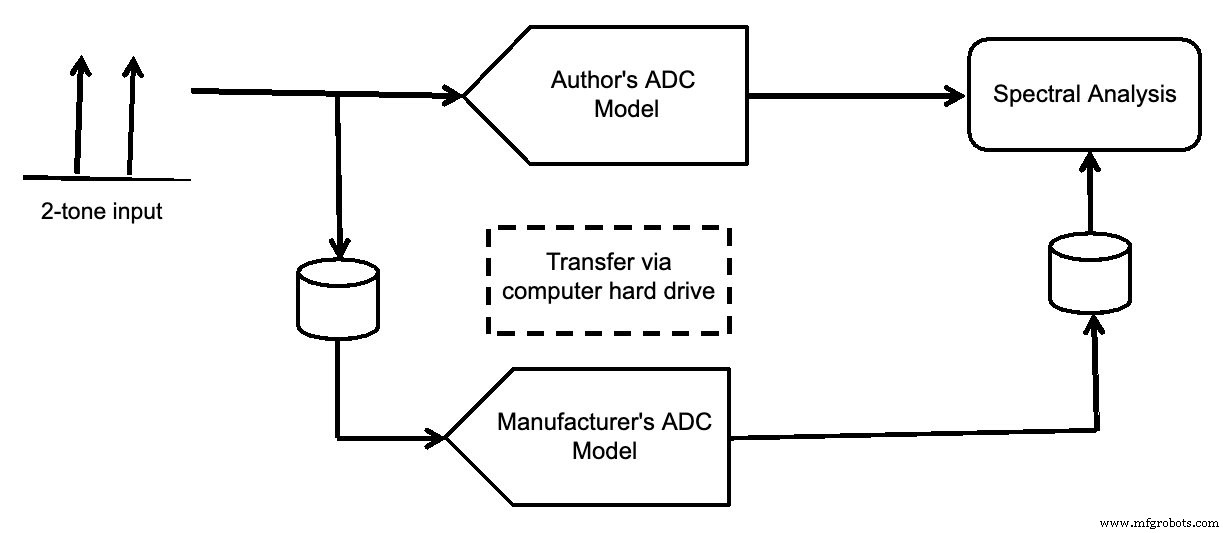

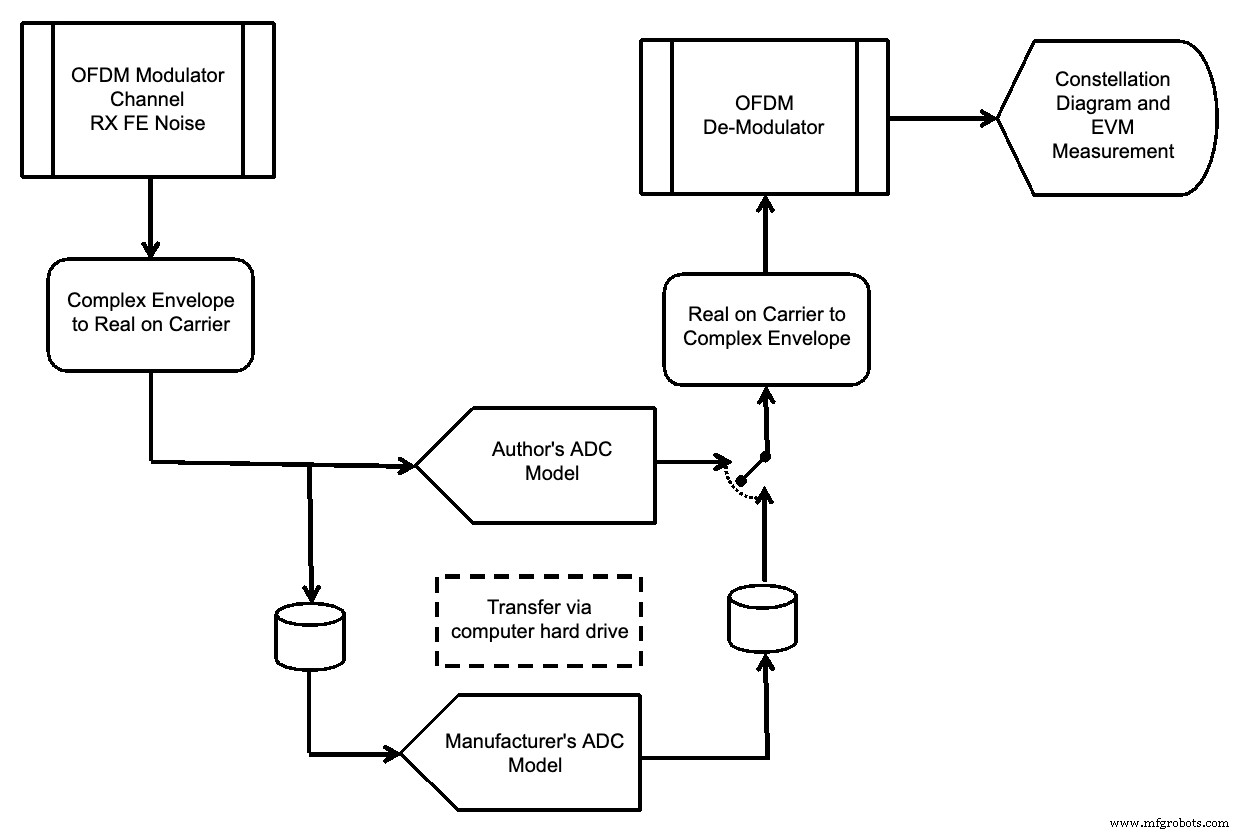

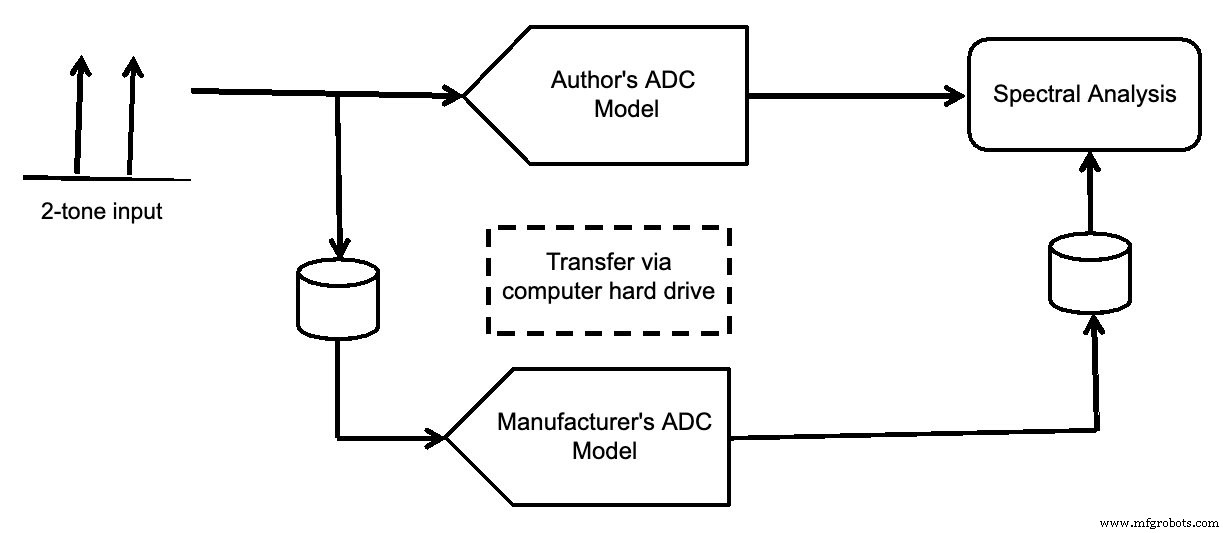

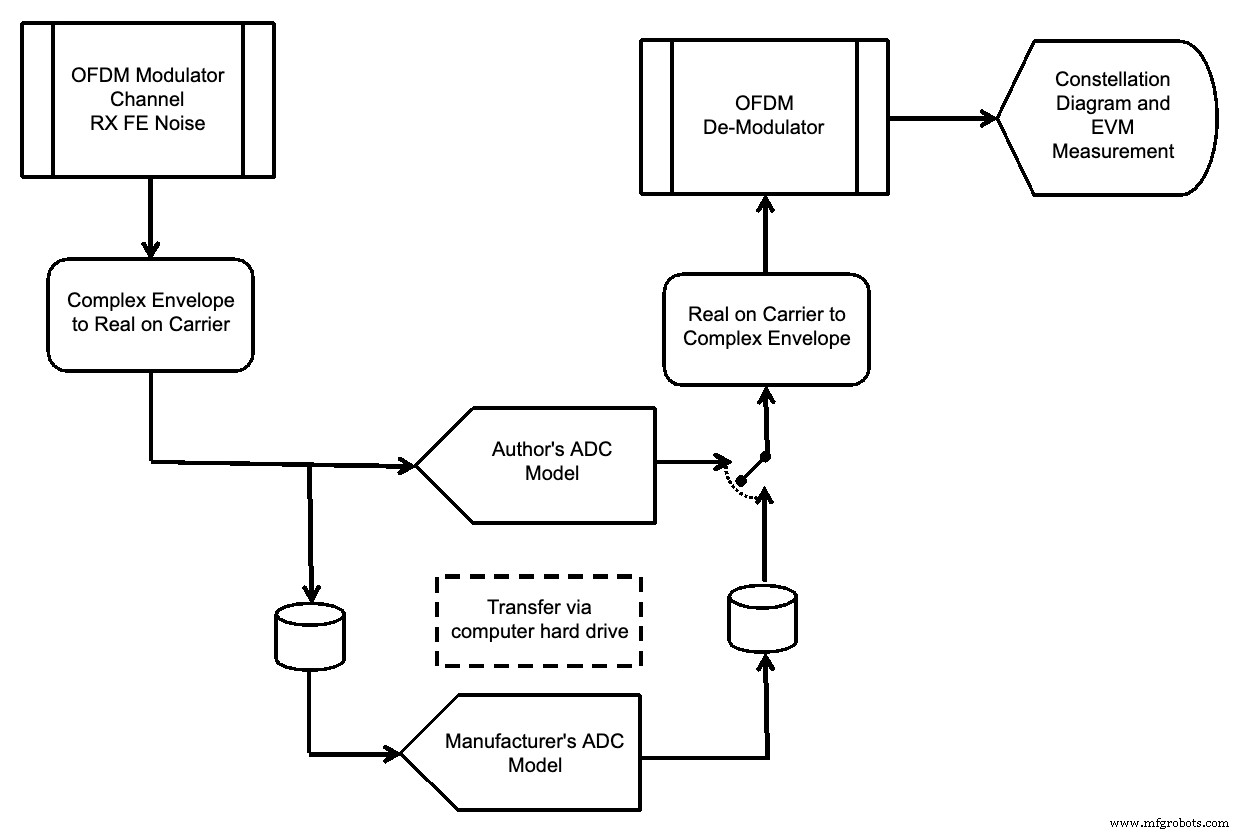

Gambar 7 menunjukkan set-up simulasi. Input dua nada dibuat, dan kemudian dimasukkan ke model pembuat dan pabrikan Anda. Keduanya ditampilkan dengan analisis spektral.

Gambar 7.

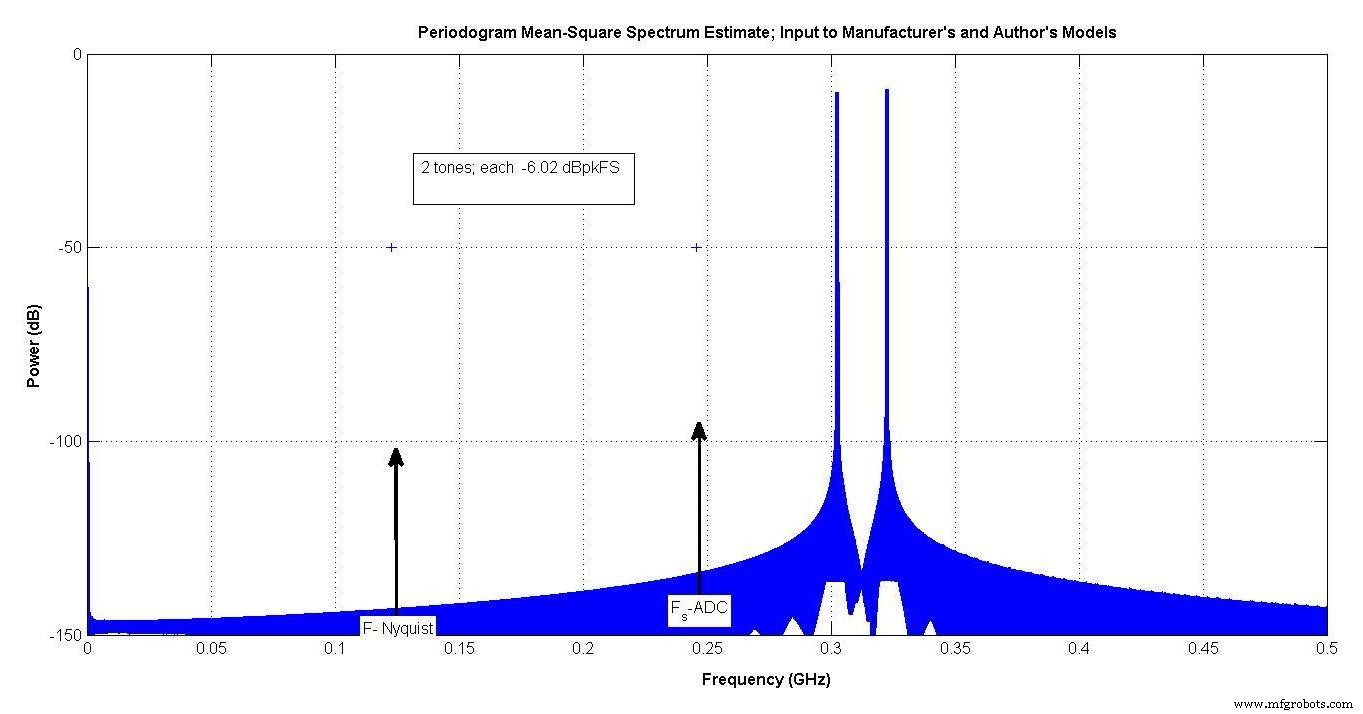

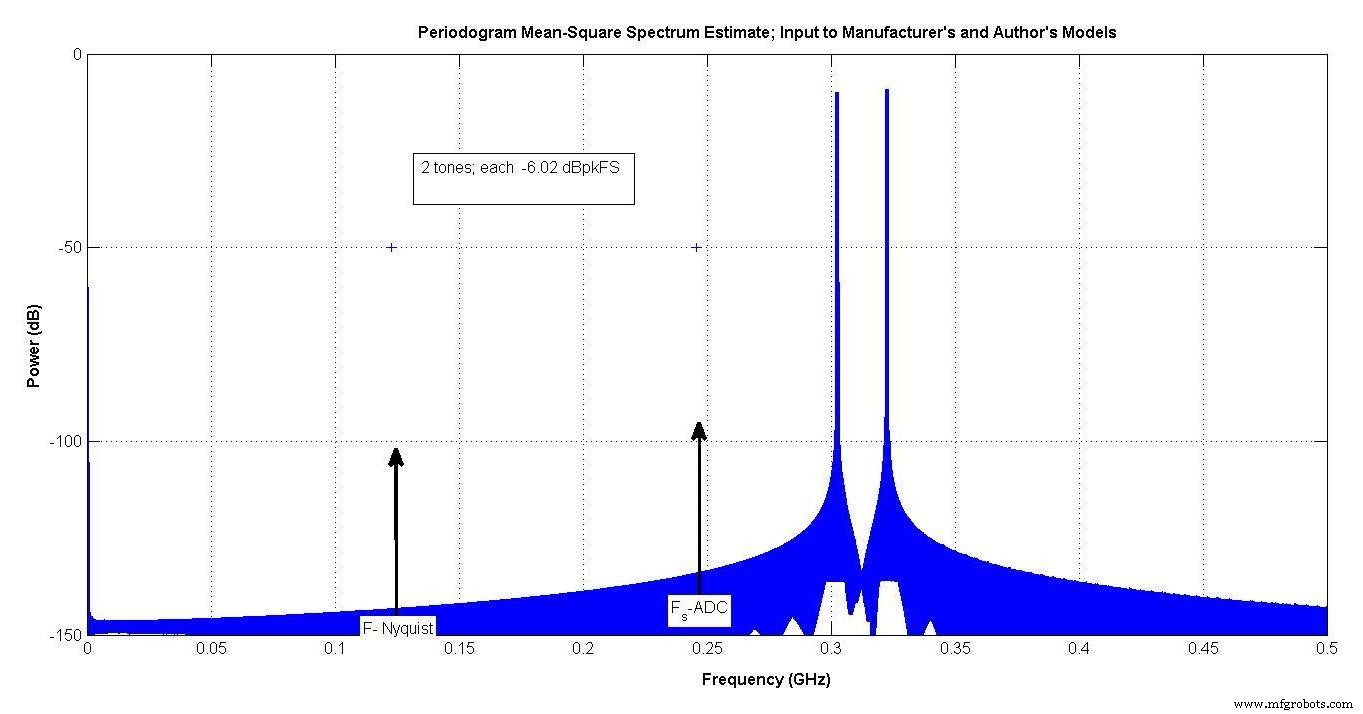

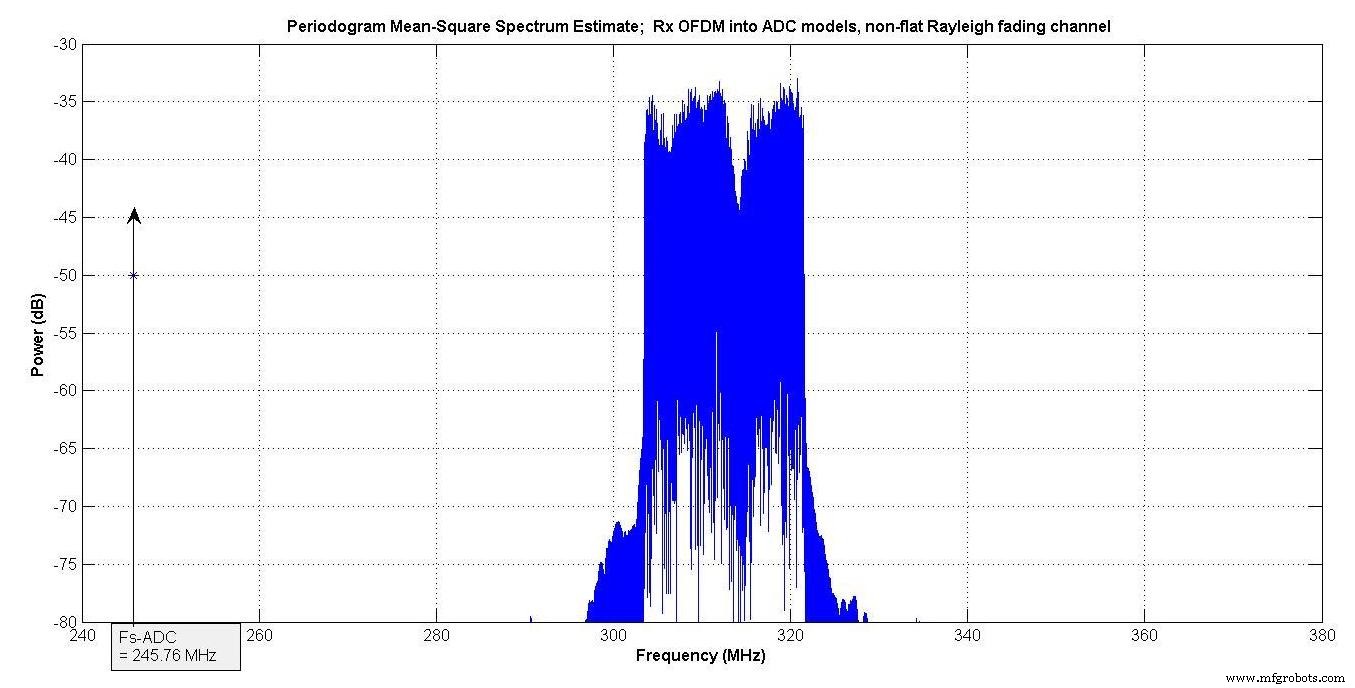

Gambar 8 menunjukkan input yang digunakan. Kedua nada tersebut antara 300 dan 350 MHz. Frekuensi pengambilan sampel ADC kira-kira 250 MHz, jadi nada ini berada di zona Nyquist ke-3.

Karena masing-masing berada pada -6,02 dBpeakFS, ketika mereka menambahkan fase, tegangan akan menjadi dua kali lipat, menghasilkan 0 dBpeakFS.

Gambar 8.

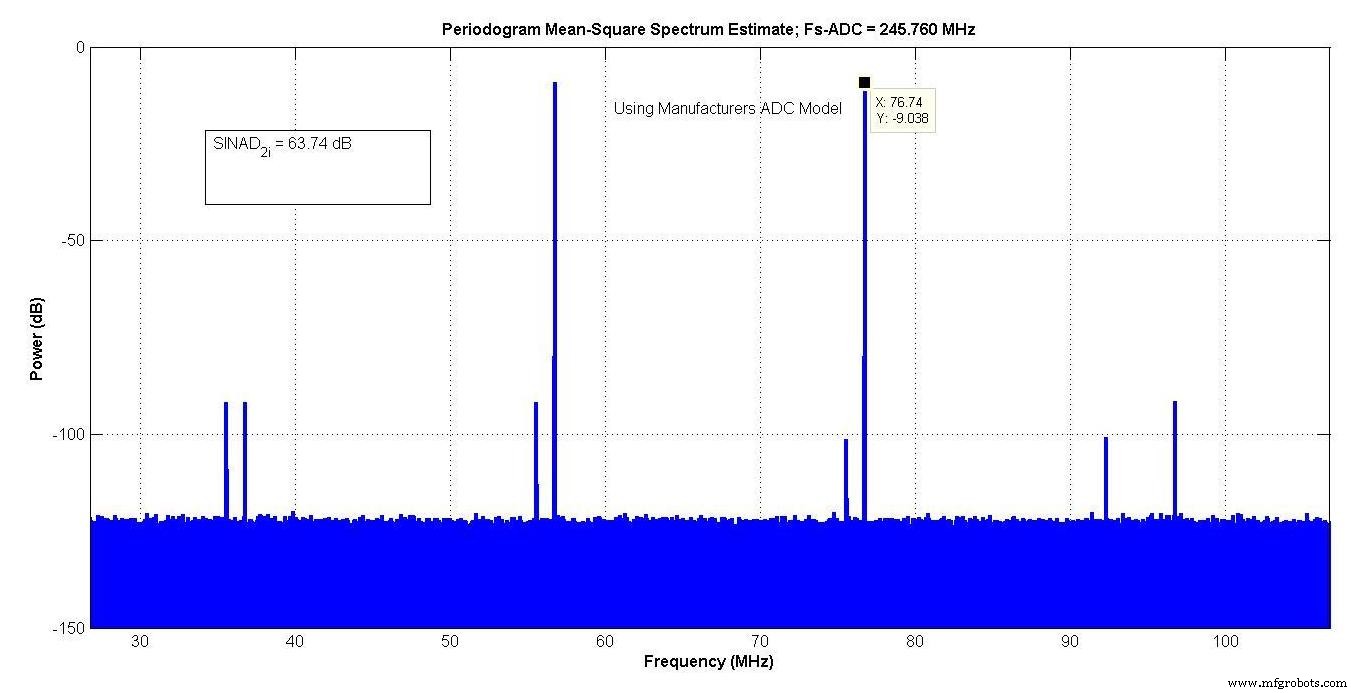

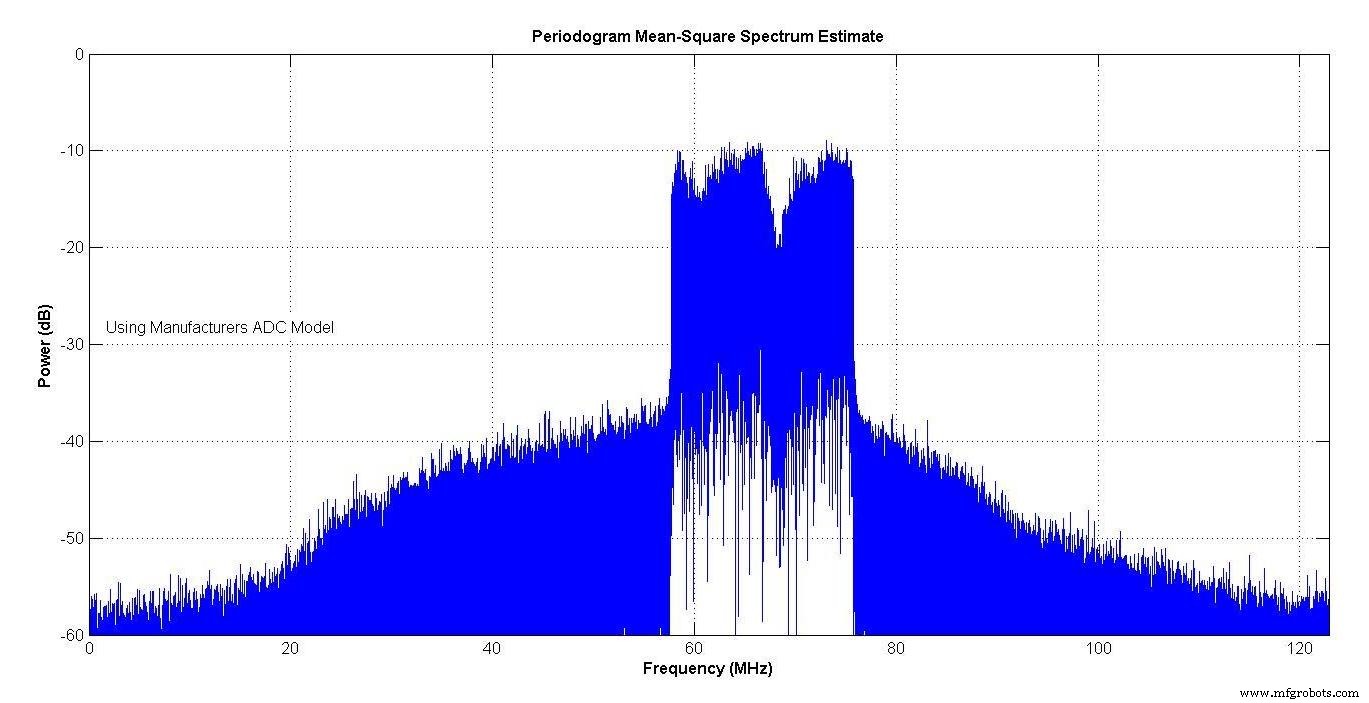

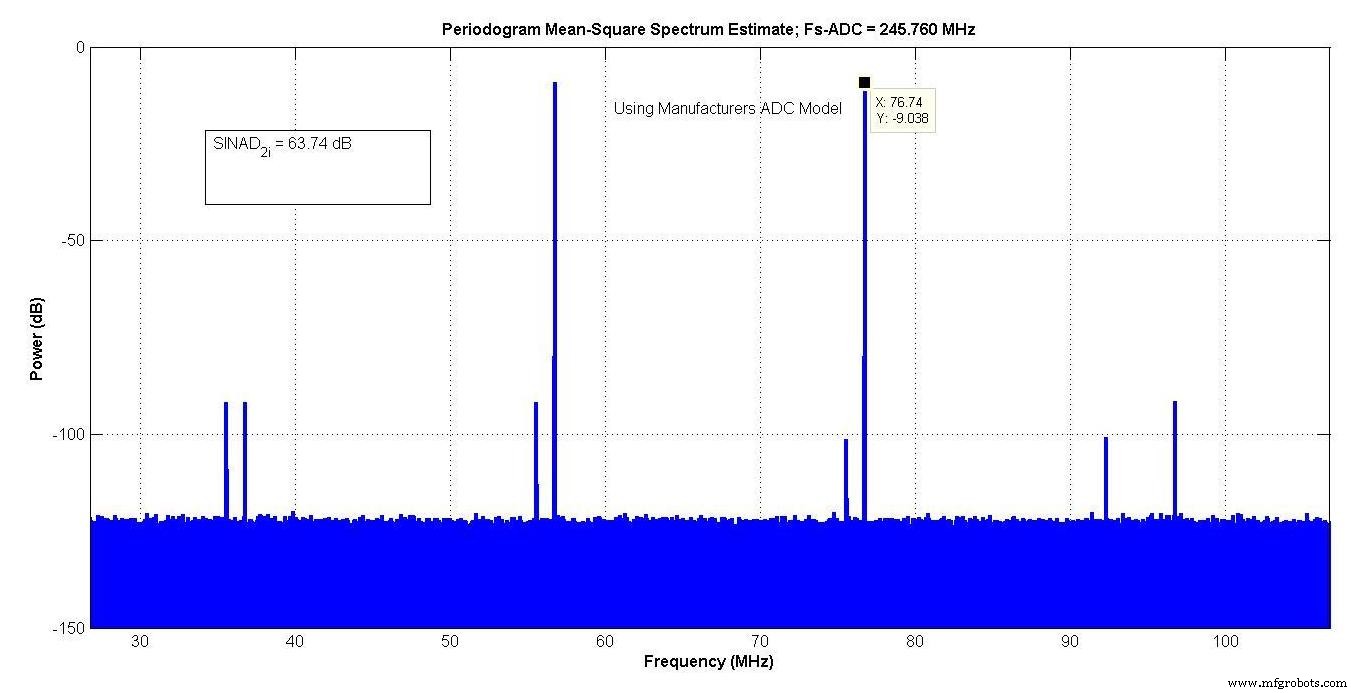

Gambar 9 menunjukkan keluaran model pabrikan, yang memiliki SINAD sebesar 63,74 dB dalam “bandwidth menarik” dari sekitar 27 hingga 107 MHz.

Gambar 9.

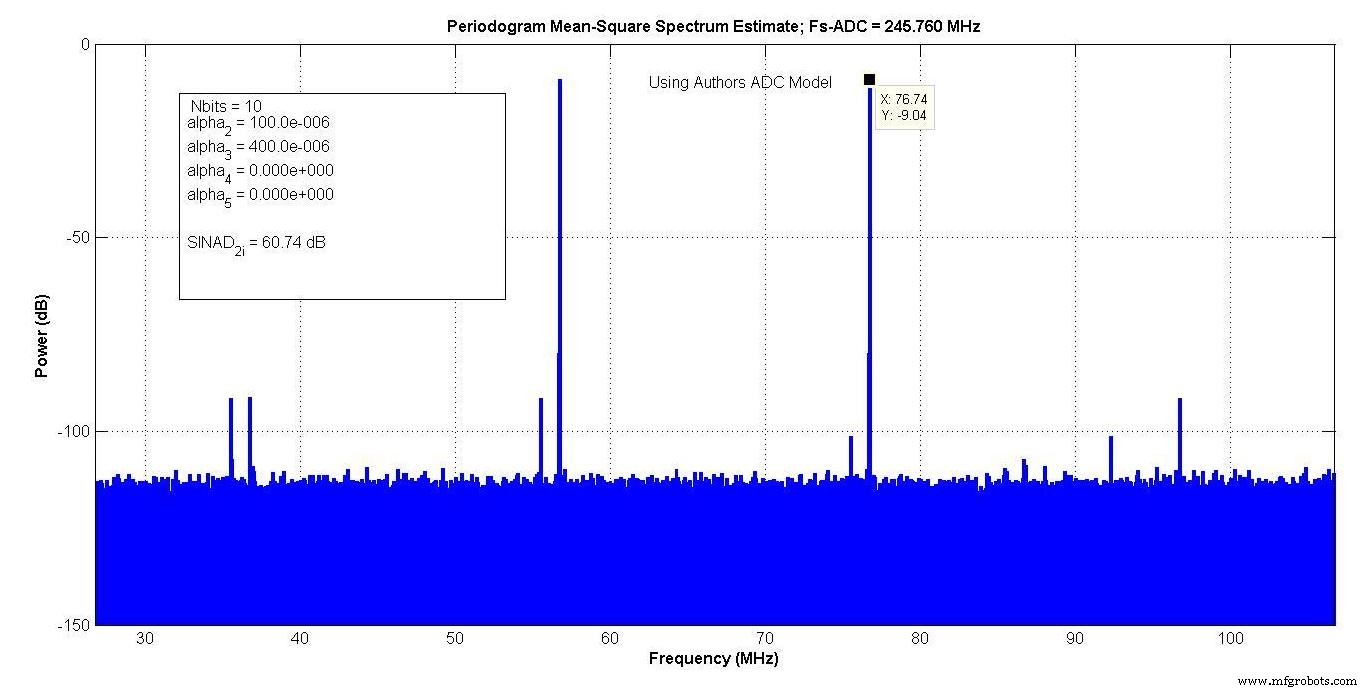

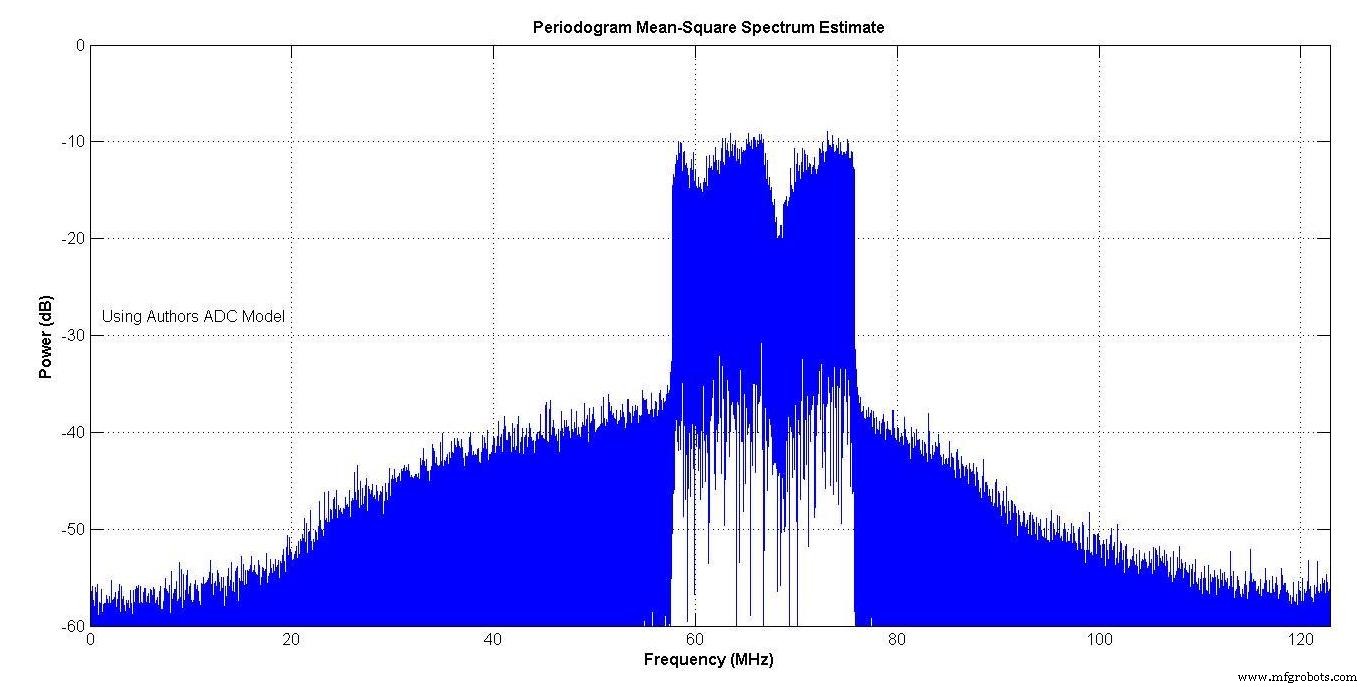

Gambar 10 menunjukkan hasil setelah menyesuaikan parameter model penulis Anda untuk kecocokan.

Gambar 10.

Koefisien polinomial memberikan derajat kebebasan yang cukup sehingga kecocokan yang hampir tepat dapat dibuat untuk taji. TE dari 11 bit memberikan tingkat kebisingan 3 dB di bawah model pabrikan, dan NE dari 10 bit memberikannya 3 dB di atas model pabrikan.

Penulis Anda memutuskan untuk menggunakan nilai pesimistis 10 bit, yang memberikan SINAD 60,74 dB. Model yang ditingkatkan akan memungkinkan hingga 6 dB derau Gaussian putih aditif ditambahkan, sehingga nilai NE yang lebih tinggi dapat dipilih, dan kebisingan tambahan ditambahkan agar sesuai dengan tingkat kebisingan.

Masukan Bentuk Gelombang OFDM

Kedua model sekarang dapat dibandingkan dengan bentuk gelombang komunikasi sebagai input.

Paket perangkat lunak yang tersedia secara komersial dilengkapi dengan model LTE; yang menghasilkan sinyal OFDM. Model ini mencakup modulator, saluran fading Rayleigh selektif frekuensi, derau Gaussian putih aditif, dan demodulator.

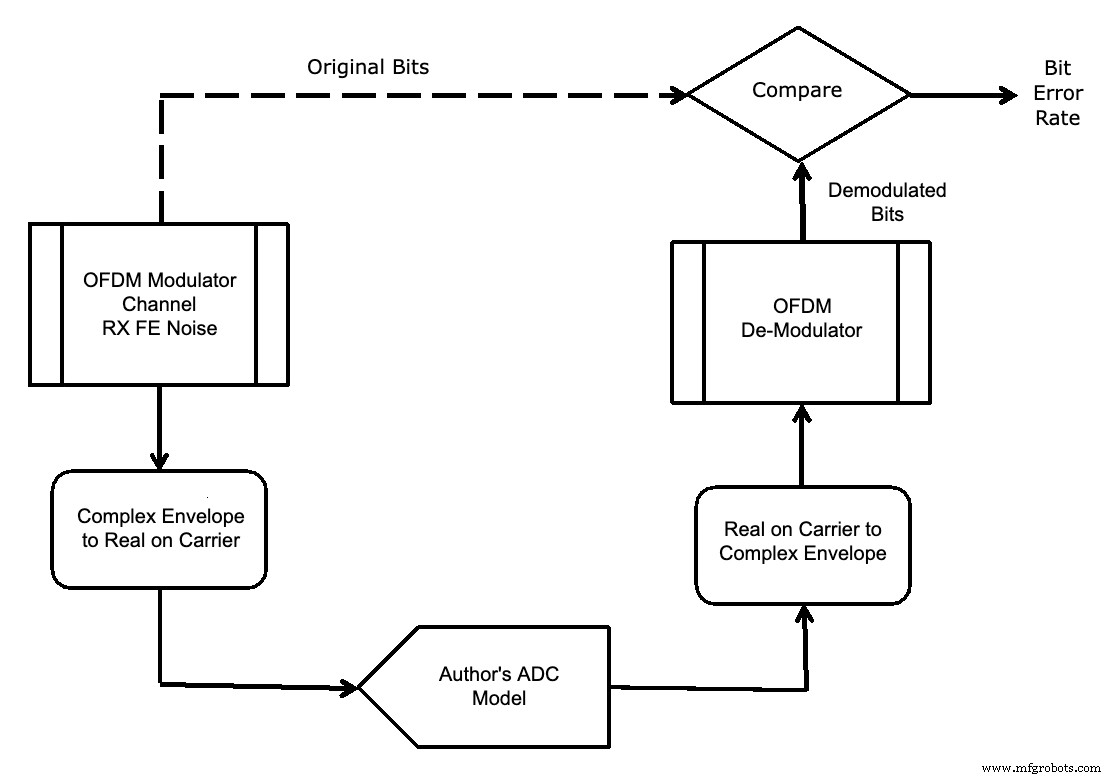

Dimungkinkan untuk memasukkan model ADC di depan demodulator, dan mengevaluasi spektrum output ADC, dan besarnya vektor kesalahan sinyal OFDM, seperti yang ditunjukkan pada Gambar 11.

Gambar 11.

Sinyal OFDM yang memiliki subcarrier 64-QAM digunakan. Parameter model ADC penulis Anda sama seperti yang digunakan untuk Gambar 10.

Paket perangkat lunak yang tersedia secara komersial menggunakan notasi amplop kompleks [3] untuk membentuk sinyalnya. Hal ini memungkinkan hanya informasi modulasi untuk dilacak sampel-ke-sampel dengan bilangan kompleks, dan frekuensi pembawa hanya disimpan sebagai konstanta yang diketahui. Jadi, jumlah sampel yang dibutuhkan untuk menggambarkan bentuk gelombang sangat berkurang.

Namun, input ke model ADC harus berupa sinyal nyata pada pembawa eksplisit, untuk memperhitungkan perbedaan kinerja ADC sebagai fungsi frekuensi input. Jadi, transformasi “Amplop Kompleks menjadi Nyata pada Pembawa” dan “Nyata pada Pembawa ke Amplop Kompleks” [3] perlu dilakukan.

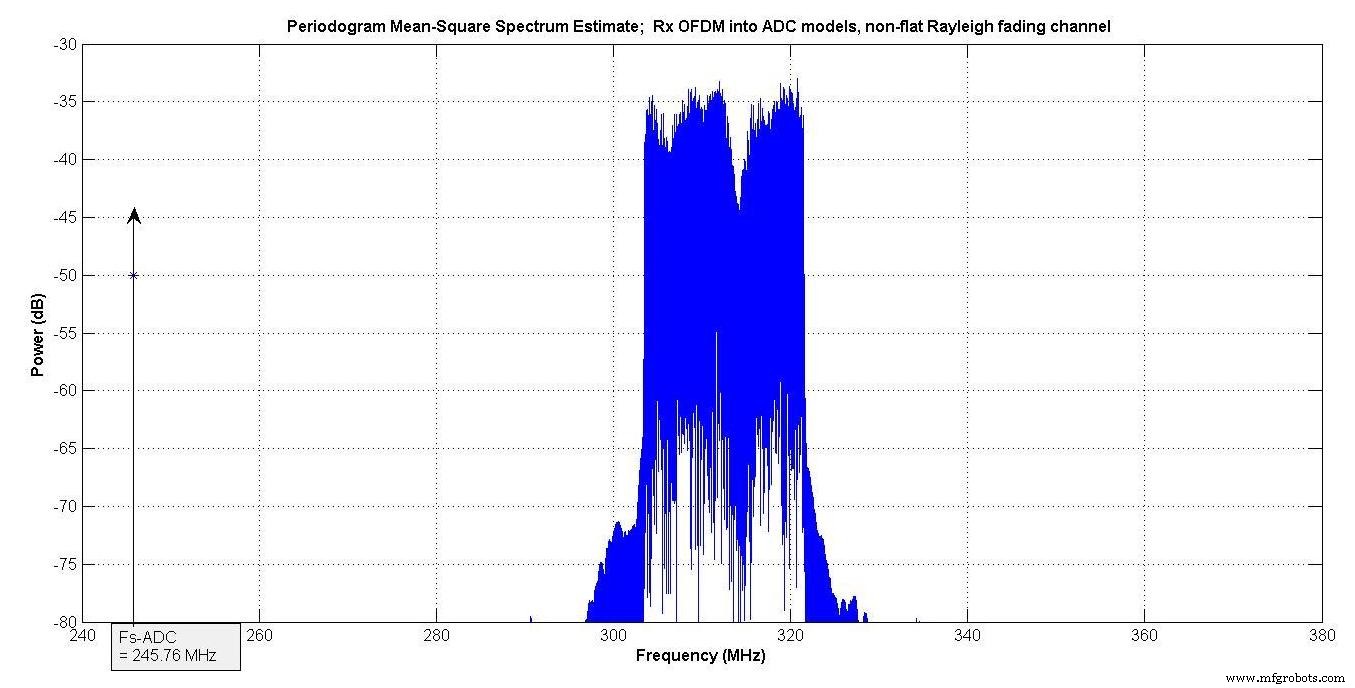

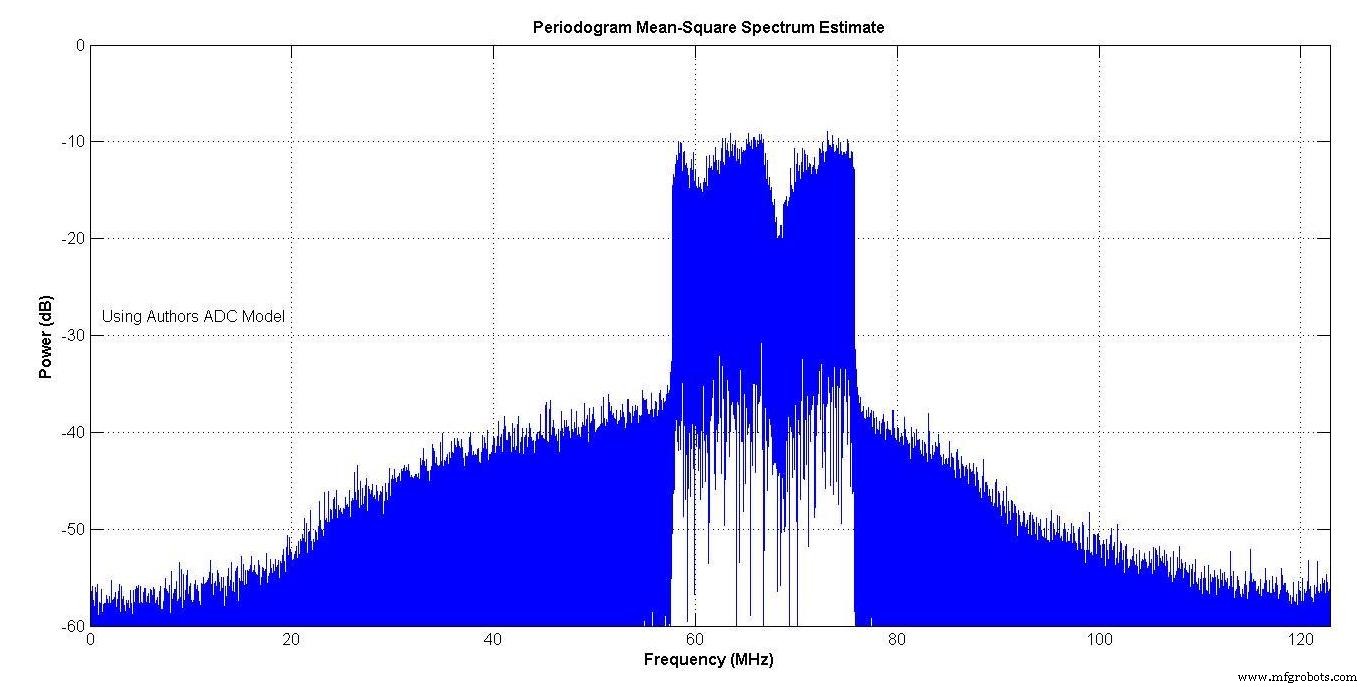

Gambar 12 menunjukkan input sinyal OFDM ke kedua model ADC. Ini berpusat pada frekuensi yang sama dengan dua nada yang ditunjukkan pada Gambar 8.

Gambar 12.

Level dBrmsFS pada kedua model ADC adalah -7 dBrmsFS.

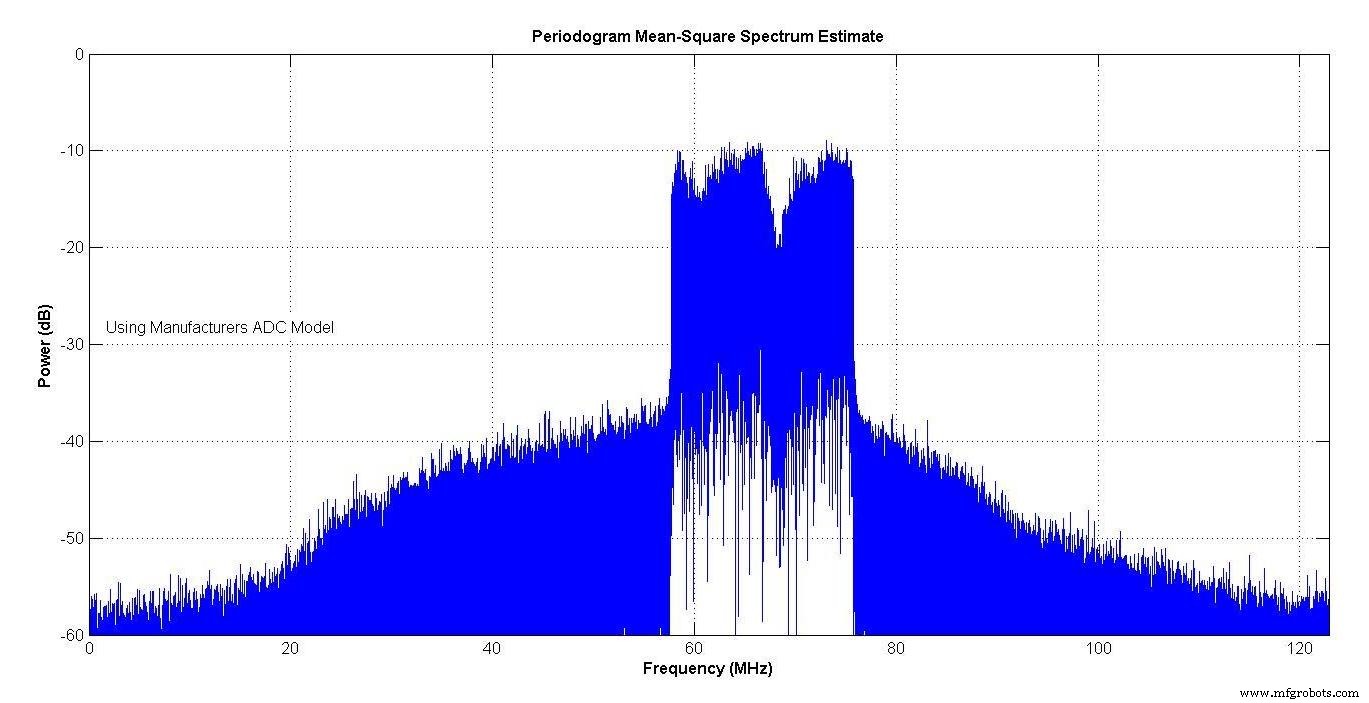

Gambar 13 menunjukkan spektrum model pabrikan, dan Gambar 14 menunjukkan spektrum model penulis Anda. Keduanya menunjukkan pertumbuhan kembali spektral karena non-linier ADC. Spektrumnya sangat dekat.

Gambar 13.

Gambar 14.

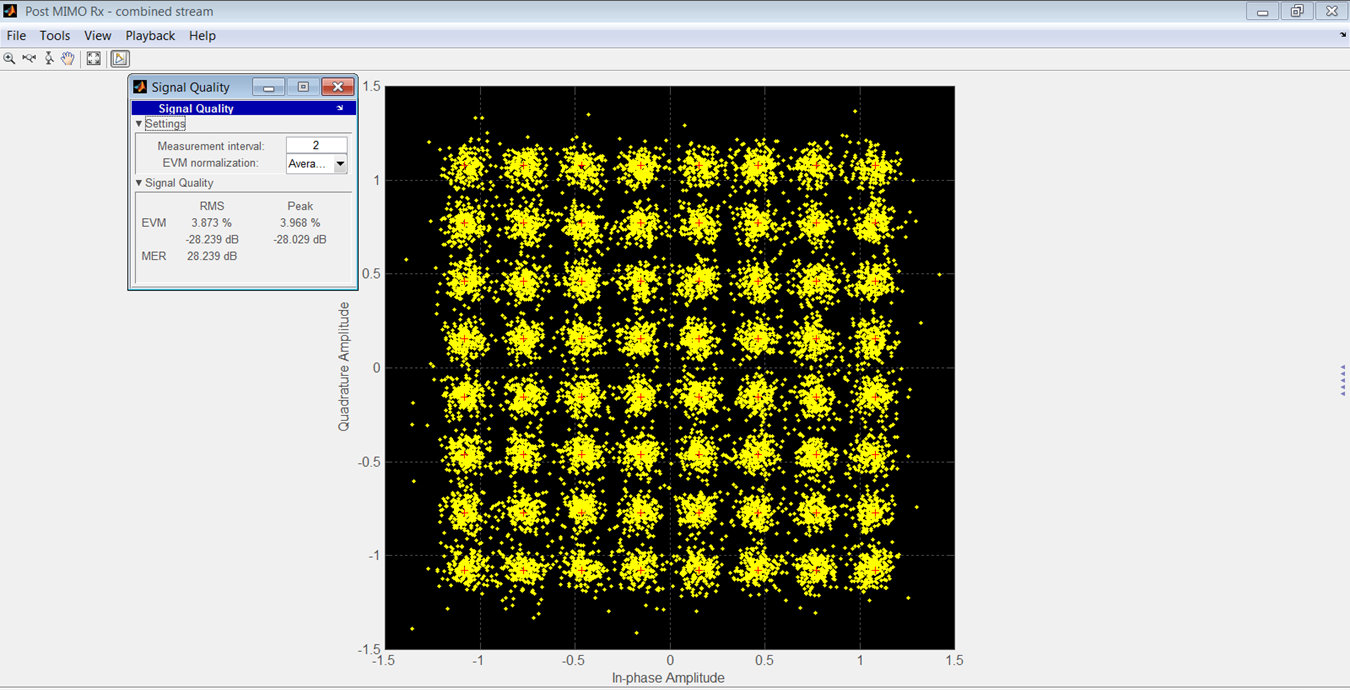

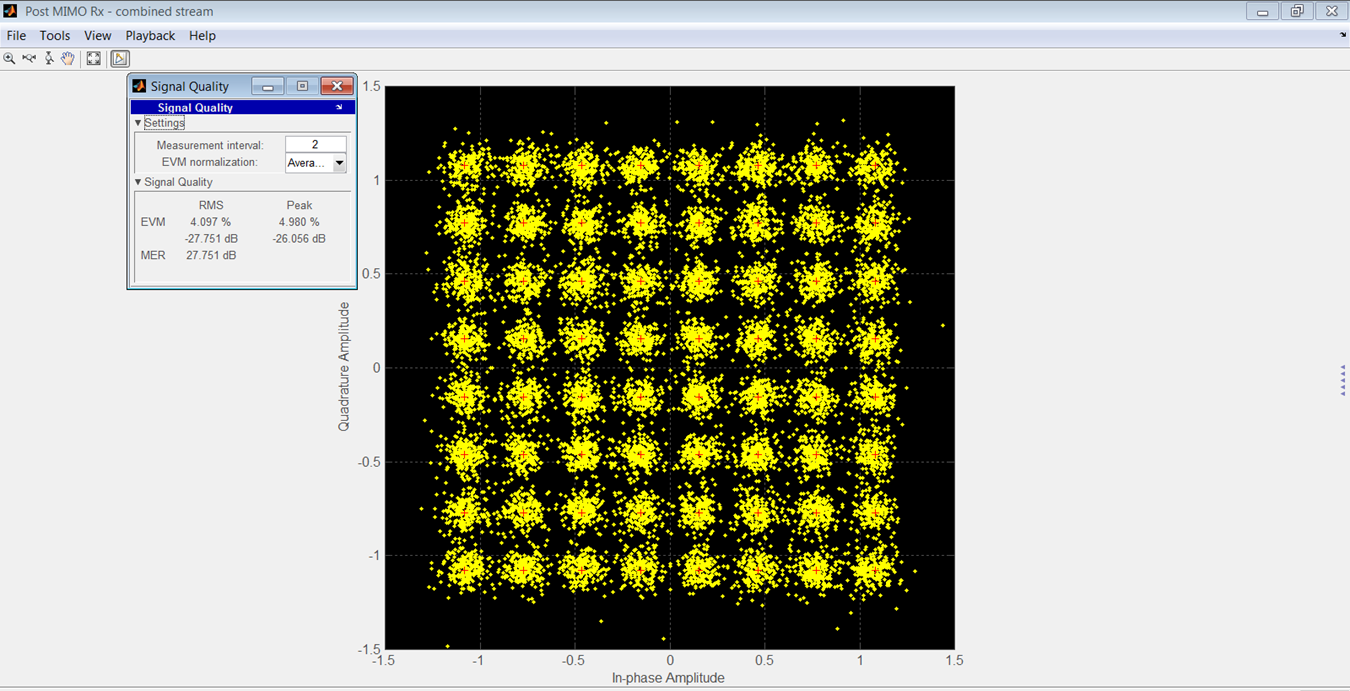

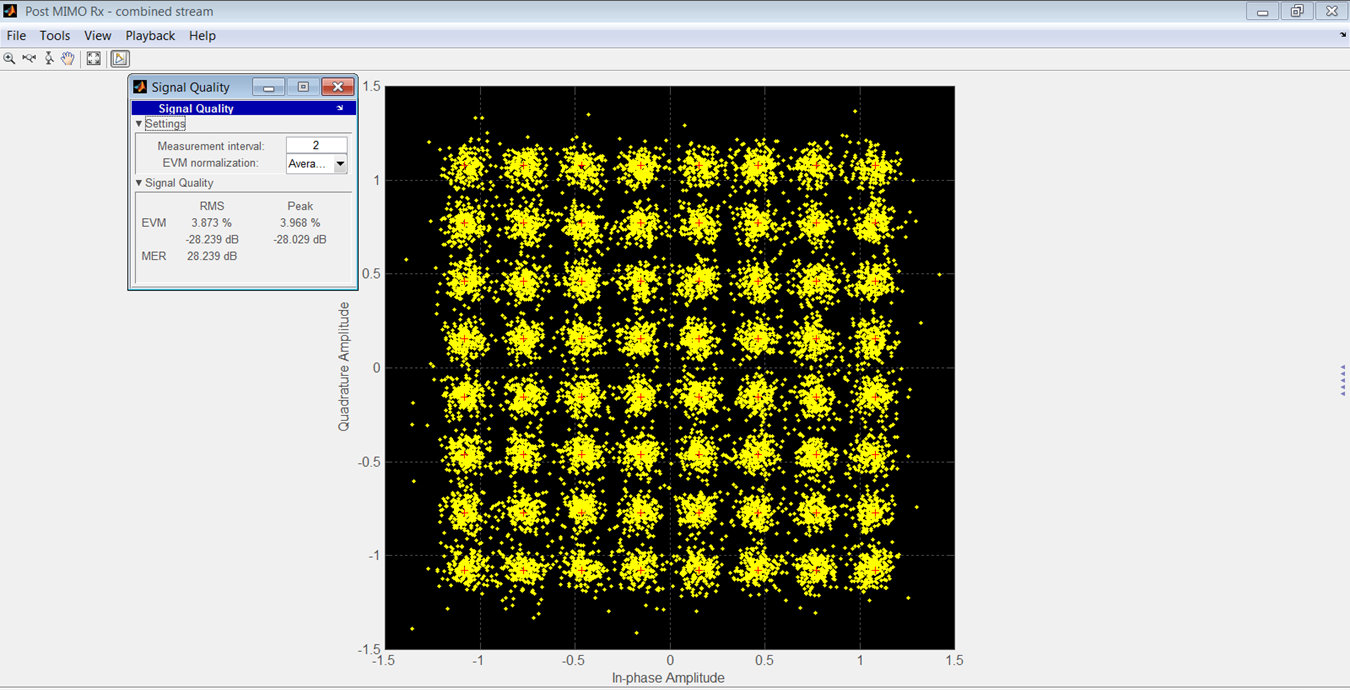

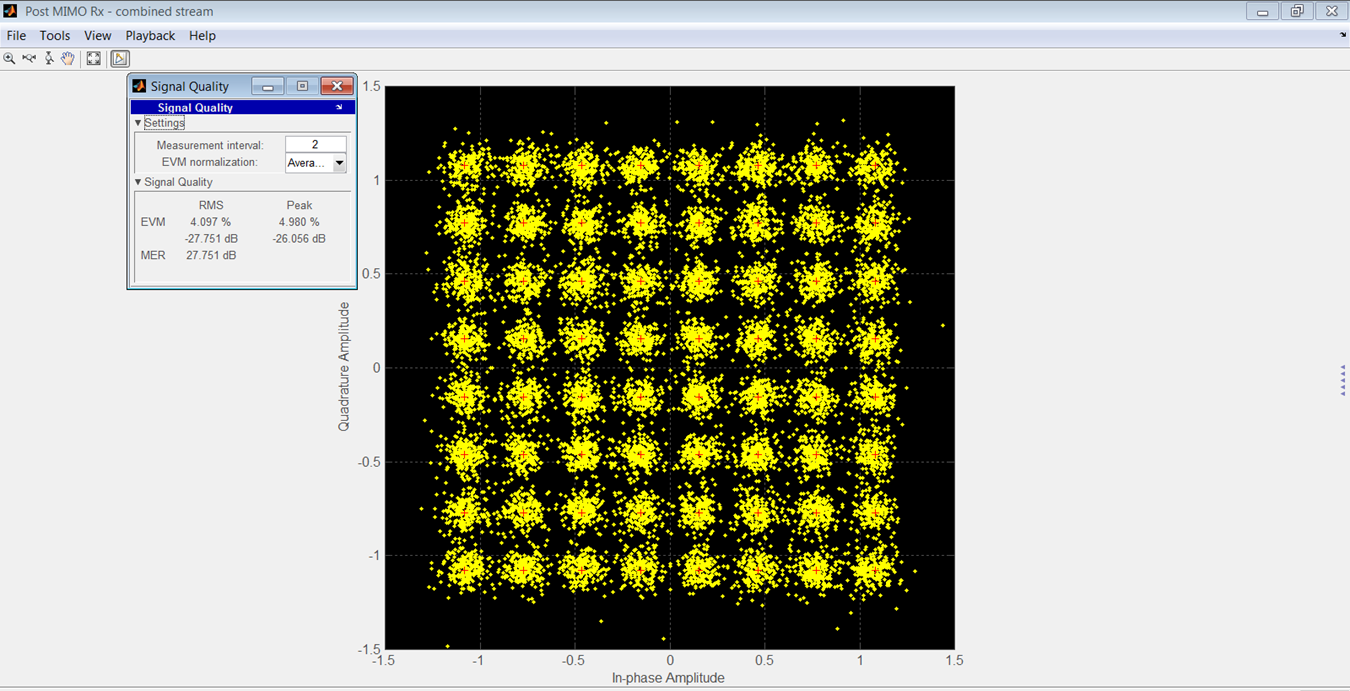

Gambar 15 menunjukkan konstelasi OFDM yang diterima untuk model pabrikan, dan Gambar 16 menunjukkannya untuk model penulis Anda.

Gambar 15.

Gambar 16.

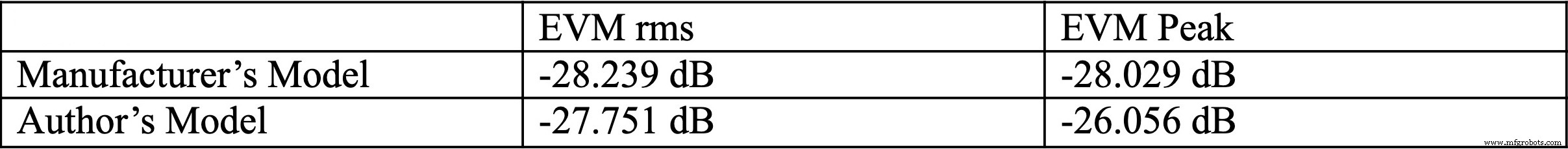

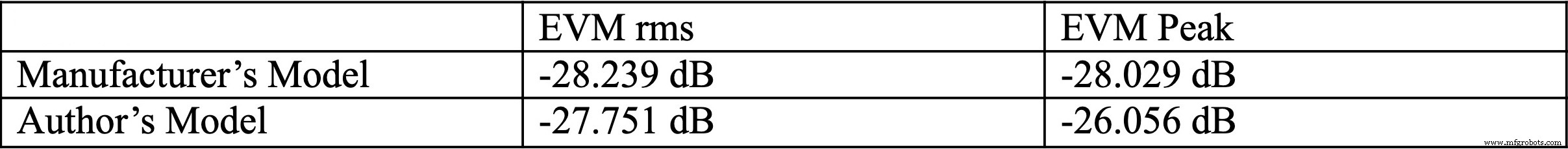

Perbandingan rms dan EVM puncak ada di Tabel 3. SNR adalah 90 dB untuk hasil ini.

Tabel 3.

Pada rentang -7 hingga -47 dBrmsFS, perbedaan rms antara EVM kedua model adalah 3,46 dB.

Secara keseluruhan, model penulis Anda memberikan hasil yang sangat mirip dengan pabrikan, untuk serangkaian parameter yang cukup sederhana. Tidak ada informasi tentang model pabrikan yang tersedia, tetapi mungkin mirip dengan milik penulis Anda.

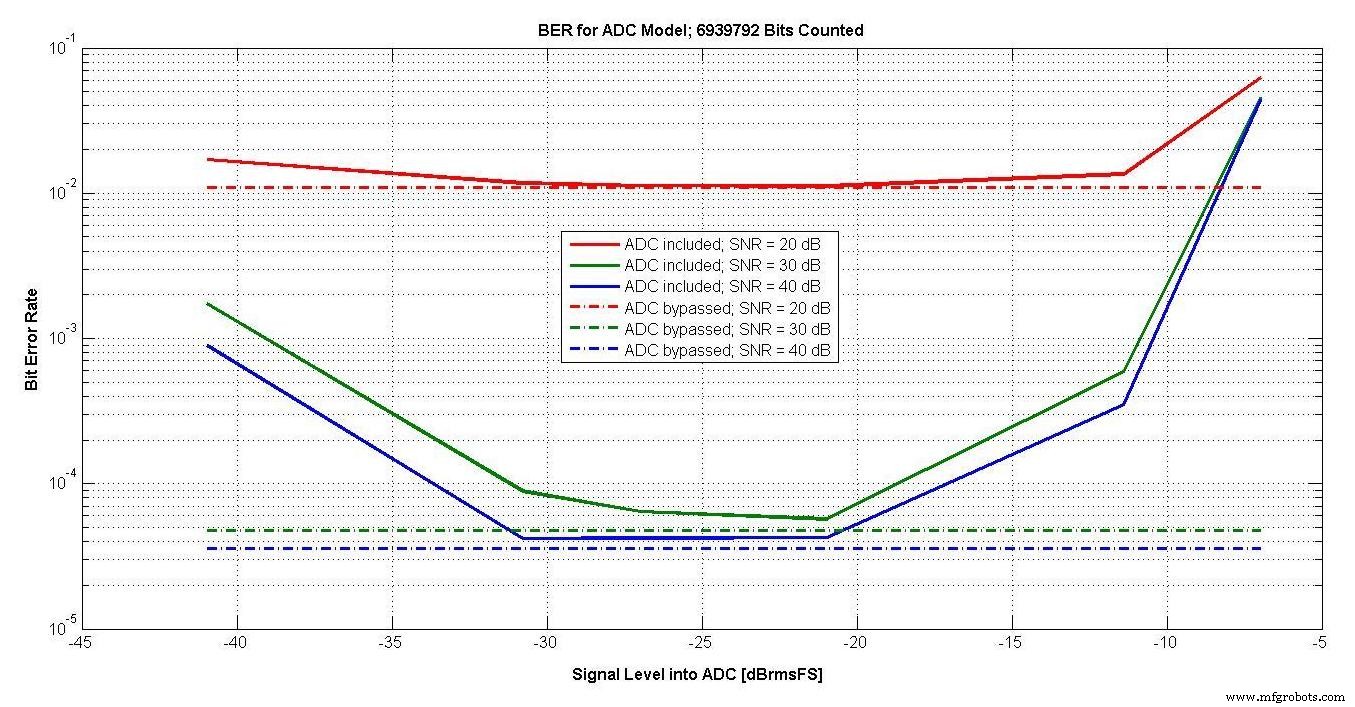

Bagaimanapun, simulasi berjalan lebih cepat saat menggunakan model penulis Anda, karena tidak perlu mentransfer data antar perangkat lunak simulasi. Jadi, model penulis Anda digunakan dalam simulasi bit error rate (BER) yang ditunjukkan pada Gambar 17.

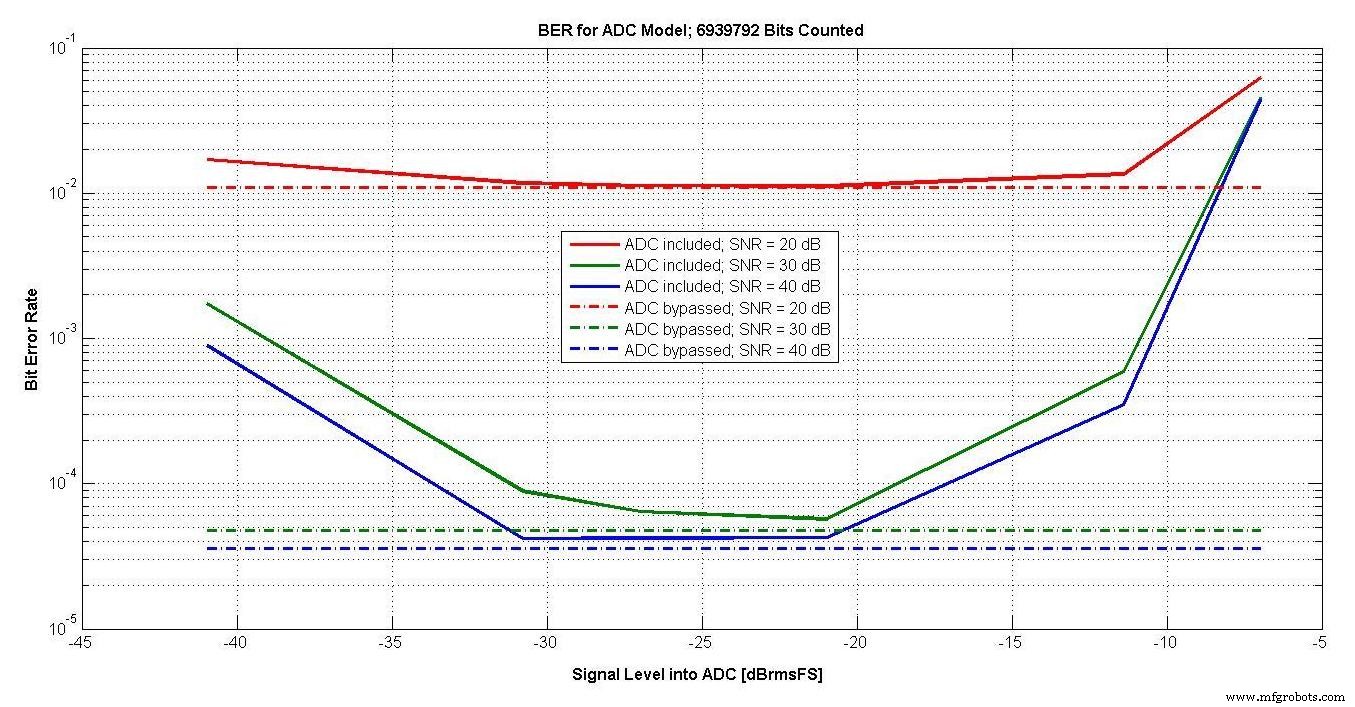

Gambar 17.

Salah satu parameter penting saat merancang sistem dengan ADC adalah level optimal untuk menempatkan sinyal relatif terhadap skala penuh ADC.

Level yang terlalu rendah menyebabkan sinyal menjadi terlalu kecil dibandingkan dengan noise dan distorsi.

Level yang terlalu tinggi menghasilkan kliping yang berlebihan, yang juga mendistorsi sinyal. Biasanya, level yang memungkinkan beberapa kliping adalah optimal.

BER untuk tiga SNR dan level sinyal yang berbeda dari -41 hingga -7 dBrmsFS ditunjukkan pada Gambar 18.

Gambar 18.

Juga ditunjukkan dengan garis putus-putus adalah BER ketika model ADC dilewati. Dengan ADC, ada kisaran 10 dB yang optimal, dan kontrol penguatan otomatis harus menjaga sinyal dalam kisaran ini.

Pada artikel berikutnya, kita akan menyelesaikan seri ini dengan menyimpulkan dengan beberapa pemikiran tentang model yang lebih baik untuk digunakan dan juga berbicara sedikit tentang model untuk DAC. Silakan bagikan pendapat Anda tentang seri ini di komentar di bawah.