Kunci inovasi material hingga 7nm dan seterusnya

Sebagai tim peneliti semikonduktor kami di Albany, NY terus menskalakan teknologi CMOS menuju node masa depan – hingga 10nm, 7nm, dan seterusnya – resistansi saluran transistor yang menentukan aliran arus, dan cara kami menghubungkannya, terus memainkan peran yang semakin signifikan dalam kinerja keseluruhan chip. Jadi untuk memastikan daya saing kinerja teknologi semikonduktor masa depan tertentu, inovasi material saluran untuk mengurangi hambatan saluran transistor adalah bidang studi yang kritis. Itulah sebabnya kami mengeksplorasi silikon germanium (SiGe) – elemen yang diperlukan untuk mencapai manfaat kinerja daya yang diuraikan dalam pengumuman chip 7nm tahun lalu.

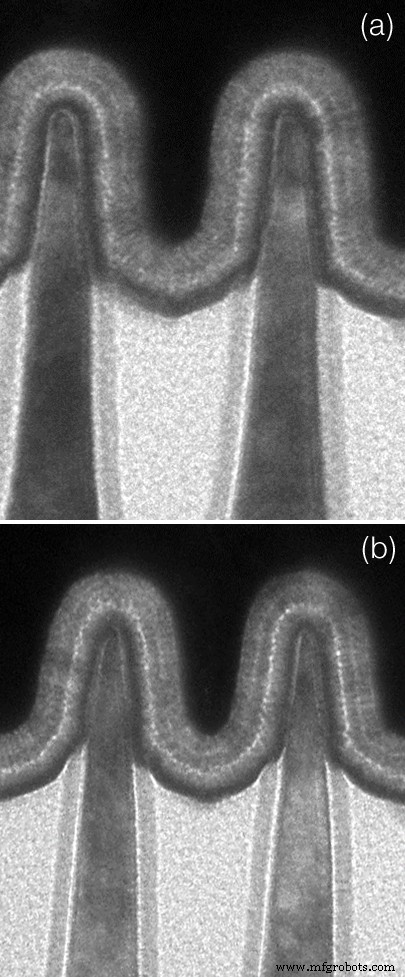

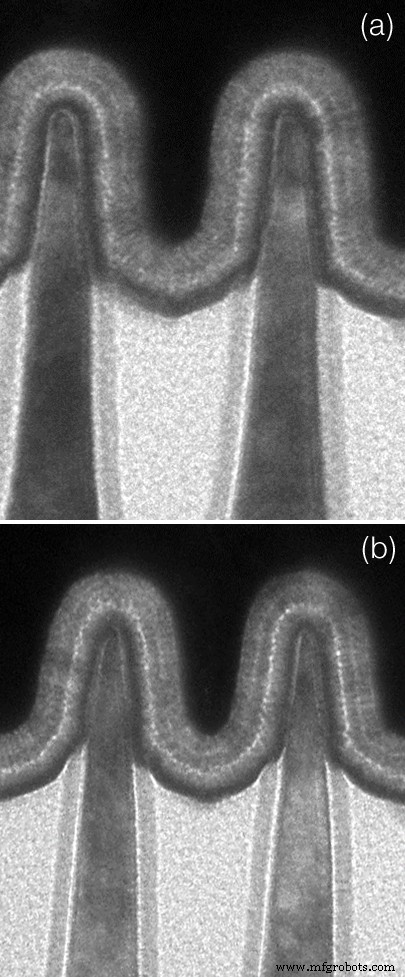

Si simetris Profil FinFET (a) dan SiGe FinFET (b) pada 10nm yang dibuat oleh IBM Research di Kompleks NanoTech SUNY Polytechnic di Albany, NY. Hal ini menggambarkan bahwa SiGe Fin dapat memberikan sifat listrik yang lebih unggul daripada Si Fin.

Chip berbasis FinFET* 14nm node saat ini menggunakan saluran khusus silikon (silikon tidak stabil di luar skala ini). Teknologi FinFET berbasis SiGe, sebagai alternatif, telah menunjukkan peningkatan kinerja dengan aturan dasar teknologi 10nm (standar industri), memberikan solusi elegan menuju opsi teknologi CMOS yang layak. Salah satu solusi SiGe FinFET yang elegan adalah kelonggarannya untuk perangkat berdaya rendah dan berkinerja tinggi pada chip yang sama – tanpa kehilangan kinerja atau variabilitas pada satu jenis perangkat di atas yang lain.

Teknologi SiGe FinFET juga memberikan keandalan listrik yang unggul dibandingkan Si FinFET. Dan ini mengarah pada stabilitas kinerja tingkat chip yang lebih baik daripada Si FinFET selama masa pakai chip. Ini berarti bahwa alur integrasi proses yang identik cocok untuk desain superkomputer serta desain seluler.

SiGe mendorong batas skala chip dengan mengubah cara arus melewati saluran transistor. Ternyata dengan menambahkan atom germanium yang lebih besar ke kristal yang terbuat dari atom silikon yang lebih kecil, kristal mengembangkan ketidakcocokan kisi, menghasilkan ketegangan di saluran transistor. Strain ini memungkinkan untuk memindahkan lebih banyak arus melalui saluran pada tegangan yang lebih rendah. Jadi dengan menggunakan SiGe sebagai materi saluran, kita dapat memetakan peta jalan ke dimensi yang lebih kecil sambil menjaga keseimbangan antara kekuatan dan kinerja.

SiGe untuk node di depan:Memecahkan tantangan dalam memproduksi chip 10nm &7nm

Retensi regangan di seluruh aliran integrasi, bersama dengan kontrol cacat adalah dua tantangan teknis utama untuk memproduksi SiGe FinFET pada node 10nm dan di bawahnya. Saluran transistor bisa kehilangan ketegangan selama proses anil termal yang mengaktifkan dopan dan menstabilkan integritas transistor; atau selama proses reses sumber/pembuangan yang membentuk persimpangan seragam dari atas sirip ke bagian bawah sirip; atau bahkan pola Sirip dalam desain khusus yang membutuhkan Sirip pendek.

Kontrol cacat juga penting dalam produksi massal teknologi CMOS. Dengan ketidakcocokan kisi antara saluran SiGe dan substrat wafer silikonnya, sulit untuk mempertahankan tingkat cacat manufakturabilitas yang diperlukan di seluruh wafer. Namun dengan manajemen pertumbuhan epitaxial (kristal) kami yang canggih, integrasi proses modul Fin yang inovatif, dan rekayasa sumber/pengurasan, kami mengembangkan solusi untuk memastikan ketegangan di saluran di seluruh aliran integrasi, sambil juga mempertahankan cacat rendah dalam pengujian 10nm dan 7nm kami. node.

Dengan studi kelayakan teknologi SiGe FinFET yang komprehensif ini pada aturan dasar teknologi 10nm, kami sekarang bekerja dengan desainer chip dan pembuat chip untuk memproduksi teknologi SiGe FinFET secara massal. Saya mengantisipasi teknologi SiGe FinFET kami akan menggantikan silikon FinFET pada node teknologi CMOS generasi berikutnya untuk penggunaan komputasi, yang mencakup superkomputer hingga perangkat seluler. Mereka juga dapat digunakan dalam aplikasi “lebih dari Moore” I cloud dan komputasi kognitif, di mana catu daya rendah dan konsumsi daya rendah sangat diinginkan, seperti aplikasi di cloud dan komputasi kognitif.

Bacaan lebih lanjut

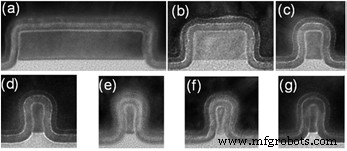

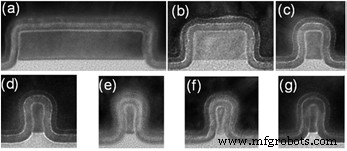

Cross section tumpukan Fin dan gerbang untuk lebar Fin mulai dari 87nm (a) hingga 3nm (g) untuk konten Ge yang lebih tinggi untuk SiGe Fin.

Pada simposium IEEE tahun ini tentang teknologi VLSI (integrasi skala sangat besar), tim kami mempresentasikan sejumlah inovasi perangkat, material, dan integrasi baru yang berpusat pada penggunaan SiGe dengan aturan dasar 10nm, dan juga sebagai jalan ke depan untuk memecahkan penskalaan dan tantangan kinerja node uji 7nm yang kami buat tahun lalu.

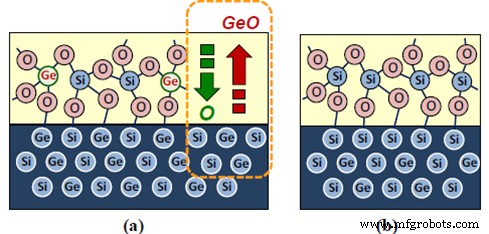

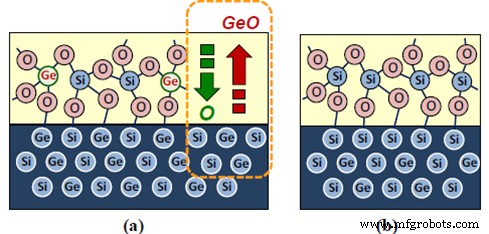

Presentasi kami mencakup fitur teknis penting dan inovasi proses mendasar untuk pengendalian cacat; inovasi dalam gate stack dan lapisan antarmuka yang sesuai untuk SiGe FIN; serta teknik kontak lanjutan pada platform SiGe FinFET, dilaporkan dalam makalah penelitian T2.2 pada konferensi VLSI. Makalah penelitian T4.3 mempresentasikan proses pembersihan germanium oksida selektif yang inventif untuk membangun lapisan antarmuka yang kuat untuk saluran SiGe.

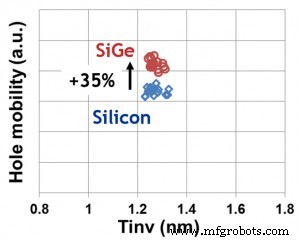

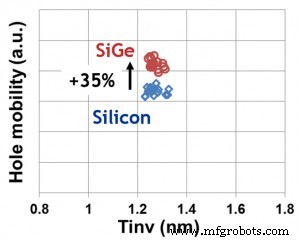

Bersihkan mobilitas manfaat SiGe Fin dibandingkan Si Fin, yang menghasilkan peningkatan kinerja tingkat chip.

Penelitian kami yang dipimpin oleh Dr. Pouya Hashemi yang berfokus pada perluasan teknologi SiGe FinFET untuk node berkinerja lebih tinggi di masa depan juga dipresentasikan di VLSI. Dalam makalah penelitian T9.3, kami melaporkan kelayakan untuk mencapai kinerja yang lebih tinggi dengan konten Ge yang lebih tinggi dan lebar Fin yang lebih kecil serta penskalaan tumpukan gerbang lebih lanjut. Peserta Simposium VLSI dapat menemukan makalah teknis ini di situs web VLSI. Anda juga dapat bergabung dengan Grup Linkedin mereka untuk informasi lebih lanjut.

T2.2:Teknologi FINFET Menampilkan Saluran SiGe Mobilitas Tinggi untuk 10nm dan Lebih Jauh

T4.3:GeO Selektifx -Pemulungan dari Lapisan Antarmuka pada Si1-x Gex Saluran untuk Si/Si Mobilitas Tinggi1-x Gex Aplikasi CMOS

T9.3:Penggantian High-K/Metal-Gate High-Ge-Content Strained FinFET SiGe dengan Mobilitas Lubang Tinggi serta SS dan Keandalan yang Sangat Baik pada EOT Agresif ~7Å dan Dimensi yang Diperkecil hingga Lebar Fin di Bawah 4nm

T7.2:Kontak Silisida Ti dan NiPt/Ti Liner untuk Teknologi Canggih

Skematis proses pencarian GeOx selektif yang inventif (a) dan lapisan antarmuka bebas GeOx (b) dengan saluran SiGe.

*-FinFET mengacu pada arsitektur transistor yang menaikkan saluran transistor sehingga terlihat seperti sirip)

Dechao Guo adalah anggota staf peneliti, penemu utama, dan manajer Desain &Integrasi Perangkat Lanjutan di IBM Research.