IBM di SPIE:Tujuh Kemajuan untuk Chip Lebih dari 7nm

Ketika kami mengumumkan chip uji 7 nanometer node (7nm) fungsional pertama di industri pada tahun 2015, dengan GLOBALFOUNDRIES dan mitra Samsung kami, kami tahu proses chip untuk mencapai "kematangan manufaktur" – mungkin pada awal tahun depan, akan berlangsung cepat. Seiring dengan percepatan upaya di industri semikonduktor, IBM terus mendorong batas dengan berfokus pada tantangan node berikutnya di luar 7nm.

Tim IBM kami sedang mempresentasikan tujuh makalah pada konferensi International Society for Optics and Photonics (SPIE) Advanced Lithography 2017 minggu ini berfokus pada eksplorasi dan pemberdayaan teknologi di luar node 7nm. Dan itu dimulai dengan Litografi Ultraviolet Ekstrim (EUV).

Tim IBM kami sedang mempresentasikan tujuh makalah pada konferensi International Society for Optics and Photonics (SPIE) Advanced Lithography 2017 minggu ini berfokus pada eksplorasi dan pemberdayaan teknologi di luar node 7nm. Dan itu dimulai dengan Litografi Ultraviolet Ekstrim (EUV).

Dengan chip 7nm, kami sekarang membuat desain yang berkaitan dengan ukuran transistor, atau bahkan kabel antar transistor, yang benar-benar pada tingkat atom. Untuk mencapai penskalaan semacam ini tanpa skema pola yang terlalu rumit, EUV adalah kuncinya. Dalam eksposur tunggal, EUV dapat membuat pola resolusi tinggi yang tidak dapat dicapai oleh proses pola semikonduktor sebelumnya. Namun, mengaktifkan pola EUV memerlukan peralatan, proses, dan pengetahuan khusus, semua ditemukan di laboratorium penelitian IBM di Albany, NY dan Yorktown Heights, NY. Ketujuh kemajuan yang dipresentasikan di SPIE berkaitan dengan masker EUV (templat yang digunakan untuk mencetak desain sirkuit ke wafer silikon), dan bahan pola (bahan "tahan" atau tahan etsa yang diaktifkan dengan cahaya), semuanya dapat dianggap penting dalam memungkinkan teknologi 7nm dan seterusnya:

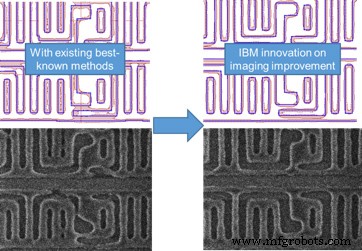

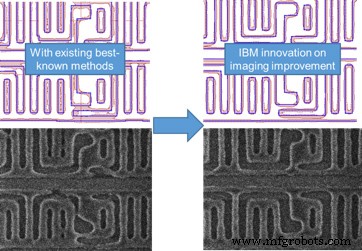

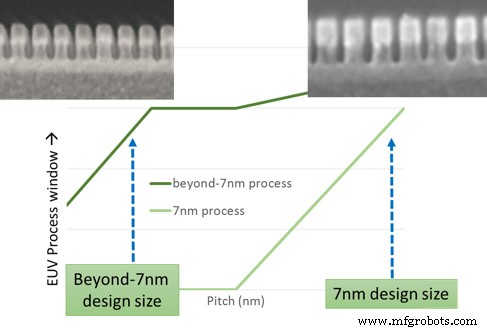

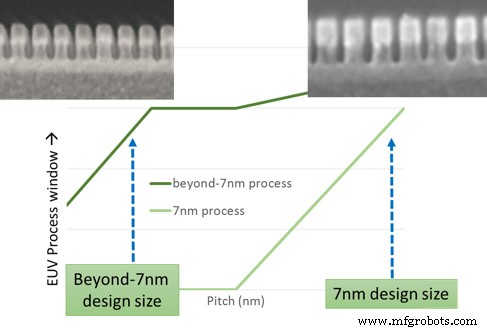

Dalam Optimasi maksud desain pada node 7nm di luar:Persimpangan teknik mitigasi stokastik DTCO dan EUVL , Michael Crouse menunjukkan bahwa meskipun judul pidatonya besar, perubahan kecil dalam desain kabel dapat secara drastis meningkatkan kondisi pencetakan. Pada Gambar 1, ia menunjukkan bahwa jika optimasi bentuk topeng dilakukan dengan benar, garis kontinu tanpa putus dapat dicetak pada dimensi terkecil yang diperlukan untuk node 7nm dan seterusnya.

Gambar 1 :Peningkatan optimasi kontras pada kabel logam dua dimensi yang ditunjukkan dengan litografi EUV. Dengan jenis peningkatan yang diilustrasikan di sebelah kanan, fitur 20-30{ccf696850f4de51e8cea028aa388d2d2d2eef894571ad33a4aa3b26b43009887} yang lebih kecil daripada yang berasal dari node 7nm dapat dicetak lebih kuat, dan variabilitas fisik/listrik dapat dikurangi secara drastis.

Dalam Investigasi tumpukan topeng alternatif dalam litografi EUV, Martin Burkhardt mensimulasikan kinerja bahan baru yang saat ini tidak digunakan untuk masker EUV. Dengan mempertimbangkan seluruh tabel periodik, ia dapat menggambarkan bahwa topeng EUV yang memberikan kontras yang lebih baik berada dalam jangkauan kita. Sebenarnya pembuatan masker dengan beberapa bahan ini akan memungkinkan pola fidelitas yang lebih tinggi pada wafer silikon tanpa perubahan lebih lanjut dalam teknologi EUV, dan dengan demikian memungkinkan industri untuk menskalakan dengan mudah di luar 7nm.

Dalam Analisis komprehensif tepi garis dan kekasaran lebar garis untuk litografi EUV , Ravi Bonam mengilustrasikan bagaimana ketidaksempurnaan kecil dan goyangan dalam saluran kabel dapat dicirikan dengan jelas, dan dengan demikian menunjukkan kondisi mana yang menghasilkan fitur paling lurus, yang penting untuk meningkatkan kemampuan manufaktur proses pembuatan pola EUV, serta kinerja dan hasil chip.

Dalam Dasar-dasar interaksi hardmask tahan-anorganik EUV , Dario Goldfarb berupaya memperbaiki tumpukan film bahan pola (titik transfer dari pola ke wafer) dengan meningkatkan interaksi fisik dan kimia pada antarmuka antara film-film ini, yang seringkali tidak suka menempel satu sama lain. Dia memanfaatkan pemahaman ini untuk menciptakan interaksi kimia spesifik untuk menyatukan bahan-bahan ini (ditunjukkan pada Gambar 2), yang sangat penting untuk memastikan bentuk kecil berpola EUV ini dapat bertahan cukup lama untuk mentransfer polanya ke substrat di bawahnya.

Gambar 2 :Tahanan EUV yang sebelumnya tidak mungkin dipolakan pada hardmask silikon anorganik sekarang dapat dipola dengan jelas setelah penyesuaian permukaan yang disesuaikan dengan kombinasi penahan/hardmask.

Dalam tema yang mirip dengan ceramah Dario Goldfarb, Indira Seshadri mendemonstrasikan dalam tumpukan pola Ultrathin EUV menggunakan sikat polimer sebagai lapisan promosi adhesi , bahwa dengan menggunakan bahan seperti polimer yang menjembatani antara fitur kecil berpola EUV dan substrat di bawahnya, pola resolusi sangat tinggi ini dapat diukir ke substrat di bawah dan mempertahankan bentuk desain yang diinginkan, kunci untuk memastikan chip yang dapat dihasilkan pada panjang ini timbangan.

Dengan begitu banyak solusi film tipis baru yang sedang dimainkan, kemampuan untuk membedakan dan meningkatkan proses yang layak manufaktur di awal fase penelitian adalah kuncinya. Dalam ceramah berjudul Menurunkan kepadatan cacat dalam tumpukan film berpola EUV komposit , Luciana Meli mendemonstrasikan studi kasus sistematis, menggunakan gabungan teknik pemeriksaan cacat yang tersedia, untuk menunjukkan proses dan peningkatan bahan yang diperlukan untuk menghasilkan cacat rendah yang diperlukan untuk 7nm dan di luar kemampuan manufaktur EUV.

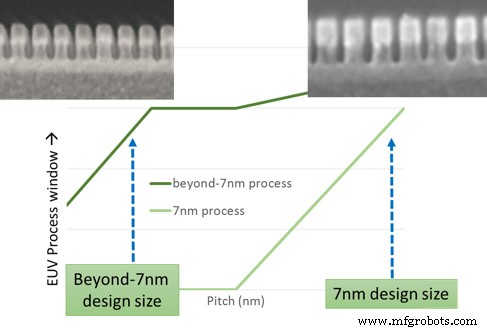

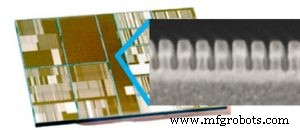

Menggabungkan banyak dari konsep pencitraan dan peningkatan material ini, Anuja De Silva akan menyajikan ceramah berjudul Pengembangan pola paparan tunggal untuk litografi EUV , menampilkan pola sukses rangkaian kabel pada dimensi 30nm dan di bawah yang diperlukan di luar node 7nm. Kemampuan untuk mencapai ini merupakan lompatan besar dari kemampuan pertama yang tersedia untuk node 7nm (lihat Gambar 3), dan sebenarnya dapat meningkatkan node 7nm itu sendiri, meskipun dia akan menyoroti tantangan yang masih ada untuk memungkinkan chip yang berfungsi penuh dan dapat dihasilkan di dimensi yang diperlukan untuk teknologi di luar 7nm.

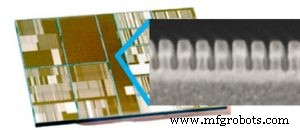

Sebuah chip 7nm memiliki 20 miliar transistor di ruang kira-kira seukuran kuku. Mereka akan masuk ke sistem dan perangkat, memperluas kemampuan – dan Hukum Moore – untuk melakukan tugas yang semakin menuntut dalam analisis data, komputasi kognitif, dan apa pun yang dimiliki oleh aplikasi seluler generasi berikutnya. Pekerjaan yang dipresentasikan di SPIE tahun ini mendorong industri lebih dekat ke solusi pola yang tidak hanya membuat proses 7nm lebih kuat dengan EUV paparan tunggal, mereka juga memungkinkan penskalaan lebih lanjut untuk mewujudkan manfaat daya/kinerja yang lebih besar untuk tahun-tahun mendatang.

Gambar 3 :Inovasi pada berbagai aspek proses pemolaan memungkinkan IBM untuk memberikan kemampuan proses pemolaan holistik dalam memberikan ukuran fitur yang diperlukan di luar node 7nm.

Presentasi IBM Lainnya di SPIE 2017

Optimasi maksud desain pada node 7nm di luar:Persimpangan teknik mitigasi stokastik DTCO dan EUVL , Michael Crouse, Nicole Saulnier, Derren Dunn

Investigasi tumpukan topeng alternatif dalam litografi EUV , Martin Burkhardt

Dekomposisi TCC menggunakan kernel yang tidak koheren untuk penghitungan gambar litografi yang lebih cepat, Alan Rosenbluth

Pengembangan Ti yang mengandung hardmask melalui deposisi PEALD, Anuja De Silva

Opsi pola DSA untuk logika dan aplikasi memori, Charlie Liu

Studi listrik dari proses penyusutan DSA dan efek perbaikan CD pada sub-60nm menggunakan kendaraan uji EUV, Cheng Chi

Mencapai Overlay Sejati di Node Lanjutan, Chiew-Seng Koay

Strategi Bebas Lapisan Atas untuk Kontrol Orientasi Kopolimer Blok Tinggi Semua Organik, Dan Sanders

Identifikasi dan analisis sensitivitas keandalan dari sistem aturan dasar yang berkorelasi (busur desain), Eric Eastman

Pengembangan dan kalibrasi model DSA 3D yang cepat dan canggih untuk pengoptimalan bersama teknologi desain, Kafai Lai

Dampak Tak Terduga dari Gas RIE pada Film Litografi, Martin Glodde

Prediksi Uji Listrik menggunakan Metrologi Hibrid dan Pembelajaran Mesin, Mary Breton

Mengurangi LER dalam Si dan SiN Melalui Optimasi RIE untuk Aplikasi Photonic Waveguide, Nathan Marchack

Strategi Pola Perakitan Diri Terarah untuk Aplikasi Memori Perubahan Fase, R.Bruce

Karakterisasi material untuk proses integrasi perangkat gerbang multi-saluran di sekeliling (GAA), Raja Muthinti

Analisis komprehensif kekasaran garis tepi dan lebar garis untuk litografi EUV, Ravi Bonam

Tim IBM kami sedang mempresentasikan tujuh makalah pada konferensi International Society for Optics and Photonics (SPIE) Advanced Lithography 2017 minggu ini berfokus pada eksplorasi dan pemberdayaan teknologi di luar node 7nm. Dan itu dimulai dengan Litografi Ultraviolet Ekstrim (EUV).

Tim IBM kami sedang mempresentasikan tujuh makalah pada konferensi International Society for Optics and Photonics (SPIE) Advanced Lithography 2017 minggu ini berfokus pada eksplorasi dan pemberdayaan teknologi di luar node 7nm. Dan itu dimulai dengan Litografi Ultraviolet Ekstrim (EUV).