Teknologi Industri

Shift register paralel-in/ serial-out melakukan semua yang dilakukan oleh register geser serial-in/ serial-out sebelumnya ditambah input data ke semua tahapan secara bersamaan.

Register geser paralel-in/serial-out menyimpan data, menggesernya berdasarkan jam demi jam, dan menundanya berdasarkan jumlah tahapan dikalikan periode jam.

Selain itu, parallel-in/ serial-out benar-benar berarti bahwa kita dapat memuat data secara paralel ke semua tahapan sebelum pemindahan dimulai.

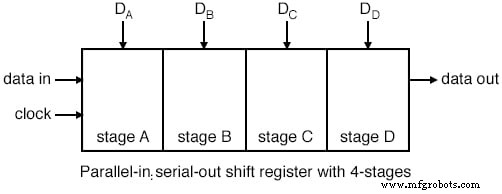

Ini adalah cara untuk mengonversi data dari paralel format ke serial format. Dengan format paralel yang kami maksud adalah bahwa bit data hadir secara bersamaan pada masing-masing kabel, satu untuk setiap bit data seperti yang ditunjukkan di bawah ini.

Dengan format serial yang kami maksud adalah bahwa bit data disajikan secara berurutan dalam waktu pada satu kabel atau sirkuit seperti dalam kasus "data keluar" pada diagram blok di bawah ini.

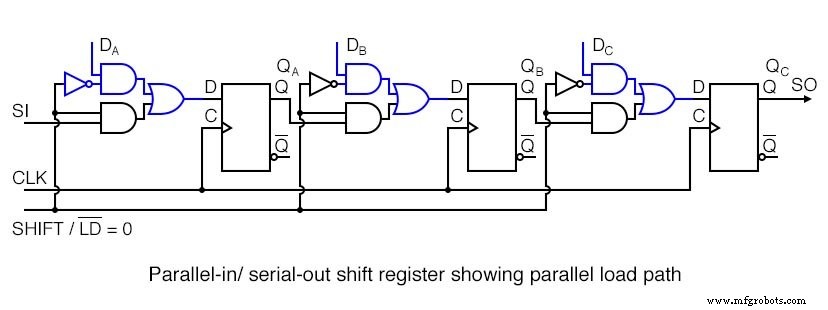

Di bawah ini kita melihat dari dekat detail internal dari register geser 3-tahap masuk/seri-keluar.

Panggung terdiri dari tipe D Flip-Flop untuk penyimpanan, dan pemilih DAN-ATAU untuk menentukan apakah data akan dimuat secara paralel, atau menggeser data yang disimpan ke kanan.

Secara umum, elemen-elemen ini akan direplikasi untuk jumlah tahapan yang diperlukan. Kami menampilkan tiga tahap karena keterbatasan ruang.

Empat, delapan atau enam belas bit normal untuk bagian nyata.

Di atas kami menunjukkan jalur beban paralel ketika SHIFT/LD' berlogika rendah. Gerbang NAND atas melayani DA DB DC diaktifkan, meneruskan data ke input D tipe D Flip-Flop TA TB DC masing-masing.

Pada tepi clock positif berikutnya, data akan di-clock dari D ke Q dari tiga FF. Tiga bit data akan dimuat ke QA TB DC pada saat yang sama.

Jenis beban paralel yang baru saja dijelaskan, di mana beban data pada pulsa clock dikenal sebagai beban sinkron karena pemuatan data disinkronkan dengan jam.

Ini perlu dibedakan dari beban asinkron di mana pemuatan dikendalikan oleh pin yang telah ditetapkan sebelumnya dan jelas dari Flip-Flops yang tidak memerlukan jam.

Hanya satu dari metode pemuatan ini yang digunakan dalam satu perangkat, beban sinkron lebih umum di perangkat yang lebih baru.

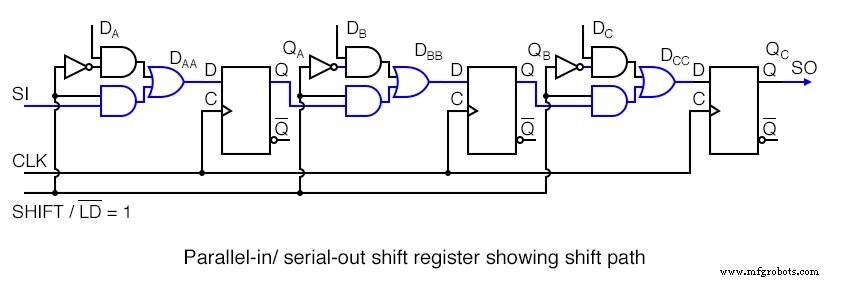

Jalur pergeseran ditunjukkan di atas saat SHIFT/LD' berlogika tinggi. Gerbang AND yang lebih rendah dari pasangan yang memberi makan gerbang OR diaktifkan memberi kita koneksi register geser SI ke DA , TA ke DB , TB ke DC , TC untuk SO. Pulsa clock akan menyebabkan data digeser ke kanan ke SO pada pulsa yang berurutan.

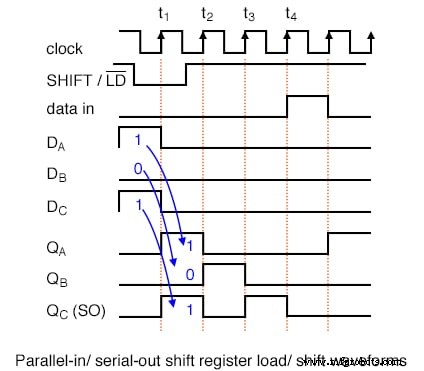

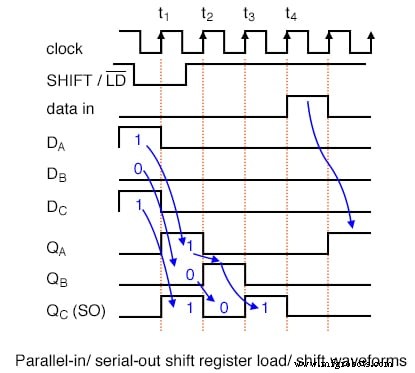

Bentuk gelombang di bawah ini menunjukkan pemuatan paralel dari tiga bit data dan pemindahan serial data ini. Data paralel di DA DB DC diubah menjadi data serial di SO.

Apa yang sebelumnya kami jelaskan dengan kata-kata untuk pemuatan dan pemindahan paralel sekarang ditetapkan sebagai bentuk gelombang di atas.

Sebagai contoh kami menyajikan 101 ke input paralel DAA DBB DCC . Selanjutnya, SHIFT/LD' menjadi rendah sehingga memungkinkan pemuatan data sebagai lawan dari pemindahan data.

Perlu waktu singkat sebelum dan sesudah pulsa clock karena persyaratan pengaturan dan penahanan. Ini jauh lebih lebar dari yang seharusnya.

Padahal, dengan logika sinkron akan lebih mudah untuk membuatnya lebar. Kita bisa membuat SHIFT/LD aktif rendah lebar hampir dua jam, rendah hampir satu jam sebelum t1 dan kembali tinggi tepat sebelum t3 .

Faktor penting adalah bahwa itu harus rendah sekitar waktu jam t1 untuk mengaktifkan pemuatan data secara paralel per jam.

Perhatikan bahwa pada t1 data 101 di DA DB DC di-clock dari D ke Q Flip-Flops seperti yang ditunjukkan pada QA TB TC pada waktu t1 .

Ini adalah pemuatan paralel data yang sinkron dengan jam.

Sekarang setelah data dimuat, kami dapat menggesernya asalkan SHIFT/LD' tinggi untuk memungkinkan pemindahan, yang sebelum t2 .

Pada t2 data 0 di QC digeser keluar dari SO yang sama dengan QC bentuk gelombang Itu dialihkan ke sirkuit terintegrasi lain, atau hilang jika tidak ada yang terhubung ke SO.

Data di QB , a 0 digeser ke QC . 1 di TA digeser ke QB . Dengan “data dalam” a 0 , TA menjadi 0 . Setelah t2 , TA TB TC =010 .

Setelah t3 , TA TB TC =001 . 1 . ini , yang awalnya hadir di QA setelah t1 , sekarang hadir di SO dan QC .

Bit data terakhir digeser ke sirkuit terintegrasi eksternal jika ada. Setelah t4 semua data dari beban paralel hilang.

Pada jam t5 kami menunjukkan pergeseran data 1 hadir di SI, masukan serial.

T:Mengapa menyediakan pin SI dan SO pada register geser?

A:Koneksi ini memungkinkan kita untuk mengalirkan tahapan register geser untuk menyediakan shifter yang lebih besar daripada yang tersedia dalam satu paket IC (Integrated Circuit). Mereka juga memungkinkan koneksi serial ke dan dari IC lain seperti mikroprosesor.

Mari kita lihat lebih dekat register geser paralel-in/serial-out yang tersedia sebagai sirkuit terintegrasi, milik Texas Instruments.

Untuk lembar data perangkat lengkap, ikuti tautan ini.

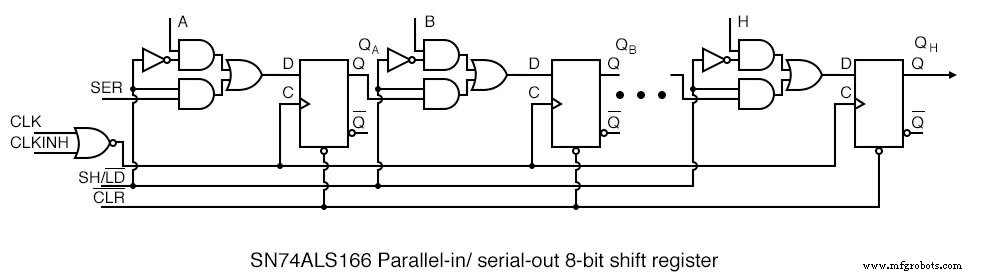

SN74ALS166 yang ditunjukkan di atas adalah kecocokan terdekat dari bagian aktual dengan angka shifter keluar/masuk paralel sebelumnya.

Mari kita perhatikan perubahan kecil pada gambar kita di atas. Pertama-tama, ada 8 tahap. Kami hanya menampilkan tiga.

Semua 8-tahap ditampilkan pada lembar data yang tersedia di tautan di atas. Pabrikan melabeli input data A, B, C, dan seterusnya ke H.

Kontrol SHIFT/LOAD disebut SH/LD’. Ini disingkat dari terminologi kami sebelumnya, tetapi bekerja dengan cara yang sama:beban paralel jika rendah, geser jika tinggi.

Input shift (data serial masuk) adalah SER pada ALS166, bukan SI. Jam CLK dikendalikan oleh sinyal penghambat, CLKINH.

Jika CLKINH tinggi, jam dihambat, atau dinonaktifkan. Jika tidak, "bagian nyata" ini sama dengan apa yang telah kita lihat secara detail.

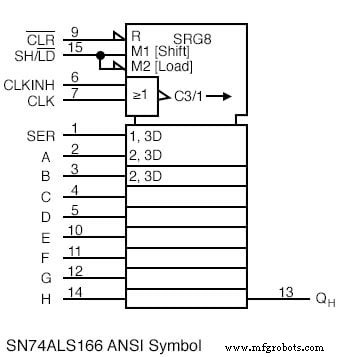

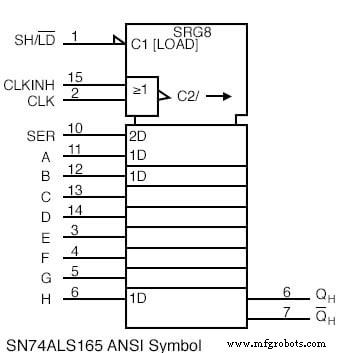

Di atas adalah simbol ANSI (American National Standards Institute) untuk SN74ALS166 seperti yang tertera pada lembar data.

Setelah kita tahu bagaimana bagian itu beroperasi, akan lebih mudah untuk menyembunyikan detailnya di dalam simbol. Ada banyak bentuk umum dari simbol.

Keuntungan dari simbol ANSI adalah labelnya memberikan petunjuk tentang bagaimana bagian tersebut beroperasi.

Blok berlekuk besar di bagian atas '74ASL166 adalah bagian kontrol dari simbol ANSI. Ada penyetelan ulang yang didakwakan oleh R .

Ada tiga sinyal kontrol:M1 (Shift), M2 (Muat), dan C3/1 (panah) (jam terhambat). Jam memiliki dua fungsi.

Pertama, C3 untuk menggeser data paralel di mana pun awalan 3 muncul. Kedua, kapan pun M1 ditegaskan, seperti yang ditunjukkan oleh 1 dari C3/1 (panah) , data digeser seperti yang ditunjukkan oleh panah penunjuk kanan.

Garis miring (/) adalah pemisah antara dua fungsi ini. Tahap 8 shift, seperti yang ditunjukkan oleh judul SRG8 , diidentifikasi oleh input eksternal A, B, C, ke H .

2, 3D internal internal menunjukkan data itu, D , dikendalikan oleh M2 [Muat] dan C3 jam. Dalam hal ini, kita dapat menyimpulkan bahwa data paralel dimuat secara sinkron dengan jam C3 .

Panggung atas di A adalah blok yang lebih lebar dari yang lain untuk mengakomodasi input SER .

Legenda 1, 3D menyiratkan bahwa SER dikendalikan oleh M1 [Shift] dan C3 jam. Jadi, kami berharap untuk mencatat data di SER saat menggeser sebagai lawan dari pemuatan paralel.

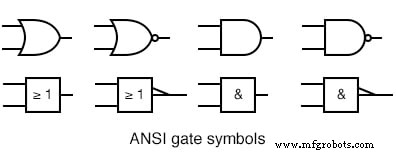

Gerbang dasar ANSI/IEEE simbol persegi panjang disediakan di atas untuk perbandingan dengan simbol bentuk yang lebih dikenal sehingga kami dapat menguraikan makna simbologi yang terkait dengan CLKIN H dan CLK pin pada simbol ANSI SN74ALS166 sebelumnya.

CLK dan CLKINH memberi umpan ATAU gerbang pada simbol SN74ALS166 ANSI. ATAU ditunjukkan oleh => pada simbol sisipan persegi panjang.

Segitiga panjang pada output menunjukkan jam. Jika ada gelembung dengan panah, ini akan menunjukkan pergeseran pada tepi jam negatif (tinggi ke rendah).

Karena tidak ada gelembung dengan panah jam, register bergeser pada tepi jam positif (transisi rendah ke tinggi).

Panah panjang, setelah legenda C3/1 menunjuk ke kanan menunjukkan shift ke kanan, yang merupakan simbol ke bawah.

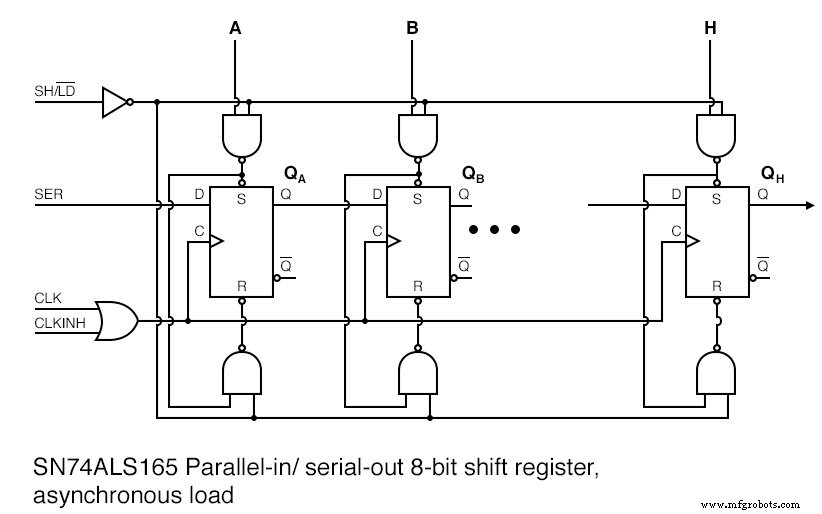

Bagian dari logika internal SN74ALS165 paralel-in/ serial-out, register pemindah beban asinkron direproduksi dari lembar data di atas.

Lihat tautan di awal bagian ini untuk diagram lengkapnya. Kami belum melihat pemuatan data yang tidak sinkron hingga saat ini.

Pertama-tama, pemuatan dilakukan dengan penerapan sinyal yang sesuai ke Set (preset) dan Setel Ulang (menghapus) masukan Flip-Flop.

Bagian atas NAND gerbang memberi makan Set pin FF dan juga mengalir ke NAND lower yang lebih rendah gerbang memberi makan Reset pin FF.

NAND lower yang lebih rendah gerbang membalikkan sinyal masuk dari Set sematkan ke Setel Ulang pin.

Pertama, SH/LD' harus ditarik Rendah untuk mengaktifkan bagian atas dan bawah NAND gerbang.

Jika SH/LD' berada pada logika tinggi sebagai gantinya, inverter memberi makan logika rendah untuk semua NAND gerbang akan memaksa Tinggi keluar, melepaskan "aktif rendah" Setel dan Setel Ulang pin dari semua FF.

Tidak mungkin memuat FF.

Dengan SH/LD' ditahan Rendah , kita dapat memberi makan, misalnya, data 1 ke input paralel A , yang membalik ke nol di bagian atas NAND keluaran gerbang, menyetel FF QA ke 1 .

0 di Setel pin diumpankan ke NAND lower yang lebih rendah gerbang yang dibalik menjadi 1 , melepaskan Setel Ulang pin QA .

Jadi, sebuah data A=1 set QA =1 . Karena semua ini tidak memerlukan jam, pemuatan tidak sinkron sehubungan dengan jam.

Kami menggunakan register geser pemuatan asinkron jika kami tidak dapat menunggu jam untuk memuat data secara paralel, atau jika tidak nyaman untuk menghasilkan satu pulsa clock.

Satu-satunya perbedaan dalam memasukkan data 0 ke input paralel A apakah itu terbalik menjadi 1 keluar dari gerbang atas melepaskan Set .

1 . ini di Setel dibalik menjadi 0 di gerbang bawah, menarik Reset ke Rendah , yang menyetel ulang QA =0 .

Simbol ANSI untuk SN74ALS166 di atas memiliki dua kontrol internal C1 [LOAD] dan C2 jam dari ATAU fungsi dari (CLKINH, CLK ).

SRG8 kata shifter 8 tahap. Panah setelah C2 menunjukkan pergeseran ke kanan atau ke bawah. SER input adalah fungsi jam seperti yang ditunjukkan oleh label internal 2D .

Input data paralel A, B, C ke H adalah fungsi dari C1 [LOAD], ditunjukkan oleh label internal 1D .

C1 ditegaskan ketika sh/LD’ =0 karena inverter setengah panah pada input.

Bandingkan ini dengan kontrol input data paralel oleh jam ANSI SN75ALS166 sinkron sebelumnya. Perhatikan perbedaan dalam label Data ANSI.

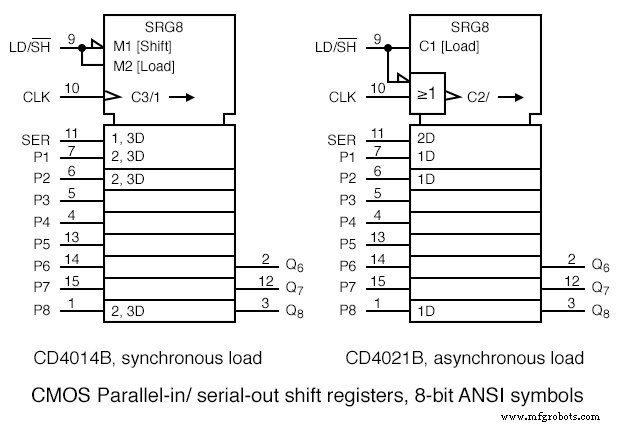

Pada CD4014B di atas, M1 ditegaskan ketika LD/SH’=0 . M2 ditegaskan ketika LD/SH’=1 .

Jam C3/1 digunakan untuk memuat data paralel pada 2, 3D ketika M2 aktif seperti yang ditunjukkan oleh 2,3 label awalan.

Pin P3 ke P7 dipahami memiliki smae internal 2,3 label awalan sebagai P2 dan P8 . Di SER , 1,3D awalan menyiratkan bahwa M1 dan jam C3 diperlukan untuk memasukkan data serial.

Pergeseran kanan terjadi saat M1 aktif seperti yang ditunjukkan oleh 1 di panah C3/1 .

CD4021B adalah bagian yang serupa kecuali untuk pemuatan data paralel asinkron seperti yang tersirat oleh kurangnya 2 awalan di label data 1D untuk pin P1, P2, hingga P8.

Tentu saja, awalan 2 dalam label 2D pada masukan SER mengatakan bahwa data di-clock ke pin ini. ATAU inset gerbang menunjukkan bahwa jam dikendalikan oleh LD/SH’ .

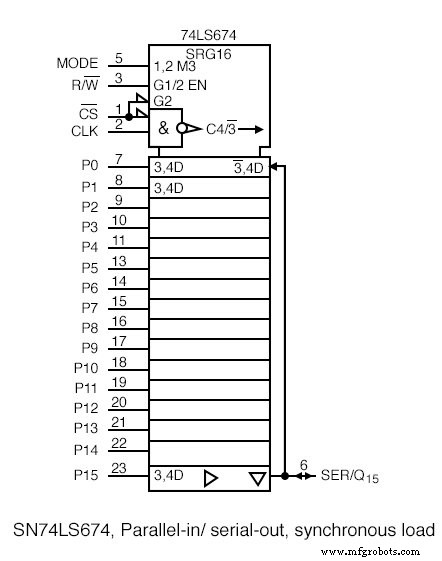

Label internal SN74LS674 di atas SRG 16 menunjukkan register geser 16-bit.

MODE masukan ke bagian kontrol di bagian atas simbol diberi label 1,2 M3 . M3 internal adalah fungsi dari masukan MODE dan G1 dan G2 seperti yang ditunjukkan oleh 1,2 sebelumnya M3 .

Label dasar G menunjukkan DAN fungsi dari G . tersebut masukan. Masukkan R/W’ secara internal diberi label G1/2 EN .

Ini adalah mengaktifkan EN (dikendalikan oleh G1 DAN G2 ) untuk perangkat tristate yang digunakan di tempat lain dalam simbol.

Kami perhatikan bahwa CS' aktif (pin 1) adalah internal G2 . Pilih chip CS' juga DAN ed dengan masukan CLK untuk memberikan jam internal C4 .

Gelembung di dalam panah jam menunjukkan bahwa aktivitas berada di tepi jam negatif (transisi tinggi ke rendah).

Garis miring (/) adalah pemisah yang menyiratkan dua fungsi untuk jam. Sebelum garis miring, C4 menunjukkan kontrol apa pun dengan awalan 4 .

Setelah garis miring, 3’ (panah) menunjukkan pergeseran. 3' dari C4/3' menyiratkan pergeseran ketika M3 tidak ditegaskan (MODE=0 ). Panah panjang menunjukkan pergeseran ke kanan (bawah).

Bergerak ke bawah di bawah bagian kontrol ke bagian data, kami memiliki input eksternal P0-P15 , pin (7-11, 13-23).

Awalan 3,4 dari label internal 3,4D menunjukkan bahwa M3 dan jam C4 mengontrol pemuatan data paralel.

D singkatan dari Data. Label ini diasumsikan berlaku untuk semua input paralel, meskipun tidak tertulis secara eksplisit.

Cari label 3’,4D di sebelah kanan P0 (pin7) panggung. Dilengkapi-3 menunjukkan bahwaM3=MODE=0 input (shift) SER/Q15 (pin5) pada waktu jam, (4 dari 3',4D) sesuai dengan jam C4 .

Dengan kata lain, dengan MODE=0 , kami menggeser data ke Q0 dari input serial (pin 6). Semua tahapan lainnya bergeser ke kanan (bawah) pada waktu jam.

Pindah ke bagian bawah simbol, segitiga yang menunjuk ke kanan menunjukkan penyangga antara Q dan pin keluaran.

Segitiga menunjuk ke bawah menunjukkan perangkat tri-negara. Kami sebelumnya menyatakan bahwa tristate dikendalikan oleh mengaktifkan EN , yang sebenarnya G1 DAN G2 dari bagian kontrol.

Jika R/W=0 , tri-state dinonaktifkan, dan kita dapat menggeser data ke Q0 melalui SER (pin 6), detail yang kami hilangkan di atas. Kami sebenarnya membutuhkan MODE=0, R/W’=0, CS’=0

Logika internal SN74LS674 dan tabel yang meringkas pengoperasian sinyal kontrol tersedia di tautan dalam daftar peluru, bagian atas.

Jika R/W’=1 , tristate diaktifkan, Q15 menggeser SER/Q15 (pin 6) dan disirkulasikan kembali ke Q0 panggung melalui kabel tangan kanan ke 3’,4D .

Kami berasumsi bahwa CS 'rendah memberi kami jam C4/3' dan G2 ke EN mampu tri-negara.

Aplikasi dari register geser paralel-in/serial-out adalah untuk membaca data ke dalam mikroprosesor.

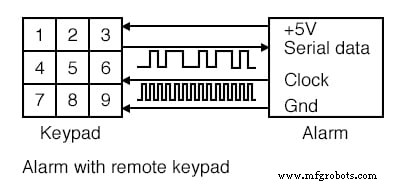

Alarm di atas dikendalikan oleh keypad jarak jauh. Kotak alarm memasok +5V dan menghubungkannya ke keypad jarak jauh untuk menyalakannya.

Alarm membaca keypad jarak jauh setiap beberapa puluh milidetik dengan mengirimkan shift clock ke keypad yang mengembalikan data serial yang menunjukkan status tombol melalui register geser paralel-in/serial-out.

Jadi, kami membaca sembilan sakelar kunci dengan empat kabel. Berapa banyak kabel yang diperlukan jika kita harus menjalankan rangkaian untuk masing-masing dari sembilan kunci?

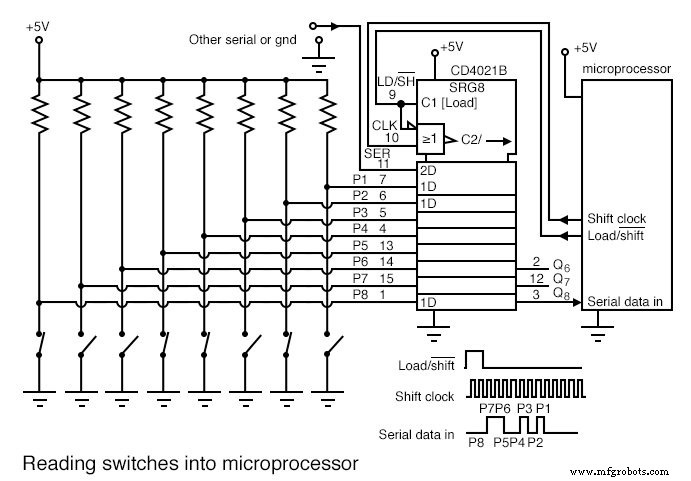

Aplikasi praktis dari register geser paralel-in/serial-out adalah membaca banyak penutup sakelar ke dalam mikroprosesor hanya dengan beberapa pin.

Beberapa mikroprosesor kelas bawah hanya memiliki pin 6-I/O (Input/Output) yang tersedia pada paket 8-pin.

Atau, kita mungkin telah menggunakan sebagian besar pin pada paket 84-pin. Kita mungkin ingin mengurangi jumlah kabel yang mengelilingi papan sirkuit, mesin, kendaraan, atau gedung.

Ini akan meningkatkan keandalan sistem kami. Telah dilaporkan bahwa produsen yang telah mengurangi jumlah kabel di mobil menghasilkan produk yang lebih andal.

Bagaimanapun, hanya tiga pin mikroprosesor yang diperlukan untuk membaca dalam 8-bit data dari sakelar pada gambar di atas.

Kami telah memilih perangkat pemuatan asinkron, CD4021B karena lebih mudah untuk mengontrol pemuatan data tanpa harus menghasilkan satu jam beban paralel.

Input data paralel dari register geser ditarik hingga +5V dengan resistor pada setiap input.

Jika semua sakelar terbuka, semua 1 s akan dimuat ke register geser saat mikroprosesor menggerakkan LD/SH’ garis dari rendah ke tinggi, lalu kembali rendah untuk mengantisipasi pergeseran.

Penutupan sakelar apa pun akan menerapkan logika 0 s ke input paralel yang sesuai. Pola data pada P1-P7 akan dimuat paralel oleh LD/SH’=1 dihasilkan oleh perangkat lunak mikroprosesor.

Mikroprosesor menghasilkan pulsa shift dan membaca bit data untuk masing-masing 8-bit.

Proses ini dapat dilakukan sepenuhnya dengan perangkat lunak, atau mikroprosesor yang lebih besar mungkin memiliki satu atau lebih antarmuka serial untuk melakukan tugas lebih cepat dengan perangkat keras.

Dengan LD/SH’=0 , mikroprosesor menghasilkan 0 ke 1 transisi pada Pergeseran garis jam , lalu membaca bit data pada Data serial di garis. Ini diulang untuk semua 8-bit.

SER garis register geser dapat digerakkan oleh sirkuit CD4021B identik lainnya jika lebih banyak kontak sakelar perlu dibaca.

Dalam hal ini, mikroprosesor menghasilkan pulsa 16-shift. Kemungkinan besar, itu akan didorong oleh sesuatu yang lain yang kompatibel dengan format data serial ini, misalnya, konverter analog ke digital, sensor suhu, pemindai keyboard, memori hanya-baca serial.

Adapun penutup sakelar, itu mungkin sakelar batas pada pengangkutan mesin, sensor suhu berlebih, sakelar buluh magnetik, sakelar pintu atau jendela, sakelar tekanan udara atau air, atau pengganggu optik solid state.

LEMBAR KERJA TERKAIT:

Teknologi Industri

Kami telah menggunakan analitik untuk meningkatkan proses produksi kami di pabrik Bosch selama bertahun-tahun. Jadi, apa yang baru dalam analitik di bidang manufaktur, dan apa langkah selanjutnya? Metodologi kami untuk analisis persyaratan membuat semua perbedaan Ada berbagai cara untuk menjalanka

Apa itu Typecasting di C? Typecasting adalah mengubah satu tipe data menjadi yang lain. Ini juga disebut sebagai konversi data atau konversi tipe dalam bahasa C. Ini adalah salah satu konsep penting yang diperkenalkan dalam pemrograman C. Pemrograman C menyediakan dua jenis operasi pengecoran tipe

Komponen dan persediaan Arduino Nano R3 × 1 Texas Instruments Shift Register- Serial to Parallel 74HC595 × 4 Ukuran Penuh Papan Tempat Memotong Roti Tanpa Solder × 1 LED (generik) Tergantung pada preferensi Anda. × 1 Resistor 100 ohm Tergantung pada LED

Arduino Serial:Komunikasi Serial oleh Arduino Latar Belakang Komunikasi Serial: Ketika mikrokontroler atau mikroprosesor perlu berkomunikasi dengan dunia luar, maka mereka menyediakan data dalam bentuk paket 8 bit, jadi jika satu sistem perlu berkomunikasi dengan yang lain, maka total 8 kabel kabel