Kontrol Impedansi dalam Desain PCB Sirkuit Digital Berkecepatan Tinggi

Teknologi kontrol impedansi cukup penting dalam desain sirkuit digital berkecepatan tinggi di mana metode yang efektif harus diadopsi untuk memastikan kinerja yang sangat baik dari PCB berkecepatan tinggi.

Perhitungan Impedansi dan Kontrol Impedansi Jalur Transmisi Sirkuit Berkecepatan Tinggi pada PCB

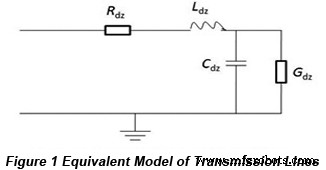

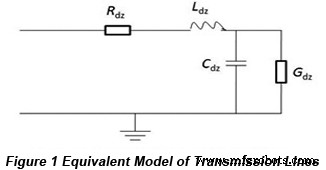

• Model Setara pada Saluran Transmisi

Gambar 1 menunjukkan efek ekivalen saluran transmisi pada PCB, yang merupakan struktur yang mencakup tandem dan kapasitor ganda, resistor, dan induktor (model RLGC).

Nilai khas dari resistansi tandem berada dalam kisaran dari 0,25 hingga 0,55ohm/kaki dan nilai resistansi dari beberapa resistor biasanya tetap cukup tinggi. Dengan resistansi parasit, kapasitansi dan induktansi ditambahkan pada jalur transmisi PCB, impedansi keseluruhan pada jalur transmisi disebut sebagai impedansi karakteristik (Z0 ). Nilai impedansi karakteristik relatif kecil dengan syarat diameter saluran besar, saluran dekat dengan daya/tanah atau konstanta dielektrik tinggi. Gambar 3 menunjukkan model ekivalen saluran transmisi dengan panjang dz, berdasarkan impedansi karakteristik saluran transmisi dapat disimpulkan sebagai rumus: . Dalam rumus ini, L mengacu pada induktansi setiap satuan panjang pada saluran transmisi sedangkan C mengacu pada kapasitansi setiap satuan panjang pada saluran transmisi.

. Dalam rumus ini, L mengacu pada induktansi setiap satuan panjang pada saluran transmisi sedangkan C mengacu pada kapasitansi setiap satuan panjang pada saluran transmisi.

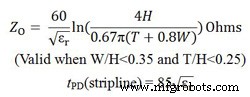

• Rumus Perhitungan Impedansi dan Delay Saluran Transmisi pada PCB

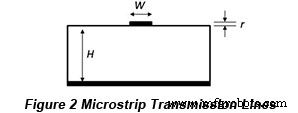

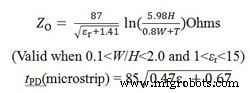

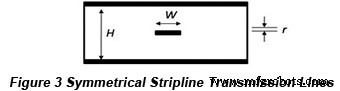

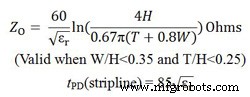

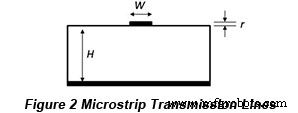

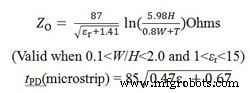

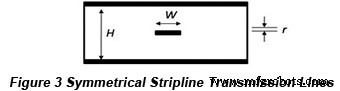

| Jalur Transmisi pada PCB | Rumus Perhitungan Impedansi dan Penundaan |

|  |

|  |

Dalam rumus di atas, Z0 mengacu pada impedansi (Ohm), W mengacu pada lebar garis (inci), T mengacu pada ketebalan garis (inci), H mengacu pada jarak ke tanah (inci), mengacu pada konstanta dielektrik relatif substrat, dan tPD mengacu pada waktu tunda (ps/inci).

• Aturan Tata Letak Kontrol Impedansi Saluran Transmisi

Berdasarkan analisis di atas, unit delay impedansi dan sinyal tidak berhubungan dengan frekuensi sinyal tetapi berhubungan dengan struktur papan, konstanta dielektrik relatif bahan papan, dan atribut fisik routing. Kesimpulan ini sangat penting untuk memahami PCB berkecepatan tinggi dan untuk desain PCB berkecepatan tinggi. Terlebih lagi, kecepatan transmisi saluran transmisi sinyal di lapisan luar jauh lebih cepat daripada di lapisan dalam sehingga elemen-elemen ini harus diperhitungkan untuk pengaturan tata letak saluran utama.

Kontrol impedansi adalah premis penting untuk implementasi transmisi sinyal. Namun, menurut struktur papan dan rumus perhitungan impedansi saluran transmisi, impedansi hanya bergantung pada bahan PCB dan struktur lapisan PCB dengan lebar saluran dan fitur perutean tidak berubah untuk saluran yang sama. Oleh karena itu, impedansi saluran tidak akan berubah pada lapisan PCB yang berbeda, yang tidak diperbolehkan dalam desain sirkuit kecepatan tinggi.

PCB berkecepatan tinggi dengan kepadatan tinggi dirancang untuk artikel ini dan sebagian besar sinyal di papan memiliki persyaratan impedansi. Misalnya, saluran sinyal CPCI harus memiliki impedansi 65Ohm, sinyal diferensial 100ohm, dan sinyal lainnya masing-masing 50ohm. Menurut ruang perutean PCB, setidaknya perutean sepuluh lapis harus digunakan dan rencana desain PCB 16 lapis ditentukan.

Karena ketebalan keseluruhan papan tidak boleh melebihi 2mm, ada beberapa kesulitan dalam hal penumpukan dengan beberapa masalah yang dipertimbangkan:

1). Setiap lapisan sinyal memiliki bidang gambar yang berdekatan untuk melindungi impedansi dan kualitas sinyal.

2). Setiap bidang daya memiliki lapisan tanah lengkap di sebelahnya sehingga kinerja daya dapat dipastikan dengan baik.

3). Penumpukan papan membutuhkan keseimbangan, dengan menghindari lengkungan papan.

Konstanta dielektrik medium diatur menjadi 4,3. Berdasarkan rancangan susun di atas, lebar saluran dan jarak antar saluran harus diatur sesuai dengan hasil perhitungan untuk memastikan persyaratan impedansi sinyal. Lebar garis diperoleh sebagai berikut:

1). Lebar garis sinyal pada lapisan permukaan adalah 5 mils dengan impedansinya 58.7Ohm.

2). Lebar garis sinyal CPCI pada lapisan permukaan adalah 4,5 mil dengan impedansinya 61,7Ohm.

3). Lebar garis sinyal di lapisan dalam adalah 4,5 mil dengan impedansinya 50,2Ohm.

4). Lebar garis di area BGA di lapisan dalam dan lapisan permukaan adalah 4mil dengan impedansi lapisan permukaan 64.6Ohm dan impedansi lapisan dalam 52.7Ohm.

5). Lebar saluran diferensial mikrostrip pada lapisan dalam adalah 5 mil dengan jarak antar saluran 6 mil dan impedansi 100,54Ohm.

6). Lebar garis diferensial garis strip di lapisan dalam adalah 4,5 mil dengan jarak antara saluran 10 mil dan impedansi 96.6Ohm.

Jarak antar garis diatur sebagai berikut:

1). Jarak antara garis sinyal (5mils) pada lapisan permukaan adalah 5.0mils.

2). Jarak antara garis sinyal CPCI (4,5 mil) pada lapisan permukaan adalah 9,0 mil.

3).. Jarak antara garis sinyal (4.5mils) pada lapisan dalam adalah 7.0mils.

4). Jarak antara garis pada lapisan permukaan dan lapisan dalam adalah 4.0mil.

5). Jarak antara jalur sinyal diferensial pada lapisan dalam dan antara jalur tersebut dengan jalur sinyal lainnya harus dijaga setidaknya 25 mil.

6). Jarak antara garis sinyal diferensial pada lapisan permukaan dan antara mereka dan garis sinyal lainnya harus dijaga setidaknya 20 mil.

Setelah pencetakan PCB, impedansi papan uji diuji oleh penguji impedansi POLAR-Cits500 dengan hasil pada tabel berikut. Data menunjukkan bahwa impedansi harus dikontrol dalam kisaran 50Ohmۯ%, 60Ohmۯ%, dan 100Ohmۯ% dalam proses desain dan fabrikasi PCB berkecepatan tinggi.

| Impedansi Prasetel (Ohm) | Impedansi Praktis (Ohm) |

| 50 | 47.52-52.33 |

| 60 | 57.65-61.35 |

| 100 | 93,65-106,35 |

LVDS dan Kontrol Impedansinya pada PCB

• LVDS

LVDS adalah jenis tingkat transmisi sinyal serial berkecepatan tinggi dengan keunggulan kecepatan transmisi tinggi, konsumsi daya rendah, kemampuan anti-interferensi yang kuat, jarak transmisi yang jauh, dan pencocokan yang layak. Bidang aplikasi LVDS mencakup komputer, komunikasi, dan konsumsi.

• Desain impedansi LVDS

LVDS memiliki fitur ayunan tegangan hanya 350MV dengan jarak transmisi terpanjang lebih dari 10 meter. Untuk memastikan bahwa sinyal tidak akan terpengaruh oleh sinyal yang dipantulkan dalam proses transmisi sinyal di saluran transmisi, impedansi saluran transmisi harus dikendalikan dengan impedansi saluran tunggal 50Ohm dan impedansi diferensial 100Ohm. Dalam aplikasi praktis, impedansi dapat dikontrol dengan mengatur ketebalan susun yang wajar dan parameter menengah, menyesuaikan lebar saluran dan jarak antar saluran dan menghitung impedansi saluran tunggal dan saluran diferensial dengan bantuan beberapa alat analisis simulasi kecepatan tinggi.

Namun, sebagian besar waktu, relatif sulit untuk memenuhi persyaratan impedansi saluran tunggal dan impedansi diferensial. Di satu sisi, rentang penyesuaian lebar garis W dan jarak antara garis S dikendalikan oleh ruang desain fisik. Misalnya, perutean dan lebar garis pada konektor margin dengan BGA atau DIP dipengaruhi oleh ukuran dan jarak pad. Di sisi lain, perubahan W dan S akan mempengaruhi hasil saluran tunggal dan impedansi diferensial. Hingga saat ini, mudah dan nyaman untuk mengetahui hubungan antara lebar garis yang telah ditentukan sebelumnya dan jarak garis.

• Aturan perutean LVDS

Secara umum, perutean sinyal diferensial diimplementasikan sesuai dengan aturan desain impedansi, yang mampu memastikan kualitas LVDS. Dalam perutean praktis, LVDS harus mematuhi aturan berikut:

1). Pasangan diferensial harus sependek mungkin, garis harus lurus dan jumlah lubang tembus harus diperkecil. Jarak antara garis sinyal dalam pasangan diferensial harus sama. Semua aturan ini berkontribusi pada penghindaran perutean yang panjang dan banyak turn-off. Untuk mematikan, sebaiknya digunakan mematikan 45 derajat, bukan 90 derajat.

2). Jarak antara pasangan diferensial harus dipertahankan lebih dari 10 kali untuk mengurangi crosstalk antar baris. Bila perlu, lubang pentanahan dapat ditempatkan di antara pasangan diferensial untuk isolasi.

3). LVDS tidak dapat dibagi di seluruh permukaan. Meskipun dua sinyal diferensial adalah jalur timbal balik, jalur pengembalian sinyal tidak dapat ditebang sebagai akibat dari pemisahan permukaan. Namun demikian, saluran transmisi mungkin akan menyebabkan diskontinuitas impedansi sebagai akibat dari kurangnya bidang gambar.

4). Hindari sinyal diferensial antar lapisan. Selama pembuatan PCB, akurasi penyelarasan susun antar lapisan jauh lebih rendah daripada akurasi etsa di lapisan yang sama ditambah kerugian sedang selama penumpukan, yang semuanya mengarah pada perubahan impedansi diferensial antara pasangan diferensial.

5). Dalam desain impedansi, metode kopling harus digunakan di dalamnya.

6). Struktur susunan PCB yang sesuai harus diatur untuk memastikan isolasi antara sinyal level tegangan dan LVDS. Jika memungkinkan, sinyal seperti TTL/CMOS berkecepatan tinggi dapat disetel pada lapisan yang berbeda, diisolasi dari perutean LVDS oleh lapisan tanah dan daya.

7). Pasangan sinyal diferensial harus kompatibel dengan panjang perutean.

Sumber Daya Bermanfaat

• Elemen yang Mempengaruhi Impedansi Karakteristik PCB dan Solusinya

• Pertimbangan Desain Impedansi untuk PCB Flex-Rigid

• Cara Menganalisis dan Melarang Impedansi Daya PCB Berkecepatan Tinggi

• Kontrol Impedansi Vias dan Pengaruhnya pada Integritas Sinyal dalam Desain PCB

• Layanan Pembuatan PCB Fitur Lengkap dari PCBCart - Beberapa opsi Nilai tambah

• Layanan Perakitan PCB Tingkat Lanjut dari PCBCart - Mulai dari 1 buah

. Dalam rumus ini, L mengacu pada induktansi setiap satuan panjang pada saluran transmisi sedangkan C mengacu pada kapasitansi setiap satuan panjang pada saluran transmisi.

. Dalam rumus ini, L mengacu pada induktansi setiap satuan panjang pada saluran transmisi sedangkan C mengacu pada kapasitansi setiap satuan panjang pada saluran transmisi.