Verilog

Parameter adalah konstruksi Verilog yang memungkinkan modul untuk digunakan kembali dengan spesifikasi yang berbeda. Misalnya, penambah 4-bit dapat diparameterisasi untuk menerima nilai jumlah bit dan nilai parameter baru dapat diteruskan selama pembuatan modul. Jadi, penambah N-bit bisa menjadi penambah 4-bit, 8-bit atau 16-bit. Mereka seperti argumen ke fungsi yang diteruskan selama pemanggilan fungsi.

parameter MSB = 7; // MSB is a parameter with a constant value 7

parameter REAL = 4.5; // REAL holds a real number

parameter FIFO_DEPTH = 256,

MAX_WIDTH = 32; // Declares two parameters

parameter [7:0] f_const = 2'b3; // 2 bit value is converted to 8 bits; 8'b3

Parameter pada dasarnya adalah konstanta dan karenanya ilegal untuk mengubah nilainya saat runtime. Adalah ilegal untuk mendeklarasikan ulang nama yang sudah digunakan oleh net, variabel, atau parameter lain.

Ada dua jenis parameter utama, modul dan tentukan dan keduanya menerima spesifikasi jangkauan. Namun, mereka biasanya dibuat selebar nilai yang akan disimpan dan karenanya spesifikasi rentang tidak diperlukan.

Parameter modul dapat digunakan untuk mengganti definisi parameter dalam modul dan ini membuat modul memiliki serangkaian parameter yang berbeda pada waktu kompilasi. Parameter dapat dimodifikasi dengan defparam pernyataan atau dalam pernyataan instance modul. Ini adalah praktik umum untuk menggunakan huruf besar dalam nama untuk parameter agar langsung terlihat.

Modul yang ditunjukkan di bawah ini menggunakan parameter untuk menentukan lebar bus, lebar data, dan kedalaman FIFO dalam desain, dan dapat ditimpa dengan nilai baru saat modul dibuat atau dengan menggunakan defparam pernyataan.

// Verilog 1995 style port declaration

module design_ip ( addr,

wdata,

write,

sel,

rdata);

parameter BUS_WIDTH = 32,

DATA_WIDTH = 64,

FIFO_DEPTH = 512;

input addr;

input wdata;

input write;

input sel;

output rdata;

wire [BUS_WIDTH-1:0] addr;

wire [DATA_WIDTH-1:0] wdata;

reg [DATA_WIDTH-1:0] rdata;

reg [7:0] fifo [FIFO_DEPTH];

// Design code goes here ...

endmodule

Dalam gaya ANSI baru dari deklarasi port Verilog, Anda dapat mendeklarasikan parameter seperti yang ditunjukkan di bawah ini.

module design_ip

#(parameter BUS_WIDTH=32,

parameter DATA_WIDTH=64) (

input [BUS_WIDTH-1:0] addr,

// Other port declarations

);

Parameter dapat diganti dengan nilai baru selama pembuatan modul. Bagian pertama membuat instance modul yang disebut design_ip dengan nama d0 di mana parameter baru dilewatkan dalam #( ) . Bagian kedua menggunakan konstruksi Verilog yang disebut defparam untuk mengatur nilai parameter baru. Metode pertama adalah cara yang paling umum digunakan untuk melewatkan parameter baru dalam desain RTL. Metode kedua biasanya digunakan dalam simulasi testbench untuk memperbarui parameter desain dengan cepat tanpa harus membuat ulang modul.

module tb;

// Module instantiation override

design_ip #(BUS_WIDTH = 64, DATA_WIDTH = 128) d0 ( [port list]);

// Use of defparam to override

defparam d0.FIFO_DEPTH = 128;

endmodule

Penghitung modul memiliki dua parameter N dan DOWN yang dinyatakan memiliki nilai default masing-masing 2 dan 0. N mengontrol jumlah bit dalam output secara efektif mengontrol lebar penghitung. Secara default ini adalah penghitung 2-bit. Parameter BAWAH mengontrol apakah penghitung harus bertambah atau berkurang. Secara default, penghitung akan berkurang karena parameter disetel ke 0.

module counter

#( parameter N = 2,

parameter DOWN = 0)

( input clk,

input rstn,

input en,

output reg [N-1:0] out);

always @ (posedge clk) begin

if (!rstn) begin

out <= 0;

end else begin

if (en)

if (DOWN)

out <= out - 1;

else

out <= out + 1;

else

out <= out;

end

end

endmodule

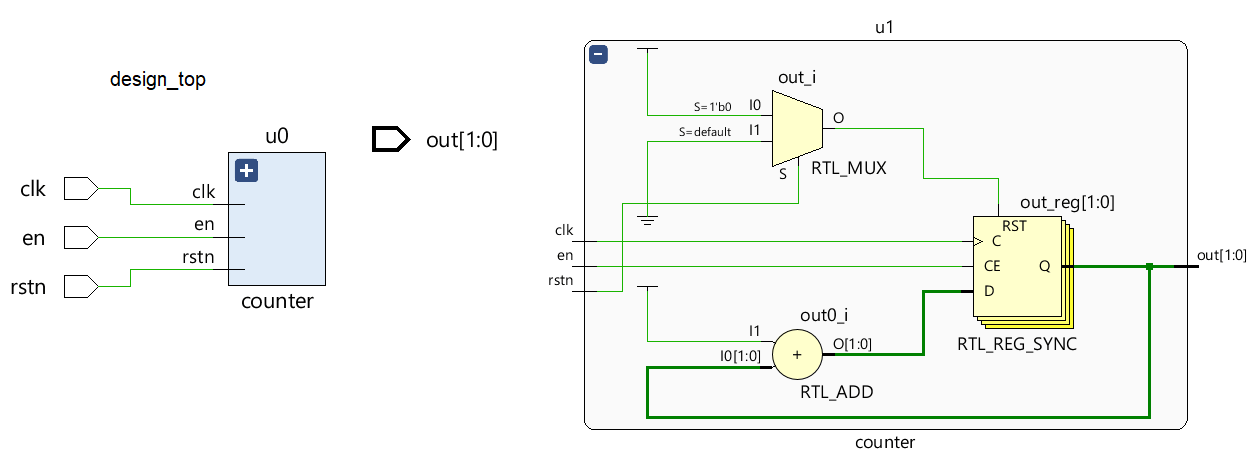

Penghitung modul diinstansiasi dengan N sebagai 2 meskipun tidak diperlukan karena nilai defaultnya adalah 2. DOWN tidak diteruskan selama pembuatan modul dan karenanya mengambil nilai default 0 menjadikannya penghitung atas.

module design_top ( input clk,

input rstn,

input en,

output [1:0] out);

counter #(.N(2)) u0 ( .clk(clk),

.rstn(rstn),

.en(en));

endmodule

Lihat bahwa parameter default digunakan untuk mengimplementasikan pencacah di mana N sama dengan dua menjadikannya pencacah 2-bit dan DOWN sama dengan nol menjadikannya pencacah atas. Keluaran dari penghitung dibiarkan tidak terhubung di tingkat atas.

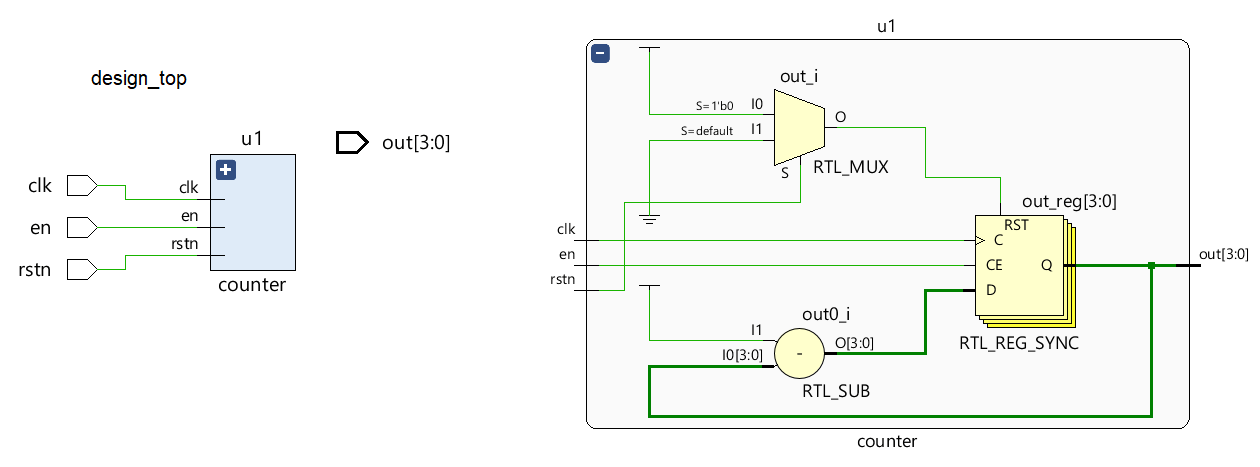

Dalam hal ini, pencacah modul diinstansiasi dengan N sebagai 4 menjadikannya pencacah 4-bit. DOWN melewati nilai 1 selama pembuatan modul dan karenanya penghitung turun diimplementasikan.

module design_top ( input clk,

input rstn,

input en,

output [3:0] out);

counter #(.N(4), .DOWN(1))

u1 ( .clk(clk),

.rstn(rstn),

.en(en));

endmodule

Ini terutama digunakan untuk memberikan nilai waktu dan penundaan dan dideklarasikan menggunakan specparam kata kunci. Itu diperbolehkan untuk digunakan baik dalam spesifikasi blok dan badan modul utama.

// Use of specify block

specify

specparam t_rise = 200, t_fall = 150;

specparam clk_to_q = 70, d_to_q = 100;

endspecify

// Within main module

module my_block ( ... );

specparam dhold = 2.0;

specparam ddly = 1.5;

parameter WIDTH = 32;

endmodule

| Tentukan parameter | Parameter modul |

|---|---|

Dideklarasikan oleh specparam | Dideklarasikan oleh parameter |

Dapat dideklarasikan di dalam specify blok atau di dalam modul utama | Hanya dapat dideklarasikan dalam modul utama |

| Dapat diberikan spesifikasi dan parameter | Mungkin tidak diberi spesifikasi |

| SDF dapat digunakan untuk mengganti nilai | Nilai parameter deklarasi instance atau defparam dapat digunakan untuk menimpa |

Verilog

Sebuah generate block memungkinkan untuk menggandakan instance modul atau melakukan instantiasi bersyarat dari modul apa pun. Ini memberikan kemampuan untuk desain yang akan dibangun berdasarkan parameter Verilog. Pernyataan ini sangat cocok ketika operasi yang sama atau contoh modul perlu diulang b

Sebuah for loop adalah loop yang paling banyak digunakan dalam perangkat lunak, tetapi terutama digunakan untuk mereplikasi logika perangkat keras di Verilog. Ide di balik for loop adalah untuk mengulangi satu set pernyataan yang diberikan dalam loop selama kondisi yang diberikan benar. Ini sangat m

case pernyataan memeriksa apakah ekspresi yang diberikan cocok dengan salah satu ekspresi lain dalam daftar dan bercabang sesuai. Biasanya digunakan untuk mengimplementasikan multiplexer. Konstruksi if-else mungkin tidak cocok jika ada banyak kondisi yang harus diperiksa dan akan disintesis menjadi

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan? Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang