Ripple Carry Adder:Semua yang Perlu Anda Ketahui

Sirkuit logika dapat mengandalkan penambah pembawa riak untuk menambahkan nilai n-bit bersama-sama. Hasilnya, implementasi rangkaian digital ini menyediakan fitur yang berguna di banyak aplikasi. Namun, ia juga menunjukkan kinerja yang tertunda karena proses perhitungan yang lambat. Itu biasanya melibatkan menunggu setiap tahap penambah penuh untuk riak bit ke tahap penambah penuh berikutnya. Proses seperti itu berulang hingga mencapai akhir, memberikan hasil.

Memahami penambah riak pembawa bisa tampak sedikit membingungkan. Dengan mengingat hal itu, kami menyusun artikel ini untuk membantu Anda mendapatkan lebih banyak pengetahuan tentang hal ini. Jadi mari kita mulai!

Apa itu Ripple Carry Adder?

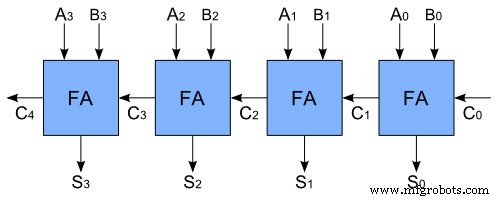

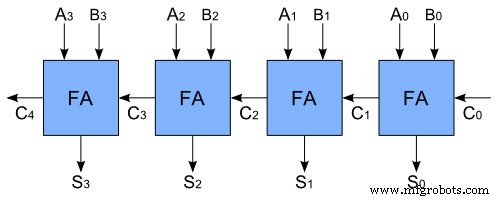

Ripple carry adder berfungsi sebagai sirkuit digital yang menjumlahkan dua bilangan biner n-bit dan memberikan hasilnya. Strukturnya terdiri dari beberapa penambah penuh, dengan masing-masing terhubung dalam pengaturan bertingkat. Dengan cara ini, output carry dari full adder terhubung ke input full adder berikutnya.

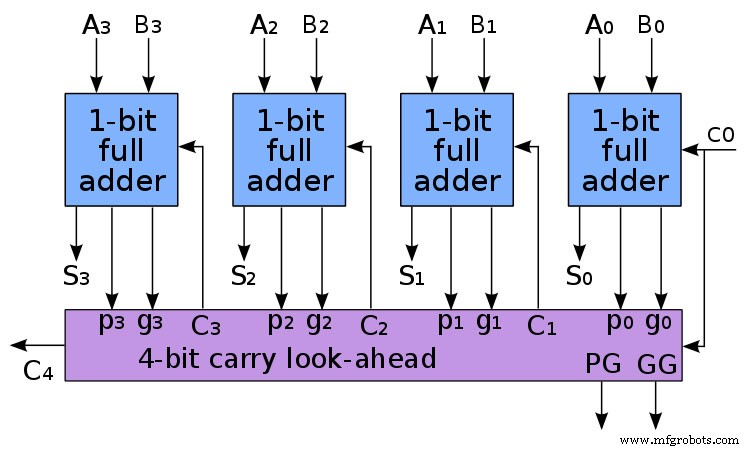

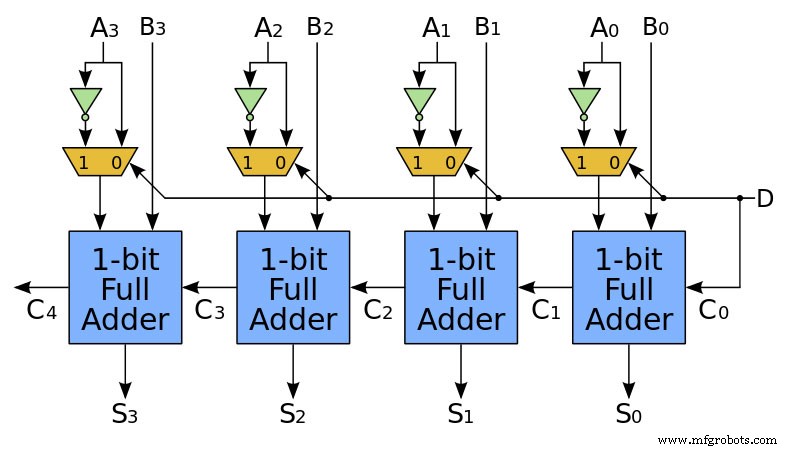

Diagram riak 4-bit membawa penambah.

Sumber:Wikimedia Commons

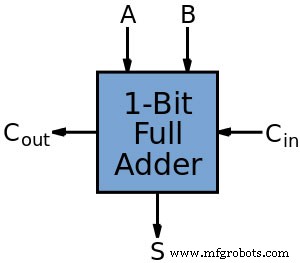

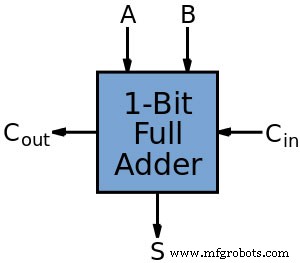

Sebuah penambah penuh mewakili rangkaian logika yang dirancang untuk menambahkan tiga input sambil menghasilkan dua output. Lebih khusus lagi, dua input berfungsi sebagai A dan B, sedangkan yang ketiga menggambarkan bit carry-in. (C-IN) Sementara itu, satu output mewakili bit carry-out (C-OUT), dan yang lainnya mewakili bit jumlah (S). Pada akhirnya, rangkaian penambah penuh dapat terhubung ke delapan input untuk membentuk penambah lebar byte. Ini mengalirkan bit carry dari satu penambah ke penambah berikutnya. Menggabungkan dua sirkuit setengah penambah bersama-sama akan membentuk penambah penuh.

Diagram logika penambah lengkap

Sumber:Wikimedia Commons

Prinsip Kerja Ripple Carry Adder

Setiap carry menghasilkan melalui tahap penambah penuh, yang kemudian akan melanjutkan ke penambah penuh berikutnya melalui inputnya. Seluruh proses maju hingga mencapai penambah penuh akhir. Akibatnya, masing-masing membawa riak bit keluaran ke tahap penambah penuh berikutnya. Secara keseluruhan, operasi yang paling penting melibatkan penambahan setiap urutan bit input bersama-sama, seperti penambah 4-bit, penambah 8-bit, penambah 16-bit, dll.

Karena penundaan propagasi sirkuit logika, jumlah bit dan bit carry-out tetap tidak valid sampai tahap carry-in terjadi. Penundaan propagasi biasanya terjadi karena jumlah waktu yang berlalu antara input dan output. Misalnya, ketika input gerbang NOT disetel ke 0, output akan dikonfigurasikan ke 1, dll. Penundaan propagasi menentukan berapa banyak waktu yang berlalu antara pengaturan output ke nol dan konfigurasi input ke satu. Selain itu, penundaan propagasi carry menentukan berapa banyak waktu yang berlalu antara penerimaan sinyal carry-in dan implementasi sinyal carry-out.

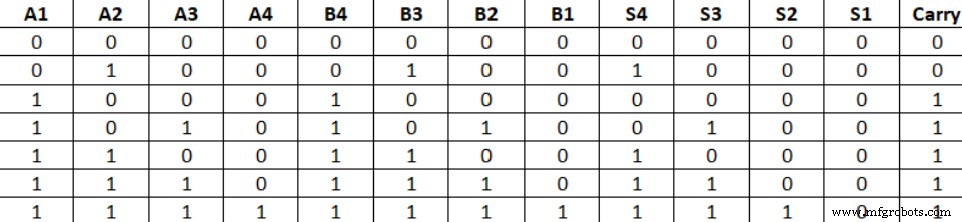

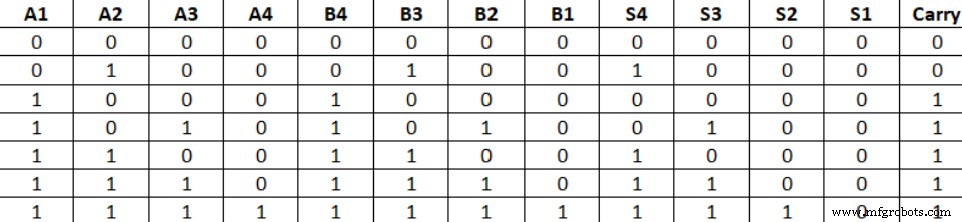

Tabel Kebenaran Ripple Carry Adder

Tabel kebenaran, seperti yang ditunjukkan di bawah, menentukan setiap nilai output untuk semua input dalam penambah pembawa riak.

Riak membawa tabel kebenaran penambah.

Kode VHDL Ripple Carry Adder dan Kode Verilog

Untuk menerapkan ripple carry adder, Anda memerlukan kode VHDL dan kode Verilog. Ada dua contoh yang diberikan. Yang pertama melibatkan penambah pembawa riak dua bit. Sementara itu, contoh lainnya menghasilkan ripple carry adder yang mengumpulkan setiap lebar input sebagai parameter.

Aplikasi Ripple Carry Adder

Jam berisi penambah pembawa riak

- Lakukan penambahan untuk dua nilai N-bit

- Pemrosesan sinyal digital dan mikroprosesor

- Pengatur Waktu

- Kalkulator

- Jam

Keuntungan dan Kerugian Ripple Carries Adder

Keuntungan

Ripple-carry adder tidak mahal.

Sumber:Wikimedia Commons

- Memberikan hasil yang akurat melalui penambahan n-bit

- Proses desain dan pengembangan yang sederhana

- Murah

Kekurangan

Penundaan menyebabkan ketidaknyamanan untuk fungsionalitas keseluruhannya

- Ini hanya memungkinkan satu penambah penuh berfungsi pada satu waktu

- Keterlambatan carry bit menyebabkannya berjalan lambat

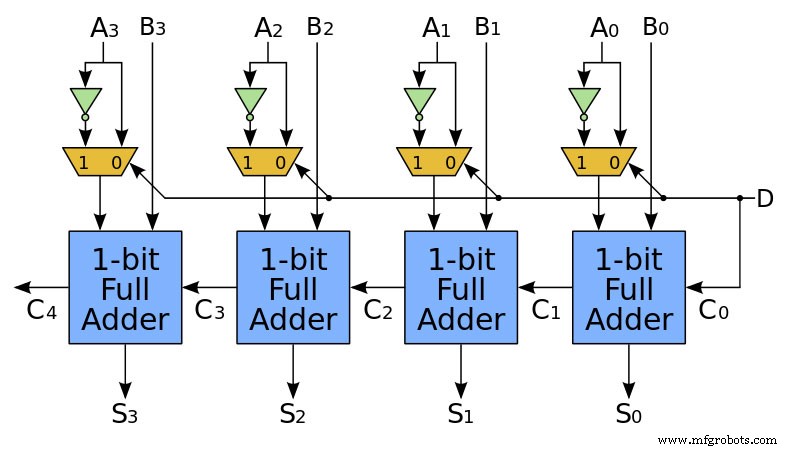

Membawa Penambah Pandangan ke Depan

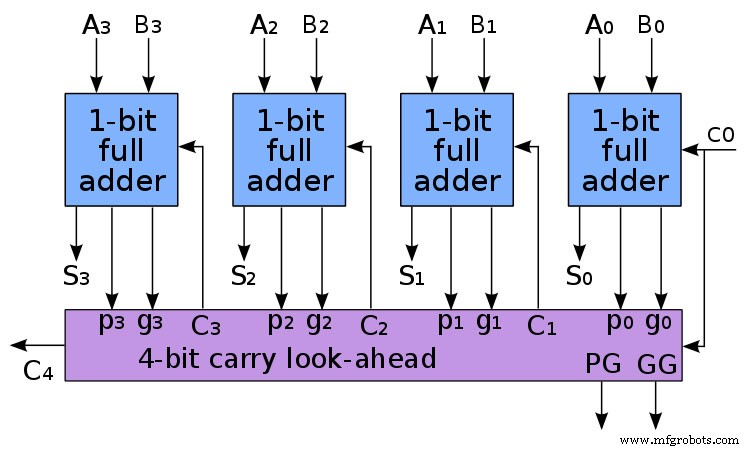

Logika carry look-ahead menghitung bit carry-in sebelum mencapai jumlah, secara efektif mengurangi waktu tunda. Ini terjadi setelah membangkitkan sinyal pembawa melalui dua metode. Yang pertama melibatkan bit a dan b yang sama dengan satu. Sementara itu, pendekatan kedua melibatkan carry-in dan bit a atau b yang disamakan dengan satu. Bit-bit ini diimplementasikan pada tahap sebelumnya, sementara carry-in dimulai pada awal adder.

Bawa skema penambah pandangan ke depan.

Sumber:Wikimedia Commons

Dalam ripple carry adder, setiap full adder memproses bit carry-in ke adder berikutnya sebelum menghitung jumlahnya. Oleh karena itu, proses tersebut mengakibatkan penundaan yang lama.

Ringkasan

Secara keseluruhan, carry-ripple-adder menyediakan kemampuan untuk menambahkan dua angka n-bit bersama-sama dalam sirkuit digital. Meskipun prosesnya lambat, ia masih memiliki aplikasi berguna yang pada dasarnya membantu pemrosesan sinyal digital. Dengan cara ini, penambah pembawa riak mengaduk bit pembawa ke setiap tahap penambah penuh hingga mencapai penambah penuh akhir. Pada titik ini, ia kemudian akan melakukan perhitungan yang diperlukan. Namun, carry-lookahead adder mencapai perhitungan ini lebih cepat karena menggunakan teknik yang berbeda. Dengan demikian, mengurangi waktu tunda.

Apakah Anda memiliki pertanyaan tentang penambah pembawa riak? Jangan ragu untuk menghubungi kami!