Verilog

Maksud utama dari tipe data dalam bahasa Verilog adalah untuk mewakili elemen penyimpanan data seperti bit dalam flip-flop dan elemen transmisi seperti kabel yang menghubungkan antara gerbang logika dan struktur sekuensial.

Hampir semua tipe data hanya dapat memiliki satu dari empat nilai yang berbeda seperti yang diberikan di bawah ini kecuali untuk real dan event tipe data.

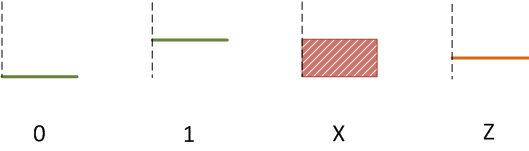

Gambar berikut menunjukkan bagaimana nilai-nilai ini direpresentasikan dalam diagram waktu dan bentuk gelombang simulasi. Kebanyakan simulator menggunakan konvensi ini di mana merah singkatan dari X dan oranye di tengah berarti impedansi tinggi atau Z .

Karena Verilog pada dasarnya digunakan untuk menggambarkan elemen perangkat keras seperti flip-flop dan logika kombinasional seperti NAND dan NOR, Verilog harus memodelkan sistem nilai yang ditemukan dalam perangkat keras. Logika satu akan mewakili suplai tegangan Vdd yang dapat berkisar antara 0.8V hingga lebih dari 3V berdasarkan simpul teknologi fabrikasi. Logika nol akan mewakili ground dan karenanya nilai 0V.

X atau x berarti nilainya tidak diketahui pada saat itu, dan bisa berupa 0 atau 1. Ini sangat berbeda dengan cara X diperlakukan dalam logika boolean, yang artinya "tidak peduli".

Seperti halnya rangkaian listrik yang tidak lengkap, kabel yang tidak terhubung ke apa pun akan memiliki impedansi tinggi pada simpul itu dan diwakili oleh Z atau z . Bahkan di Verilog, setiap kabel yang tidak terhubung akan menghasilkan impedansi tinggi.

Jaring dan variabel adalah dua kelompok utama tipe data yang mewakili struktur perangkat keras yang berbeda dan berbeda dalam cara mereka ditugaskan dan mempertahankan nilai.

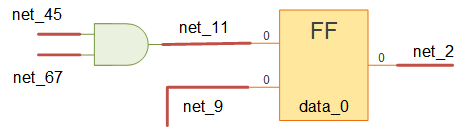

Jaring digunakan untuk menghubungkan antara entitas perangkat keras seperti gerbang logika dan karenanya tidak menyimpan nilai apa pun sendiri. Pada gambar di bawah ini, jaring yang disebut net_11 digunakan untuk menghubungkan antara output gerbang AND ke input pertama flip-flop yang disebut data_0. Dengan cara yang sama, dua input gerbang AND dihubungkan ke nets net_45 dan net_67.

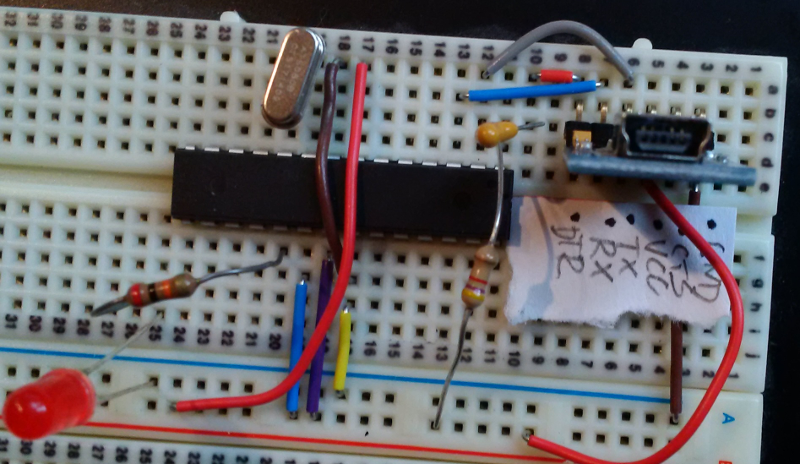

Ada berbagai jenis jaring dengan karakteristik yang berbeda, tetapi yang paling populer dan banyak digunakan adalah net dalam desain digital bertipe wire . Sebuah wire adalah tipe data Verilog yang digunakan untuk menghubungkan elemen dan untuk menghubungkan jaring yang digerakkan oleh satu gerbang atau penugasan berkelanjutan. wire mirip dengan kabel listrik yang digunakan untuk menghubungkan dua komponen pada papan tempat memotong roti.

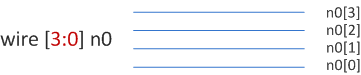

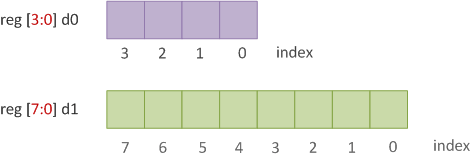

Ketika ada kebutuhan untuk beberapa jaring, jaring-jaring tersebut dapat dirangkai menjadi satu wire . Pada gambar yang ditunjukkan di bawah ini, kami memiliki kabel 4-bit yang dapat mengirim 4 nilai terpisah pada masing-masing kabel. Entitas seperti itu dengan lebar lebih dari 1 disebut vektor seperti yang akan kita lihat di artikel berikutnya.

wire [3:0] n0; // 4-bit wire -> this is a vector

Adalah ilegal untuk mendeklarasikan ulang nama yang telah dideklarasikan oleh net, parameter, atau variabel seperti yang ditunjukkan pada kode di bawah ini.

module design;

wire abc;

wire a;

wire b;

wire c;

wire abc; // Error: Identifier "abc" previously declared

assign abc = a & b | c;

endmodule

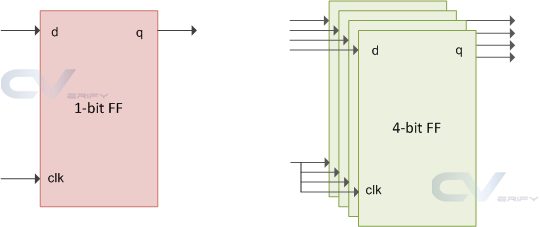

Variabel di sisi lain adalah abstraksi dari elemen penyimpanan data dan dapat menyimpan nilai. Flip-flop adalah contoh yang baik dari elemen penyimpanan.

Verilog tipe data reg dapat digunakan untuk memodelkan register perangkat keras karena dapat menyimpan nilai di antara penugasan. Perhatikan bahwa reg tidak harus selalu mewakili flip-flop karena dapat juga digunakan untuk mewakili logika kombinasional.

Pada gambar di sebelah kiri, kita memiliki flip-flop yang dapat menyimpan 1 bit dan flip-flop di sebelah kanan dapat menyimpan 4-bit.

Sebuah integer adalah variabel tujuan umum dengan lebar 32-bit yang dapat digunakan untuk tujuan lain saat memodelkan perangkat keras dan menyimpan nilai integer.

integer count; // Count is an integer value > 0

Sebuah time variabel tidak ditandatangani, lebar 64-bit dan dapat digunakan untuk menyimpan jumlah waktu simulasi untuk keperluan debugging. Sebuah realtime variabel hanya menyimpan waktu sebagai kuantitas floating point.

time end_time; // end_time can be stored a time value like 50ns

realtime rtime; // rtime = 40.25ps

Sebuah real variabel dapat menyimpan nilai floating point dan dapat diberikan dengan cara yang sama seperti integer dan reg .

real float; // float = 12.344 - can store floating numbers

module testbench;

integer int_a; // Integer variable

real real_b; // Real variable

time time_c; // Time variable

initial begin

int_a = 32'hcafe_1234; // Assign an integer value

real_b = 0.1234567; // Assign a floating point value

#20; // Advance simulation time by 20 units

time_c = $time; // Assign current simulation time

// Now print all variables using $display system task

$display ("int_a = 0x%0h", int_a);

$display ("real_b = %0.5f", real_b);

$display ("time_c = %0t", time_c);

end

endmodule

Log Simulasi ncsim> run int_a = 0xcafe1234 real_b = 0.12346 time_c = 20 ncsim: *W,RNQUIE: Simulation is complete.

String disimpan di reg , dan lebar reg variabel harus cukup besar untuk menampung string. Setiap karakter dalam string mewakili nilai ASCII dan membutuhkan 1 byte. Jika ukuran variabel lebih kecil dari string, maka Verilog memotong bit paling kiri dari string. Jika ukuran variabel lebih besar dari string, maka Verilog menambahkan nol di sebelah kiri string.

// "Hello World" requires 11 bytes

reg [8*11:1] str = "Hello World"; // Variable can store 11 bytes, str = "Hello World"

reg [8*5:1] str = "Hello World"; // Variable stores only 5 bytes (rest is truncated), str = "World"

reg [8*20:1] str = "Hello World"; // Variable can store 20 bytes (rest is padded with zeros), str = " Hello World"

Berikut adalah contoh lengkap yang menunjukkan bagaimana ketiga variabel yang diberikan di atas dapat disimulasikan.

module testbench;

reg [8*11:1] str1;

reg [8*5:1] str2;

reg [8*20:1] str3;

initial begin

str1 = "Hello World";

str2 = "Hello World";

str3 = "Hello World";

$display ("str1 = %s", str1);

$display ("str2 = %s", str2);

$display ("str3 = %s", str3);

end

endmodule

Perhatikan bahwa str1 memiliki ukuran yang tepat untuk menyimpan semua 11 byte string "Hello World" dan karenanya seluruh string akan dicetak. Namun str2 hanya dapat menyimpan 5 byte dan karenanya 6 byte atas terpotong dan berakhir dengan hanya menyimpan "Dunia". Variabel ketiga str3 lebih besar dari 11 byte dan mengisi spasi kosong ke kiri dan karenanya nilai yang disimpan di dalamnya menjadi " Hello World".

Log Simulasincsim> run str1 = Hello World str2 = World str3 = Hello World ncsim: *W,RNQUIE: Simulation is complete.

Verilog

Ada beberapa cara untuk mengelompokkan sekumpulan pernyataan bersama-sama yang secara sintaksis setara dengan satu pernyataan dan dikenal sebagai pernyataan blok . Ada dua jenis pernyataan blok:berurutan dan paralel. Sequential Pernyataan dibungkus menggunakan begin dan end kata kunci dan akan diek

Hari ini kita akan belajar tentang cara kerja menggambar dan jenis-jenisnya seperti menggambar kawat, menggambar batang dan menggambar tabung. Menggambar adalah proses pembentukan logam digunakan untuk mengurangi penampang dan menambah panjang benda kerja. Proses ini terkait dengan gaya tarik yang m

Gerbang Logika Digital Pertama, kita perlu mengetahui tentang gerbang logika “Gerbang logika adalah rangkaian elektronik atau perangkat yang membuat keputusan logika. Dengan kata lain, gerbang logika adalah rangkaian elektronik yang memiliki satu atau lebih dari satu input dan hanya satu output yang

Apa itu Ilmu Data? Ilmu Data adalah bidang interdisipliner yang melibatkan penggunaan metode, proses, dan sistem ilmiah untuk mengumpulkan, menyiapkan, dan menganalisis data dalam bentuk terstruktur dan tidak terstruktur. Ilmu data memanfaatkan berbagai bidang termasuk matematika, statistik, databa