Verilog

Konvensi leksikal di Verilog mirip dengan C dalam arti bahwa ia berisi aliran token. Token leksikal dapat terdiri dari satu atau lebih karakter dan token dapat berupa komentar, kata kunci, angka, string, atau spasi. Semua baris harus diakhiri dengan tanda titik koma ; .

Verilog peka huruf besar/kecil , jadi var_a dan var_A berbeda.

Ada dua cara untuk menulis komentar di Verilog.

// dan memberi tahu kompiler Verilog untuk memperlakukan semuanya setelah titik ini hingga akhir baris sebagai komentar./* dan diakhiri dengan */ dan tidak dapat disarangkan.Namun, komentar satu baris dapat disarangkan dalam komentar beberapa baris.

// This is a single line comment

integer a; // Creates an int variable called a, and treats everything to the right of // as a comment

/*

This is a

multiple-line or

block comment

*/

/* This is /*

an invalid nested

block comment */

*/

/* However,

// this one is okay

*/

// This is also okay

///////////// Still okay

Spasi putih adalah istilah yang digunakan untuk mewakili karakter spasi, tab, baris baru, dan umpan formulir, dan biasanya diabaikan oleh Verilog kecuali jika memisahkan token. Sebenarnya, ini membantu dalam lekukan kode agar lebih mudah dibaca.

module dut; // 'module' is a keyword,

// 'dut' is an identifier

reg [8*6:1] name = "Hello!"; // The 2 spaces in the beginning are ignored

Namun kosong (spasi) dan tab (dari kunci TAB) tidak diabaikan dalam string. Pada contoh di bawah, string variabel yang disebut addr mendapat nilai "Bumi " karena pelestarian ruang dalam string.

// There is no space in the beginning of this line, // but there's a space in the string reg [8*6:1] addr = "Earth "; endmodule

Ada tiga jenis operator:unary , biner , dan terner atau bersyarat .

x = ~y; // ~ is a unary operator, and y is the operand

x = y | z; // | is a binary operator, where y and z are its operands

x = (y > 5) ? w : z; // ?: is a ternary operator, and the expression (y>5), w and z are its operands

Jika ekspresi (y> 5) benar, maka variabel x akan mendapatkan nilai dalam w , jika tidak, nilai dalam z .

Kami paling akrab dengan angka yang direpresentasikan sebagai desimal. Namun, angka juga dapat direpresentasikan dalam biner , oktal dan heksadesimal . Secara default, simulator Verilog memperlakukan angka sebagai desimal. Untuk mewakili mereka dalam radix yang berbeda , aturan tertentu harus diikuti.

16 // Number 16 in decimal 0x10 // Number 16 in hexadecimal 10000 // Number 16 in binary 20 // Number 16 in octal

Nomor berukuran diwakili seperti yang ditunjukkan di bawah ini, di mana ukuran ditulis hanya dalam desimal untuk menentukan jumlah bit dalam nomor tersebut.

[size]'[base_format][number]

3'b010; // size is 3, base format is binary ('b), and the number is 010 (indicates value 2 in binary)

3'd2; // size is 3, base format is decimal ('d) and the number is 2 (specified in decimals)

8'h70; // size is 8, base format is hexadecimal ('h) and the number is 0x70 (in hex) to represent decimal 112

9'h1FA; // size is 9, base format is hexadecimal ('h) and the number is 0x1FA (in hex) to represent decimal 506

4'hA = 4'd10 = 4'b1010 = 4'o12 // Decimal 10 can be represented in any of the four formats

8'd234 = 8'D234 // Legal to use either lower case or upper case for base format

32'hFACE_47B2; // Underscore (_) can be used to separate 16 bit numbers for readability

Huruf besar legal untuk spesifikasi angka ketika format dasarnya adalah heksadesimal.

16'hcafe; // lowercase letters Valid 16'hCAFE; // uppercase letters Valid 32'h1D40_CAFE; // underscore can be used as separator between 4 letters Valid

Angka tanpa format_dasar spesifikasi adalah angka desimal secara default . Angka tanpa ukuran spesifikasi memiliki jumlah bit default tergantung pada jenis simulator dan mesin.

integer a = 5423; // base format is not specified, a gets a decimal value of 5423

integer a = 'h1AD7; // size is not specified, because a is int (32 bits) value stored in a = 32'h0000_1AD7

Angka negatif ditentukan dengan menempatkan minus - tanda sebelum ukuran angka. Adalah ilegal untuk memiliki tanda minus di antara base_format dan nomor .

-6'd3; // 8-bit negative number stored as two's complement of 3 -6'sd9; // For signed maths 8'd-4; // Illegal

Urutan karakter yang diapit tanda kutip ganda " " disebut string. Itu tidak dapat dipecah menjadi beberapa baris dan setiap karakter dalam string membutuhkan 1 byte untuk disimpan.

"Hello World!" // String with 12 characters -> require 12 bytes "x + z" // String with 5 characters "How are you feeling today ?" // Illegal for a string to be split into multiple lines

Identifier adalah nama-nama variabel sehingga mereka dapat direferensikan nanti. Mereka terdiri dari karakter alfanumerik [a-z][A-Z][0-9] , menggarisbawahi _ atau tanda dolar $ dan peka huruf besar/kecil. Mereka tidak dapat memulai dengan angka atau tanda dolar.

integer var_a; // Identifier contains alphabets and underscore -> Valid integer $var_a; // Identifier starts with $ -> Invalid integer v$ar_a; // Identifier contains alphabets and $ -> Valid integer 2var; // Identifier starts with a digit -> Invalid integer var23_g; // Identifier contains alphanumeric characters and underscore -> Valid integer 23; // Identifier contains only numbers -> Invalid

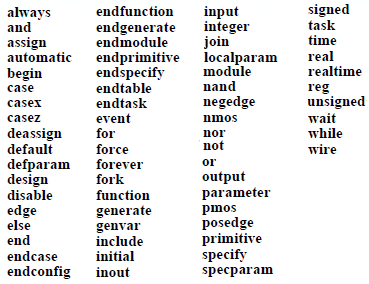

Kata kunci adalah pengidentifikasi khusus yang disediakan untuk mendefinisikan konstruksi bahasa dan dalam huruf kecil. Daftar kata kunci penting diberikan di bawah ini.

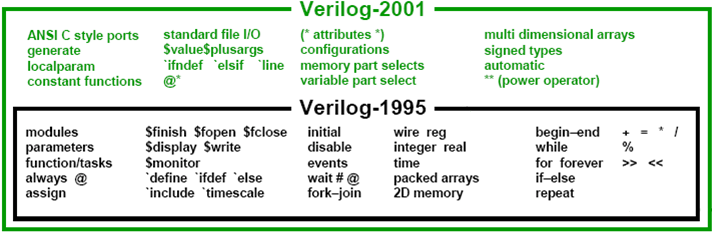

Verilog telah mengalami beberapa revisi selama bertahun-tahun dan lebih banyak penambahan telah dilakukan dari tahun 1995 hingga 2001 yang ditunjukkan di bawah ini.

Verilog

case pernyataan memeriksa apakah ekspresi yang diberikan cocok dengan salah satu ekspresi lain dalam daftar dan bercabang sesuai. Biasanya digunakan untuk mengimplementasikan multiplexer. Konstruksi if-else mungkin tidak cocok jika ada banyak kondisi yang harus diperiksa dan akan disintesis menjadi

Parameter adalah konstruksi Verilog yang memungkinkan modul untuk digunakan kembali dengan spesifikasi yang berbeda. Misalnya, penambah 4-bit dapat diparameterisasi untuk menerima nilai jumlah bit dan nilai parameter baru dapat diteruskan selama pembuatan modul. Jadi, penambah N-bit bisa menjadi pen

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan? Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang

Desain module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; else