Verilog

Simulasi Verilog tergantung pada bagaimana waktu didefinisikan karena simulator perlu mengetahui apa arti #1 dalam hal waktu. `timescale direktif compiler menentukan unit waktu dan presisi untuk modul yang mengikutinya.

`timescale <time_unit>/<time_precision>

// Example

`timescale 1ns/1ps

`timescale 10us/100ns

`timescale 10ns/1ns

unit_waktu adalah pengukuran penundaan dan waktu simulasi sedangkan time_precision menentukan bagaimana nilai penundaan dibulatkan sebelum digunakan dalam simulasi.

Gunakan konstruksi skala waktu berikut untuk menggunakan unit waktu yang berbeda dalam desain yang sama. Ingatlah bahwa spesifikasi penundaan dalam desain tidak dapat disintesis dan tidak dapat dikonversi ke logika perangkat keras.

`timescale untuk satuan dasar pengukuran dan ketepatan waktu$time dan $realtime fungsi sistem mengembalikan waktu saat ini dan format pelaporan default dapat diubah dengan tugas sistem lain $timeformat .Bilangan bulat dalam spesifikasi ini dapat berupa 1, 10 atau 100 dan string karakter yang menentukan unit dapat mengambil nilai apa pun yang disebutkan dalam tabel di atas.

// Declare the timescale where time_unit is 1ns

// and time_precision is also 1ns

`timescale 1ns/1ns

module tb;

// To understand the effect of timescale, let us

// drive a signal with some values after some delay

reg val;

initial begin

// Initialize the signal to 0 at time 0 units

val <= 0;

// Advance by 1 time unit, display a message and toggle val

#1 $display ("T=%0t At time #1", $realtime);

val <= 1;

// Advance by 0.49 time unit and toggle val

#0.49 $display ("T=%0t At time #0.49", $realtime);

val <= 0;

// Advance by 0.50 time unit and toggle val

#0.50 $display ("T=%0t At time #0.50", $realtime);

val <= 1;

// Advance by 0.51 time unit and toggle val

#0.51 $display ("T=%0t At time #0.51", $realtime);

val <= 0;

// Let simulation run for another 5 time units and exit

#5 $display ("T=%0t End of simulation", $realtime);

end

endmodule

Pernyataan penundaan pertama menggunakan #1 yang membuat simulator menunggu tepat 1 unit waktu yang ditentukan menjadi 1ns dengan `timescale pengarahan. Pernyataan penundaan edetik menggunakan 0,49 yang kurang dari setengah unit waktu. Namun presisi waktu ditentukan menjadi 1ns dan karenanya simulator tidak boleh lebih kecil dari 1ns yang membuatnya membulatkan pernyataan penundaan yang diberikan dan menghasilkan 0ns. Jadi penundaan kedua gagal untuk memajukan waktu simulasi.

Pernyataan penundaan ketiga menggunakan tepat setengah unit waktu [hl]#0.5[/lh] dan sekali lagi simulator akan membulatkan nilai untuk mendapatkan #1 yang mewakili satu unit waktu penuh. Jadi ini akan dicetak pada T=2ns.

Pernyataan penundaan keempat menggunakan nilai lebih dari setengah satuan waktu dan dibulatkan serta membuat pernyataan tampilan dicetak pada T=3ns.

Log Simulasincsim> run T=1 At time #1 T=1 At time #0.49 T=2 At time #0.50 T=3 At time #0.51 T=8 End of simulation ncsim: *W,RNQUIE: Simulation is complete.

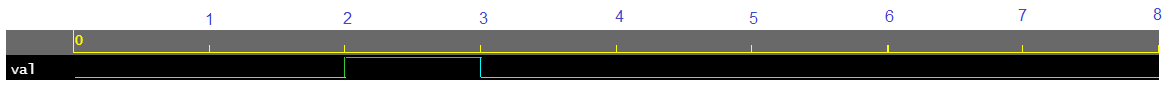

Simulasi berjalan selama 8ns seperti yang diharapkan, tetapi perhatikan bahwa bentuk gelombang tidak memiliki pembagian yang lebih kecil antara setiap nanodetik. Ini karena ketepatan waktu sama dengan satuan waktu.

hanya perubahan yang dibuat dalam contoh ini dibandingkan dengan yang sebelumnya adalah bahwa skala waktu telah diubah dari 1ns/1ns menjadi 10ns/1ns. Jadi satuan waktunya adalah 10 ns dan presisi adalah 1 ns.

// Declare the timescale where time_unit is 10ns

// and time_precision is 1ns

`timescale 10ns/1ns

// NOTE: Testbench is the same as in previous example

module tb;

// To understand the effect of timescale, let us

// drive a signal with some values after some delay

reg val;

initial begin

// Initialize the signal to 0 at time 0 units

val <= 0;

// Advance by 1 time unit, display a message and toggle val

#1 $display ("T=%0t At time #1", $realtime);

val <= 1;

// Advance by 0.49 time unit and toggle val

#0.49 $display ("T=%0t At time #0.49", $realtime);

val <= 0;

// Advance by 0.50 time unit and toggle val

#0.50 $display ("T=%0t At time #0.50", $realtime);

val <= 1;

// Advance by 0.51 time unit and toggle val

#0.51 $display ("T=%0t At time #0.51", $realtime);

val <= 0;

// Let simulation run for another 5 time units and exit

#5 $display ("T=%0t End of simulation", $realtime);

end

endmodule

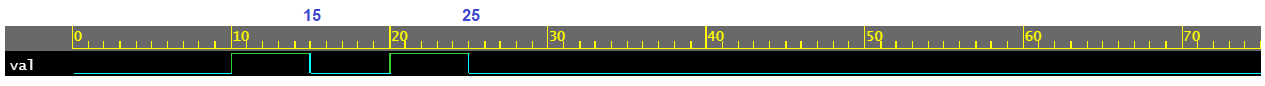

Waktu simulasi sebenarnya diperoleh dengan mengalikan penundaan yang ditentukan menggunakan # dengan satuan waktu dan kemudian dibulatkan berdasarkan presisi. Pernyataan penundaan pertama kemudian akan menghasilkan 10ns dan yang kedua memberikan 14,9 yang dibulatkan menjadi 15ns.

Pernyataan ketiga juga menambahkan 5ns (0,5 * 10ns) dan total waktu menjadi 20ns. Yang keempat menambahkan 5ns lagi (0,51 * 10) untuk memajukan total waktu menjadi 25ns.

Log Simulasincsim> run T=10 At time #1 T=15 At time #0.49 T=20 At time #0.50 T=25 At time #0.51 T=75 End of simulation ncsim: *W,RNQUIE: Simulation is complete.

Perhatikan bahwa satuan dasar dalam bentuk gelombang adalah dalam puluhan nanodetik dengan presisi 1ns.

hanya perubahan yang dibuat dalam contoh ini dibandingkan dengan yang sebelumnya adalah bahwa skala waktu telah diubah dari 1ns/1ns menjadi 1ns/1ps. Jadi satuan waktunya adalah 1 dtk dan presisi adalah 1 ps.

// Declare the timescale where time_unit is 1ns

// and time_precision is 1ps

`timescale 1ns/1ps

// NOTE: Testbench is the same as in previous example

module tb;

// To understand the effect of timescale, let us

// drive a signal with some values after some delay

reg val;

initial begin

// Initialize the signal to 0 at time 0 units

val <= 0;

// Advance by 1 time unit, display a message and toggle val

#1 $display ("T=%0t At time #1", $realtime);

val <= 1;

// Advance by 0.49 time unit and toggle val

#0.49 $display ("T=%0t At time #0.49", $realtime);

val <= 0;

// Advance by 0.50 time unit and toggle val

#0.50 $display ("T=%0t At time #0.50", $realtime);

val <= 1;

// Advance by 0.51 time unit and toggle val

#0.51 $display ("T=%0t At time #0.51", $realtime);

val <= 0;

// Let simulation run for another 5 time units and exit

#5 $display ("T=%0t End of simulation", $realtime);

end

endmodule

Lihat bahwa unit waktu diskalakan agar sesuai dengan nilai presisi baru 1 ps. Perhatikan juga bahwa waktu direpresentasikan dalam resolusi terkecil yang dalam hal ini adalah picoseconds.

Log Simulasincsim> run T=1000 At time #1 T=1490 At time #0.49 T=1990 At time #0.50 T=2500 At time #0.51 T=7500 End of simulation ncsim: *W,RNQUIE: Simulation is complete.

Verilog

Sebuah for loop adalah loop yang paling banyak digunakan dalam perangkat lunak, tetapi terutama digunakan untuk mereplikasi logika perangkat keras di Verilog. Ide di balik for loop adalah untuk mengulangi satu set pernyataan yang diberikan dalam loop selama kondisi yang diberikan benar. Ini sangat m

case pernyataan memeriksa apakah ekspresi yang diberikan cocok dengan salah satu ekspresi lain dalam daftar dan bercabang sesuai. Biasanya digunakan untuk mengimplementasikan multiplexer. Konstruksi if-else mungkin tidak cocok jika ada banyak kondisi yang harus diperiksa dan akan disintesis menjadi

Parameter adalah konstruksi Verilog yang memungkinkan modul untuk digunakan kembali dengan spesifikasi yang berbeda. Misalnya, penambah 4-bit dapat diparameterisasi untuk menerima nilai jumlah bit dan nilai parameter baru dapat diteruskan selama pembuatan modul. Jadi, penambah N-bit bisa menjadi pen

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan? Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang